.png) STMCU小助手

发布时间:2022-7-12 23:18

STMCU小助手

发布时间:2022-7-12 23:18

|

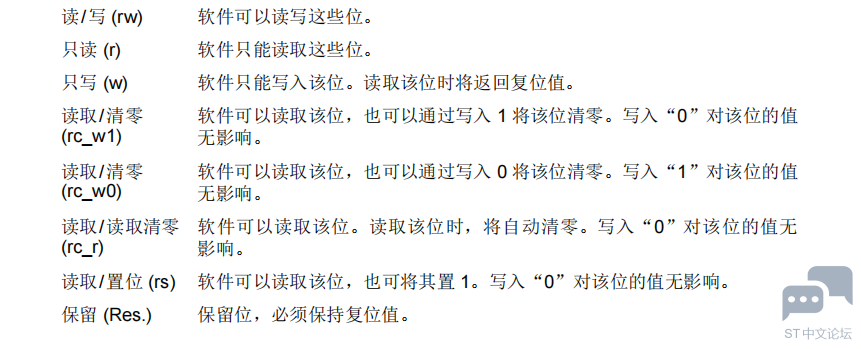

前言 本参考手册面向应用开发人员,提供有关使用 STM32L0x3 微控制器存储器与外设的完整信息。 STM32L0x3 构成一个微控制器系列,各产品具有不同的存储器大小、封装和外设。 有关订购信息以及器件的机械与电气特性,请参见相应的数据手册。 有关 ARM® Cortex®-M0+ 内核的信息,请参见Cortex®-M0+技术参考手册。 1 文档约定 1.1 寄存器相关缩写词列表 寄存器说明中使用以下缩写词:

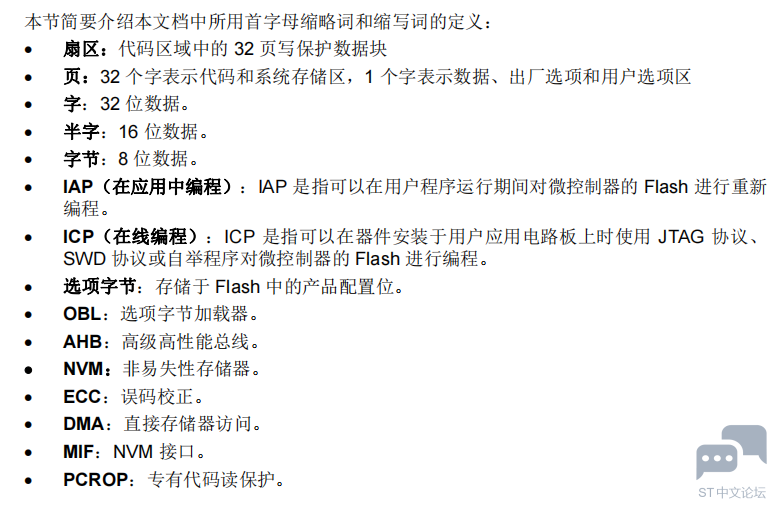

1.2 词汇表 本节简要介绍本文档中所用首字母缩略词和缩写词的定义:

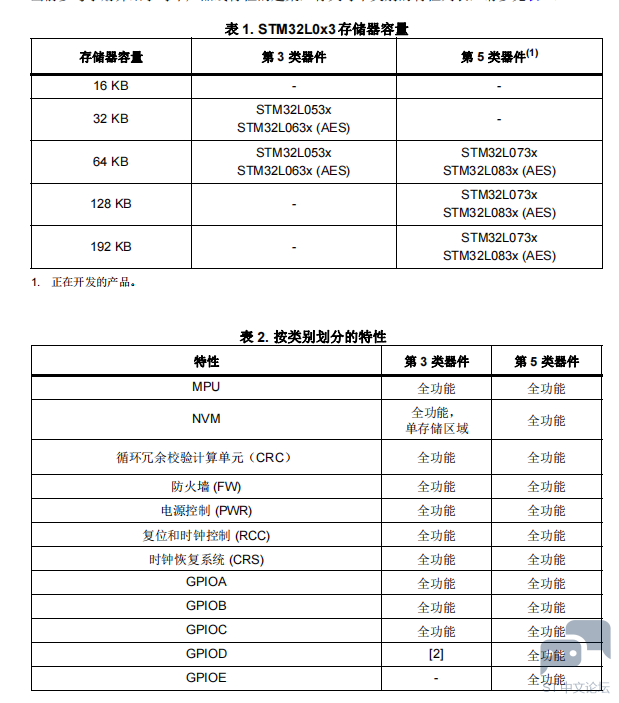

1.3 外设可用性 有关各型号产品的外设可用性及数量信息,请参见特殊器件数据手册。 1.4 产品类别定义 表 1 概括介绍了存储器容量和产品线。 当前参考手册介绍了每个产品线特性的超集,有关每个类别的特性列表,请参见表 2。

![9P7{VY~KLWE@OP88]K5FQ$H.png 9P7{VY~KLWE@OP88]K5FQ$H.png](data/attachment/forum/202207/12/231916qissgc8fyhypyf83.png)

![D`_N123G05`%@]BN6G{(CIQ.png D`_N123G05`%@]BN6G{(CIQ.png](data/attachment/forum/202207/12/231916w5qqcg9c9mp5e2qi.png)

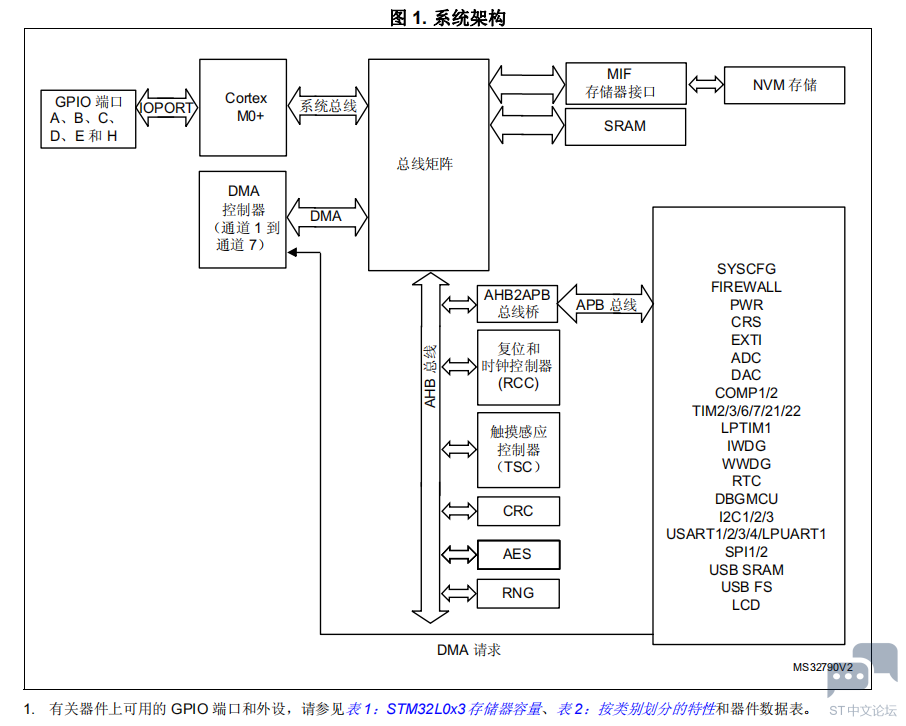

2 系统和存储器概述 2.1 系统架构 主系统包括: 两个主器件: – Cortex®-M0+内核(AHB-lite 总线) – GP-DMA,通用微控制器 三个从器件: – 内部 SRAM – 内部非易失性存储器 – AHB到APB,连接所有APB外设 这些外设使用多层 AHB 总线架构互连,如图 1 所示。

2.1.1 S0:Cortex® 总线 此总线用于将 Cortex®-M0+ 内核的 DCode/ICode 总线连接到总线矩阵。内核会使用此总线获取指令、获取数据以及访问 AHB/APB 资源。 2.1.2 S1:DMA 总线 此总线用于将 DMA 的 AHB 主接口连接到总线矩阵,而总线矩阵管理着不同主器件对 Flash和 EEPPROM、SRAM 以及 AHB/APB 外设的访问。 2.1.3 总线矩阵 总线矩阵用于主控总线之间的访问仲裁管理。仲裁采用循环调度算法。总线矩阵由两个主器件(CPU、DMA)和三个从器件(NVM 接口、SRAM、AHB2APB1/2 总线桥)构成。 AHB/APB 总线桥 AHB/APB 总线桥可在 AHB 与 2 条 APB 总线之间实现完全同步的连接。APB1 和 APB2 的最大工作频率高达 32 MHz。 有关连接到此总线桥的外设的地址映射,请参见第 57 页的第 2.2.2节:存储器映射和寄存器边界地址。 每次芯片复位后,所有外设时钟都被关闭(SRAM 和 MIF 除外)。使用外设前,必须在RCC_AHBENR、RCC_APB2ENR、RCC_APB1ENR 或 RCC_IOPENR 寄存器中使能其时钟。 注: 对 APB 寄存器执行 16 位或 8 位访问时,该访问将转换为 32 位访问:总线桥将 16 位或 8 位数据复制后提供给 32 位向量。 2.2 存储器组织结构 2.2.1 简介 程序存储器、数据存储器、寄存器和 I/O 端口排列在同一个线性(即地址连续)的 4 GB 地址空间内。 各字节按小端格式在存储器中编码。字中编号最低的字节被视为该字的最低有效字节,而编号最高的字节被视为最高有效字节。 可寻址的存储空间分为 8 个主要块,每个块为 512 MB。 ![HD]MXU}_R1XTJJ_UNKZ_`UF.png HD]MXU}_R1XTJJ_UNKZ_`UF.png](data/attachment/forum/202207/12/231915uh9l3kllr90nkrhn.png)

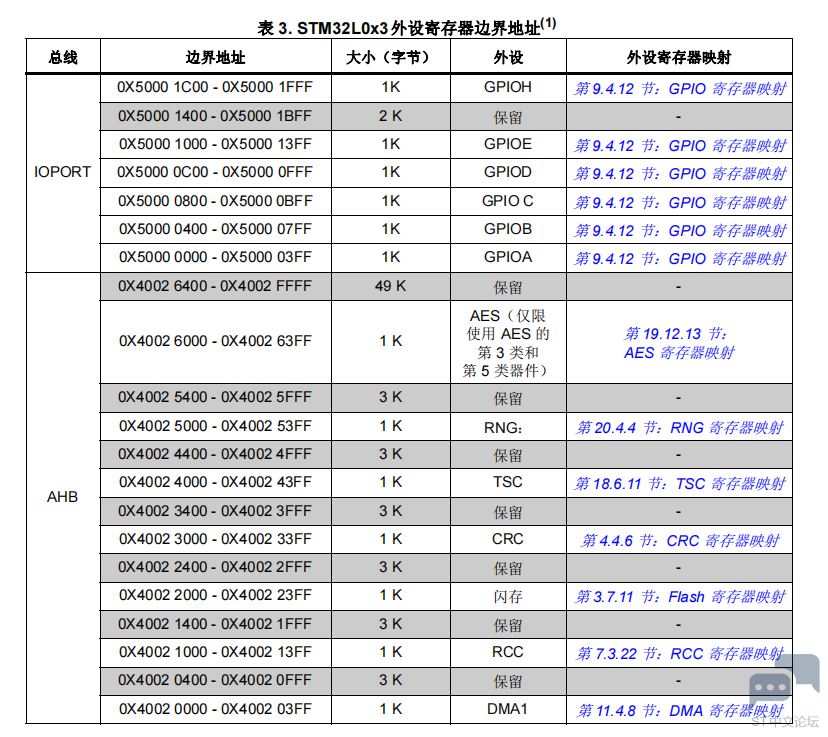

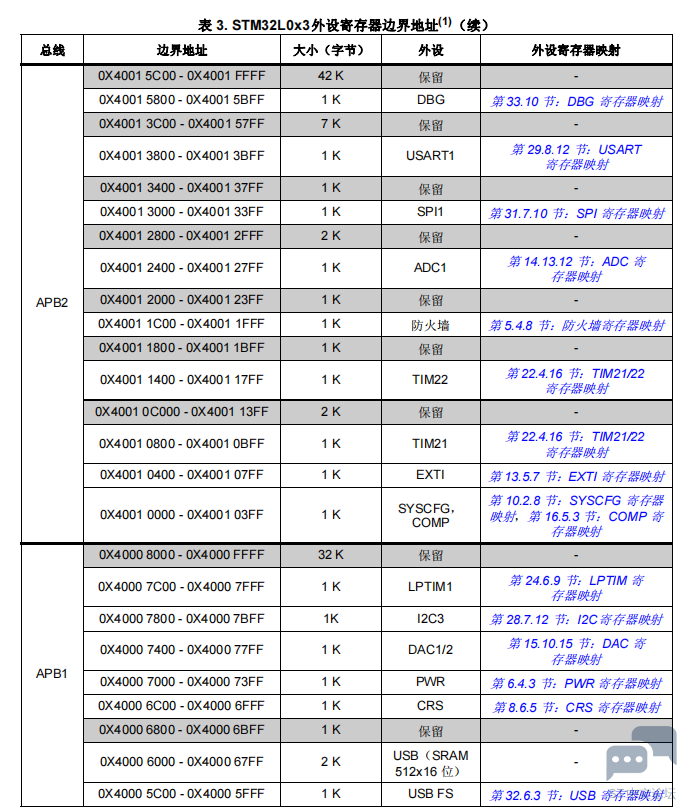

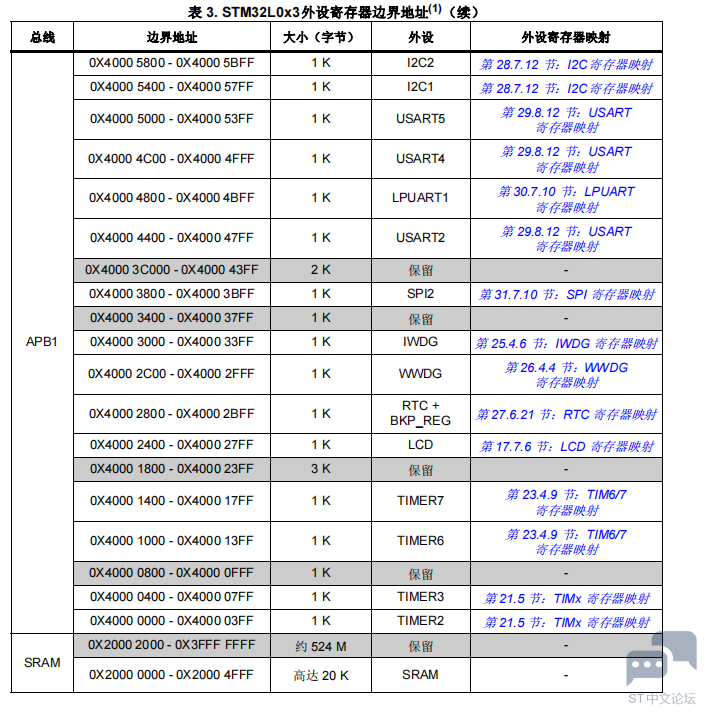

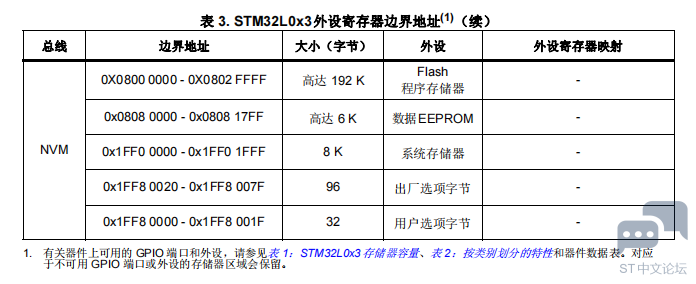

未分配给片上存储器和外设的所有存储区域均视为“保留区”。有关可用存储器和寄存器区域的详细映射,请参见存储器映射和寄存器边界地址和外设章节。 2.2.2 存储器映射和寄存器边界地址 有关综合存储器映射图,请参见相应器件的数据手册。 下表给出了器件中可用外设的边界地址。

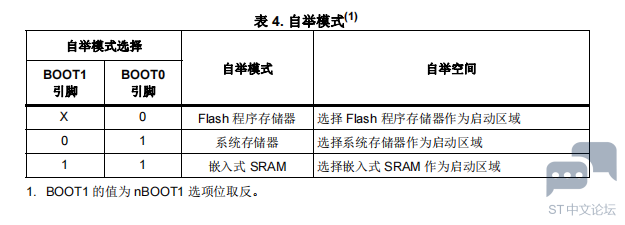

2.3 嵌入式 SRAM STM32L0x3器件的静态 SRAM 高达 20 KB。 此 RAM 可按字节、半字(16 位)或全字(32 位)访问。此存储器可以最大系统时钟频率进行寻址,无等待状态,因此可由 CPU 和 DMA 访问。 SRAM 起始地址为 0x2000 0000。 若通过启动引脚或 MEM_MODE 选择物理重映射,CPU 可从地址 0x0000 0000 访问 SRAM(参见第 10.2.1 节:SYSCFG 存储器重映射寄存器 (SYSCFG_CFGR1))。 2.4 自举配置 在 STM32L0x3 中,可通过 BOOT0 引脚以及用户选项字节中的启动配置位选择三种不同的启动模式,如下表所示。

复位后,在 SYSCLK 的第四个上升沿锁存启动模式配置。用户可以通过设置 nBOOT1 和BOOT0 引脚来选择需要的启动模式。 退出待机模式后,还可以对启动模式配置进行重新采样。因此不得在待机模式下修改启动模式配置。该启动延迟结束后,CPU 将从地址 0x0000 0000 获取栈顶值,然后从始于 0x00000004 的启动存储器开始执行代码。 根据所选的启动模式,Flash 程序存储器、系统存储器或 SRAM 可通过以下方式进行访问: 从 Flash 程序存储器启动:Flash 程序存储器在启动存储空间 (0x0000 0000) 中有别名,但也可从它原来的存储空间 (0x0800 0000) 访问。换句话说,Flash 存储器内容可从地址 0x0000 0000 或 0x0800 0000 开始访问。 从系统存储器启动:系统存储器在启动存储空间 (0x0000 0000) 中有别名,但也可从它原来的存储空间 (0x1FF0 0000) 访问。 从嵌入式 SRAM 启动:SRAM 在启动存储空间 (0x0000 0000) 中有别名,但也可从它原来的存储空间 (0x2000 0000) 访问。 存储区交换(仅限第 5 类器件) 对于具有两个存储区的器件,存储区交换机制允许 CPU 指向启动存储空间 (0x00000000) 中的存储区 1 或存储区 2。Flash 程序和数据 EEPROM 地址会更改(参见表 8:UFB = 0 时的 NVM 构成(128 KB 第 5 类器件)、表 10:UFB = 0 时的 NVM 构成(64 KB第 5 类器件))。 物理重映射 选择了启动引脚和启动位后,应用程序软件可修改代码区域中可访问的存储器。这种修改是通过对 SYSCFG 存储器重映射寄存器 (SYSCFG_CFGR1) 中的 MEM_MODE 位进行编程实现的。 内部自举程序 嵌入式启动加载器位于系统存储器中,由 ST 在生产阶段编程。它用于通过以下串行接口重 新编程 Flash: 对于第 3 类器件:USART1、USART2、SPI1 或 SPI2。 对于配有 USB 接口的第 5 类器件:USART1、USART2 或 USB。 对于没有 USB 接口的第 5 类器件:USART1、USART2、SPI1、SPI2、I2C1 或 I2C2。 关于启动加载器串行接口对应的 I/O 的详细信息,请参见器件数据表。 更多关于 STM32 启动加载器的详细信息,请参见 AN2606。 完整版请查看:附件 |

DM00095744_ZHV4.pdf

下载11.59 MB, 下载次数: 27

微信公众号

微信公众号

手机版

手机版