.png) STMCU小助手

发布时间:2022-7-19 16:00

STMCU小助手

发布时间:2022-7-19 16:00

|

前言 嵌入式设备中对类似于智能手机的高级图形用户界面的需求不断增长,为嵌入式系统设计者带来了极大挑战。到目前为止,SPI、并口和RGB接口已被广泛应用于在MCU和显示屏之间建立连接。 由于对分辨率和刷新频率的要求越来越高,需要更多数量的引脚(对于16.7M色彩显示屏,最多为28个引脚)和更高的像素时钟频率。这些需求提高了对MCU侧的引脚数量要求和总体PCB复杂性和成本,这要归因于板尺寸、路由复杂性和时钟与数据之间的偏差问题。 为了解决这些挑战,意法半导体在市场上第一个提供了带有MIPI DSI主机的MCU产品(参见表 1)。这些新的具有DSI主机的STM32产品实现了一种更有效的连接到显示屏的方法。 MIPI-DSI是一种高速、引脚数量少的串行接口,用于原本针对移动产业的显示屏。由于在移动手机和平板电脑中的广泛应用,DSI接口越来越普及,这推动了DSI显示屏成本的下降,并使之对其他消费市场产生了吸引力。 STM32 MIPI-DSI主机大幅减少了设备的引脚数量,可与如今市场上随处可见的DSI显示屏实现轻松连接。得益于它的引脚数量少和低功耗特性,DSI主机是连接显示屏的最有效方式,特别是对于有严格的尺寸和功耗限制的设备,例如可穿戴设备。 本应用笔记描述了STM32F4系列和STM32F7系列微控制器的DSI主机接口,重点展示了DSI主机的不同操作模式,并提供了根据应用需要选择最佳工作模式的指南。还提供了关于如何根据操作模式配置DSI主机的实例。 相关文档 本应用笔记必须同以下文档(在www.st.com上获取)一起阅读: • STM32F76xxx和STM32F77xxx基于32位MCU(RM0410)的高级ARM® • STM32F469xx和STM32F479xx基于32位MCU(RM0386)的高级ARM® • 相关的STM32F469/479、STM32F7x8和STM32F7x9数据手册

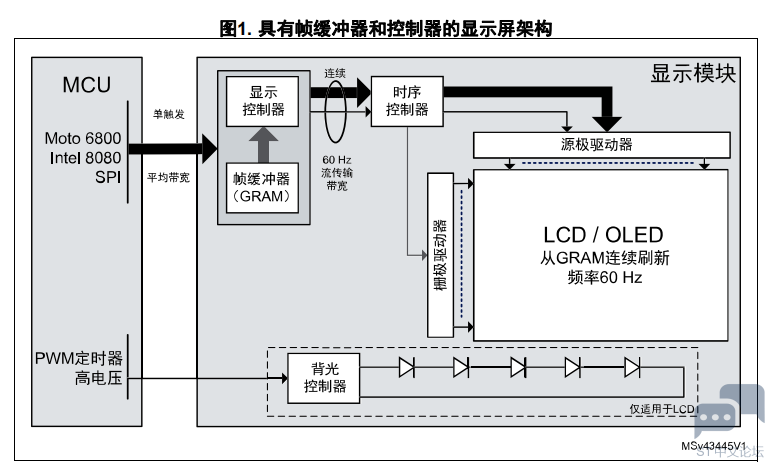

1 标准和参考文献 本章列出了本文档中使用的标准和参考文献。 • MIPI®联盟显示串行接口(DSI)规范 v1.1 - 2011年11月22日 • MIPI®联盟显示总线接口(DBI-2)规范 v2.00 - 2005年11月16日 • MIPI®联盟显示指令集(DCS)规范 v1.1 - 2011年11月22日 • MIPI®联盟显示像素接口(DPI-2)规范 v2.00 - 2005年9月15日 • MIPI®联盟立体显示格式(SDF)规范 v1.0 - 2011年11月22日 • MIPI®联盟D-PHY规范 v1.1 - 2011年11月7日 2 概述 显示屏串行接口(DSI)是由MIPI(移动产业处理器接口)联盟定义的高速串行协议,提供显示模块与主机处理器之间的连接。 STM32是市场上首款具有集成DSI主机的MCU产品(参见表 1获取适用产品列表)。STM32 DSI主机提供高度集成的解决方案,这要得益于它的内部MIPI D-PHY、专用PLL和1.2 V调节器。 DSI主机提供速度高达1 Gb/s的高速通信接口。DSI主机允许微控制器使用更少的引脚与显示屏连接,无需外部电桥。DSI接口完全可配置,可与目前市售的DSI兼容显示屏实现轻松连接。 应用可受益于DSI主机支持的轻松连接和更少引脚数,降低了PCB复杂性和系统总成本。 DSI主机与LCD-TFT显示控制器(LTDC)深度集成,用于简化应用开发和移植。 STM32 DSI主机提供可扩展的架构。根据带宽要求,用户可以选择一个或两个数据通道。 2.1 显示屏连接 根据显示屏是否具有内部控制器和帧缓冲器,可将显示屏分为两类: • 显示模块具有显示控制器和帧缓冲器:它们集成了图形RAM(GRAM),用于存储要显示的帧,并具有控制刷新操作的显示控制器。 MCU使用一组指令更新显示屏的帧缓冲器内容。 显示屏依赖其内部控制器和帧缓冲器来执行刷新操作,无需MCU的干预。 • 显示模块无显示控制器和帧缓冲器:这些显示屏依赖于MCU发送数据和视频时序信息的实时像素流,以便刷新显示。 这些不同类型的显示屏采用不同类型的显示接口: • 至有控制器和帧缓冲器的显示模块的接口: – SPI接口:使用的引脚很少(最多6个引脚),但速度很慢且不适合动画。 – 并行接口:使用并行总线发送指令和数据,因此拥有的带宽高于SPI接口。 常见的并行接口有Motorola 6800总线和Intel 8080总线。并行接口需要最多22个引脚(16个数据信号和6个控制信号)。 显示控制器和GRAM帧缓冲器位于显示侧。MCU发送更新显示屏GRAM的指令。更新将一次完成。 图 1显示的是集成了帧缓冲器和显示控制器的显示屏架构及其相应的接口方案:

• 至没有显示控制器和帧缓冲器的显示模块的接口: – RGB接口:MCU提供像素数据和视频时序信号。RGB接口具有很好的实时性能,但要求MCU侧具有高带宽,用于对显示屏的馈送。它还需要最多28个引脚:24 RGB数据(R[0:7]G[0:7]B[0:7])和四个同步信号(PCLK、HSYNC、VSYNC、DATAEN)。 MCU持续生成像素数据和视频控制信号来驱动显示屏。帧缓冲器位于MCU侧。 图 2显示了没有帧缓冲器和显示控制器的显示屏的典型架构: ![4VY34%BG55W4SNG]K8LU0US.png 4VY34%BG55W4SNG]K8LU0US.png](data/attachment/forum/202207/18/165427ty072f000aa206at.png)

2.2 MIPI显示屏规格标准 MIPI显示屏工作组规定了主机处理器与显示屏之间的互联。 该工作组定义了一组规范,目的是实现现有协议寻址显示的标准化: • 显示总线接口(DBI)涵盖了有显示控制器和帧缓冲器的协议寻址显示模块。它定义了三种接口类型: – A类,支持并行Motorola 6800总线。 – B类,支持并行Intel 8080总线。 – C类,支持SPI接口。 • 显示指令集(DCS)规定了适用于支持MIPI-DBI接口的显示屏的指令。 • 显示像素接口(DPI)支持针对没有控制器和帧缓冲器的显示屏的RGB接口。 为了以更好的方式驱动现代显示屏,MIPI显示屏工作组开发了新的协议。 为了减少MCU和显示屏之间的连线数量,MIPI显示屏工作组定义了DSI。 DSI封装了DBI指令(称为指令模式)或DPI信号(称为视频模式),并将它们以信号的形式传输至显示屏。这允许只使用四个或六个引脚来连接标准显示屏,并获得与DPI相同的性能。 DSI可通过单一接口支持所有可能的显示屏架构(有或没有显示控制器和帧缓冲器)。 完整版请查看:附件 |

DM00287601_ZHV1.pdf

下载14.66 MB, 下载次数: 50

SPI 高温读错最后一位?STM32F42xx 官方根治方案

STM32F745 USART1 Bootloader启动失败排查与解决的流程分析

STM32CubeIDE for Visual Studio Code 开发流水帐

STM32的RTC电流消耗异常问题分析

STM32与51单片机差异一文速览

STM32大神笔记,超详细单片机学习汇总资料

STM32芯片命名规则

STM32 引脚到底有多少?为什么一个引脚能当好几个用?

STM32F429I-Disco官方提供的裸机BSP

入门嵌入式,为什么STM32是“优选起步”?

微信公众号

微信公众号

手机版

手机版