.png) STMCU小助手

发布时间:2022-8-11 19:15

STMCU小助手

发布时间:2022-8-11 19:15

|

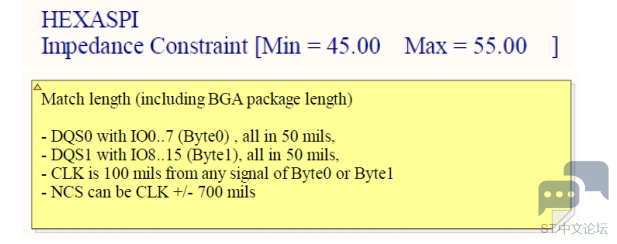

1. 引言 本文介绍在使用 STM32U5 的 HexaSPI(HSPI)总线连接 PSRAM 外设时,做 PCB 布线上需要注意的一些技术要求. 2. HexaSPI 总线连接 PSRAM 的布线规则 HexaSPI(HSPI)总线接口是在 STM32U5 系列 MCU 中新增加的外设,它可以连接到PSRAM, OSPI FLASH 的外部设备来扩展系统内存, 其运行速度可以达到 160MHz@1.8V ,或 133MHz@3.3V. 我们下面将讨论当 U5 的 HSPI 总线与 AMMEMORY 公司的 APS256XXN-OBR-BG 相连时,对 PCB 布线的一些技术要求. 2.1. STM32U5 参考板上 HSPI 总线的布线规则 在 STM32U5 的 DISCOVERY 参考板 MB1662 的原理图上, 可以看到 HSPI 总线的布线要求是 :

可以看到, DISCOVERY 板的参考设计布线中, 对 HSPI 总线的布线的走线阻抗和总线的信号等长控制都提出了较严格的要求. 条件允许的情况下按照这些要求进行 PCB 布线而得到的电路板在运行中肯定是没有问题的. 但是在 U5 的某些实际应用中, 比如智能手表, 由于 PCB 尺寸非常小, 以及 PCB 层数的限制, 有时要想做到对 HSPI 总线的阻抗控制或者等长控制是非常困难甚至是不可能的.在这种情况下, 如何布线才是安全的呢 ? 2.2. HSPI 总线的等长要求 对于速度 160MHz 的 HSPI 信号来说, 其时钟周期为 1/160MHZ 也就是 6.25ns, 在扣除了足够的建立/保持时间, 以及扣除以及一些必要的时间用来弥补总线 IO 的输入输出偏差等情况后, 保守一些, 可以认为至少有 3%周期的时间可以用来应对因 PCB 走线不等长而导致的信号延迟. 时钟周期的 3%也就是 6.25ns*3%= 187.5ps. 假设使用的是 FR4 的 PCB, 信号在 PCB 上的速度是 6mil/ps (实际的信号速度取决于 PCB 材质, 信号所在的 PCB 层等,请咨询实际使用的 PCB 供应商), 那么 HSPI 总线所允许的长度偏差就是 187.5ps*6mil/ps=1125mil =28.5mm 很显然, 这个总线等长要求相对于 MB1662 的+/-50mil 的要求大大放宽了, 基本上, 在智能手表类 PCB 尺寸有限的应用中, 即使不特意做等长处理, HSPI 总线的等长差异仍然能够保持在上述的安全范围内. 2.3. HSPI 总线信号的阻抗控制 通常来说, 为了保证信号的完整性, 对 HSPI 总线信号进行阻抗控制是必要的. 但是, 在一些层数有限的 PCB 系统中, 是不可能为 HSPI 总线提供参考平面进行阻抗控制的. 而且我们知道, 当信号足够短的时候, 就不需要进行阻抗控制. 那么, 具体要多短呢 ? 我们知道, 阻抗控制是对 PCB 高速信号传输线的要求, 而传输线的一般定义是当信号在该段走线上的延迟达到了其上升沿时间的 1/6 左右时, 就可以认为这段走线是传输线. 因此, 我们只要把 HSPI 总线的信号延迟控制在上升沿时间的 1/6 范围内, 就不需要进行阻抗控制. HSPI 总线的上升沿时间大约 900ps 左右, 1/6 就是 150ps, 因此, 如果无法进行阻抗控制, HSPI 的总线长度应该控制在 6mil/ps *150ps = 900mil = 22.9mm 的长度范围内. 完整版请查看:附件 |

LAT1034 STM32U5 HexaSPI总线到PSRAM的PCB布线规则_v1.0.pdf

下载284.4 KB, 下载次数: 1

STM32U5低功耗测试

STM32怎么选型

内存配置的艺术:STM32为嵌入式系统高端UI优化RAM和闪存的三大策略

【STM32U545】实现CAN数据收发

【我的STM32U5 项目秀】+04-MPU6050在STM32U5上的移植

实战经验 | 基于 STM32U5 创建 USBx_CustomHID 通信

STM32U5 x E-BIKE,记录你的骑行多巴胺

基于STM32U5系列TIMER+DMA+DAC应用经验分享

实战经验 | 基于 STM32U5 片内温度传感器正确测算温度

【文末有礼】新款STM32U5:让便携产品拥有惊艳图效

微信公众号

微信公众号

手机版

手机版