.png) STMCU小助手

发布时间:2022-8-23 18:23

STMCU小助手

发布时间:2022-8-23 18:23

|

正文 规则 和 注入 是两类通道,不是模式。 ADC时钟

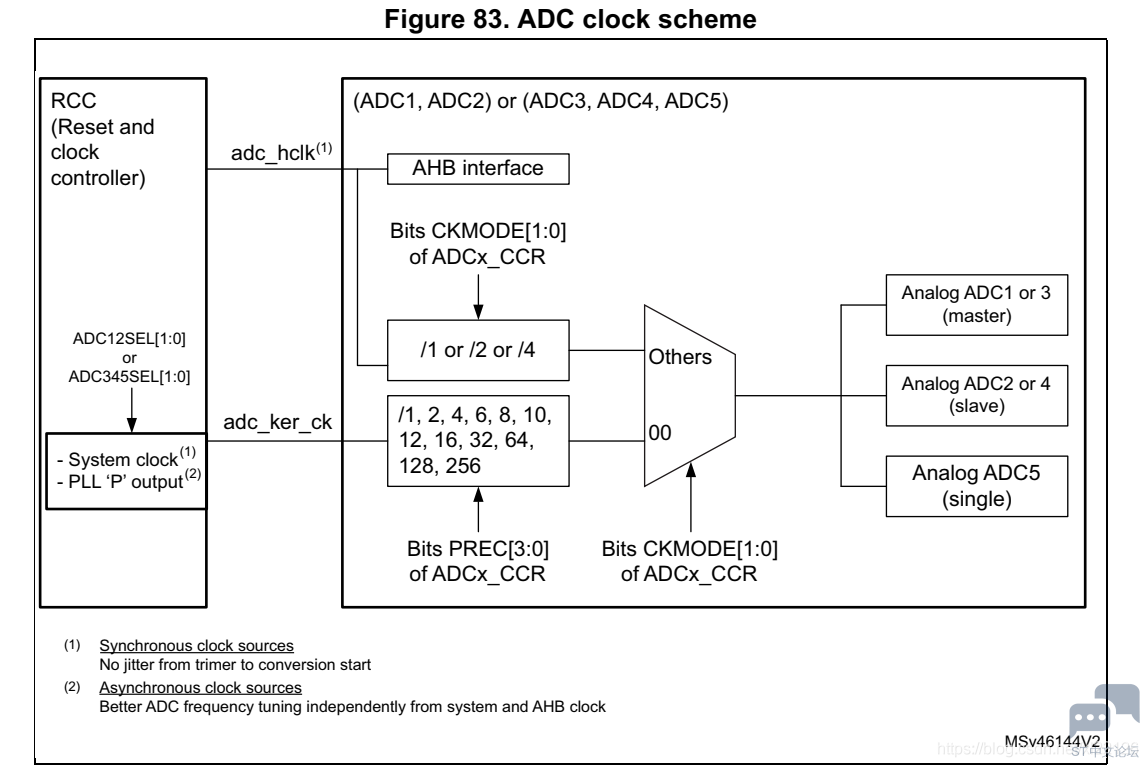

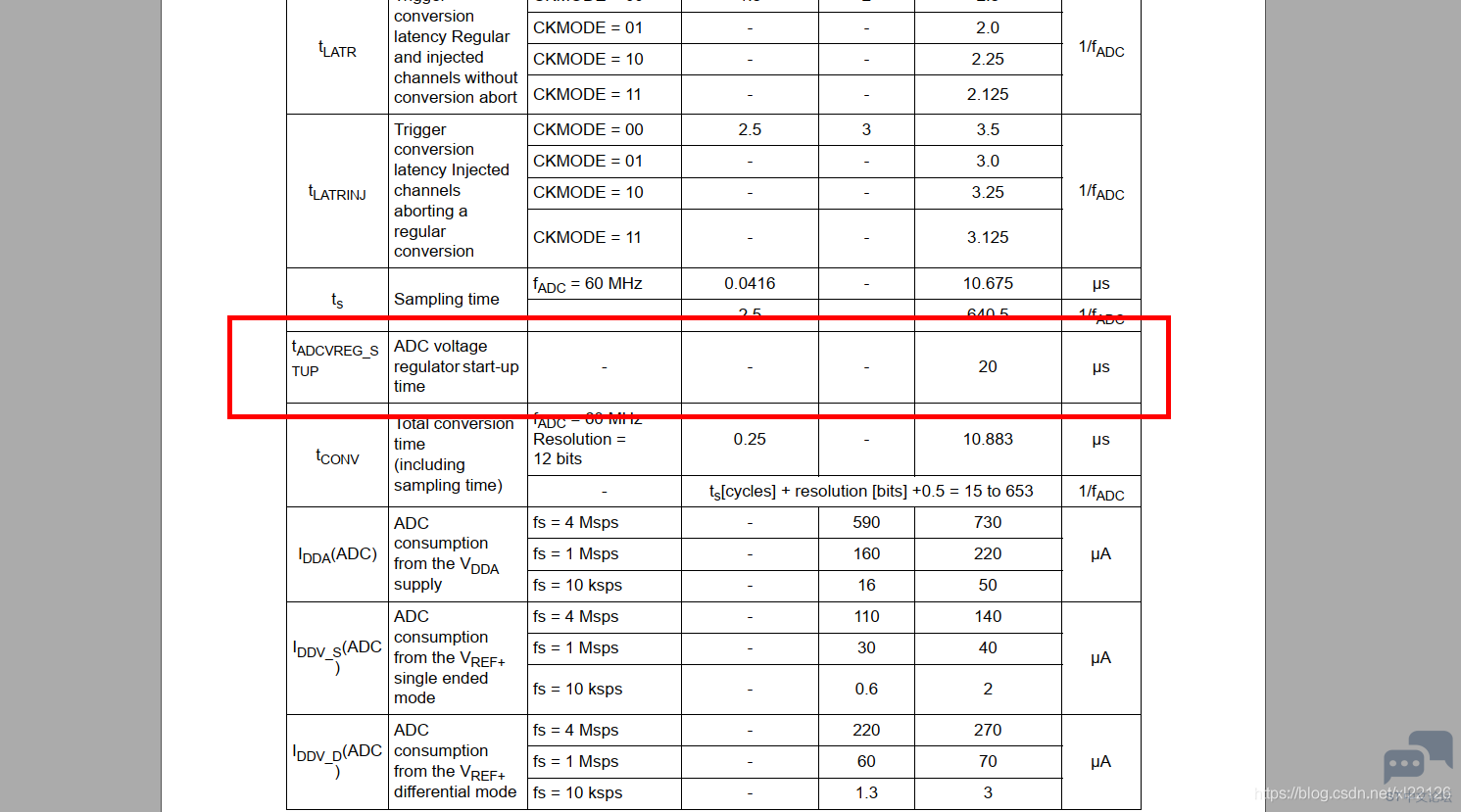

如果只用规则通道而不用注入通道,则ADC时钟与AHB没有约束关系。 上图可以看到,ADC的时钟输入有两个时钟源:adc_hclk 和 adc_ker_ck 。 adc_hclk 被认为是 同步时钟。 adc_ker_ck 被认为是 异步时钟,他也有两个输入时钟,可以通过 RCC_CCIPR 寄存器配置选择使用 SYSCLK 还是 PCLK 。 1. ADC的启动 1.1 退出深度掉电模式和ADC稳压器的开启 使用ADC的第一步就是退出“深度掉电模式”,即ADC->CR中的DEEPPWD = 0; 然后使能稳压器,即ADC->CR中的ADVREGEN = 1; 等待稳压器启动,具体启动时间参见数据手册。(G474数据手册写的是20us )数据手册第146页 DM00431551_ENV3

1.2 选择输入模式 ADC->DIFSEL 模式选择寄存器 中选择 差分输入或者单端输入模式。

1.3 校准 校准分为单端校准和差分校准

确定DEEPPWD=0(退出深度掉电模式),ADVREGEN=1(稳压器开启),并且已经等待了稳压器的启动时间。 确定ADEN=0。 配置ADC->CR寄存器中的ADCALDIF标志位,选择输入模式(ADCALDIF=0 单端输入 / ADCALDIF=1 差分输入)。 ADC->CR寄存器的ADCAL标志位置位,即开启校准(ADCALDIF配置为什么模式就校准什么模式)。 等待ADC->CR寄存器的ADCAL硬件清除,即ADCAL=0,代表校准结束。 在ADC->CALFACT寄存器中读取校准系数。 下面以单端输入校准为例:

如果通道中又有差分输入还有单端输入,则需要将两个系数都进行校准。 1.4 转换队列设置 1.5 采样时间设置

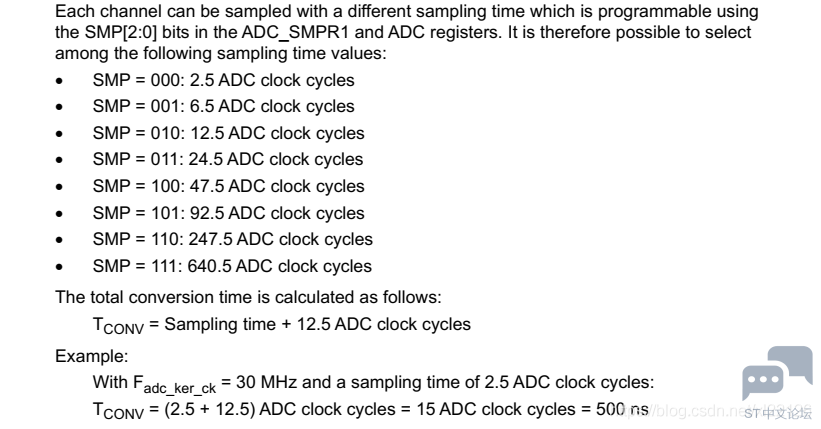

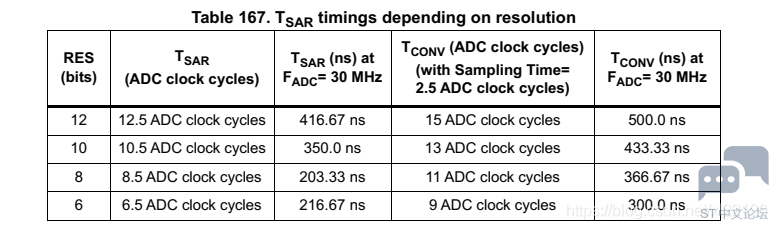

每个通道都可以用不同的采样时间进行采样,采样时间由ADC->SMPR1寄存器中的SMP位进行编程。因此,可以在以下采样时间值中进行选择: • SMP = 000: 2.5 ADC clock cycles • SMP = 001: 6.5 ADC clock cycles • SMP = 010: 12.5 ADC clock cycles • SMP = 011: 24.5 ADC clock cycles • SMP = 100: 47.5 ADC clock cycles • SMP = 101: 92.5 ADC clock cycles • SMP = 110: 247.5 ADC clock cycles • SMP = 111: 640.5 ADC clock cycles 总转换时间计算如下:TCONV = SMP + 12.5 ADC时钟周期(12-bit) 例如: Fadc_ker_ck = 30MHz,并且SMP=0 即2.5 ADC时钟周期 TCONV = (2.5 + 12.5)个 ADC 时钟周期,即 15 / 30 us = 500ns 采样结束后,ADC_ISR_EOSMP置位,代表采样结束(仅在规则转换中有效) 器与分辨率的转换时间如下表:

注意:

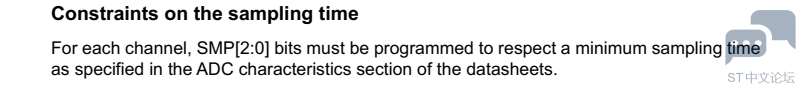

每个通道的采样时间必须遵循数据手册的最小采样时间。(数据手册第146页 DM00431551_ENV3)

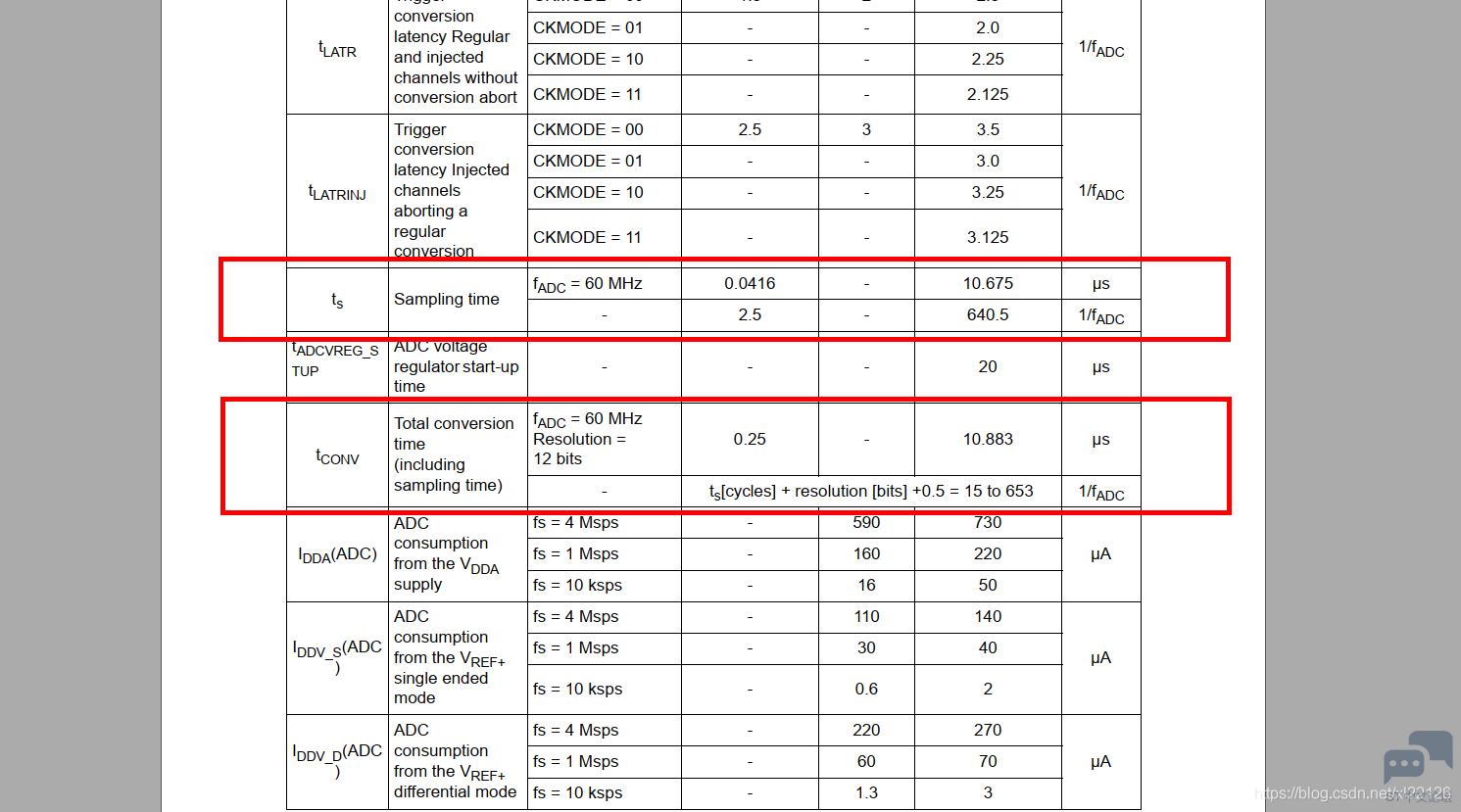

SMPPLUS control bit 在ADC->SMPR1寄存器中有这么个标志位,其作用是为了方便 交错模式 对称。 2 ADC采样模式 2.1 Bulb sampling mode(灯泡模式?) 启动该采样模式,则在第二个ADC空闲时间进行采样,如下图

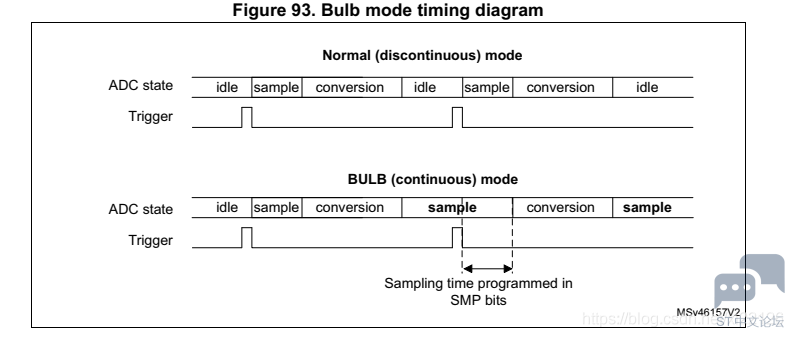

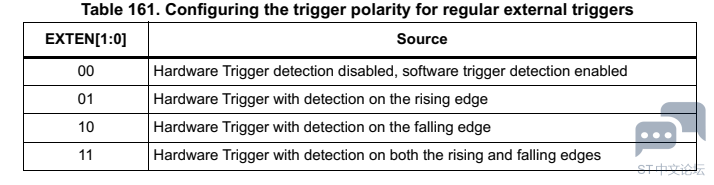

该采样方式有最大采样时间限制,参考数据手册。 该采样方式不适用连续采样和注入采样。 如果该模式启动(ADC->CFGR2中的BULB=1),则不准置位ADC->CFGR2中的SMPTRIG。 2.2 Sampling time control trigger mode(采样时间控制触发模式) 当SMPTRIG置位时(在ADC->CFGR2寄存器中),通过SMPx位(在ADC->SMPRx寄存器中)编程的采样时间是无效的。采样时间由触发信号边缘控制。 该模式分为软件控制和硬件控制: 硬件触发 当选择硬件触发器时,触发信号的每个上升沿开始采样周期。下降沿结束采样周期并开始转换。EXTEN(外部触发极性选择,在ADC->CFGR寄存器中)必须设置为01(上升沿有效)。 Hardware triggers with not defined rising and falling edges (one pulse event) cannot be used in Bulb mode. 软件触发 当选择软件触发器时,软件触发器不是ADC->CR中的ADSTART位,而是ADC->CFGR2寄存器中的SWTRIG位。置位SWTRIG位开始采样周期,清除SWTRIG位结束采样周期同时开始转换。EXTEN(外部触发极性选择,在ADC->CFGR寄存器中)必须设置为00(禁止外部触发)。 3. 转换模式 3.1 单次转换模式(CONT=0) 当ADC_CFGR_CONT=0,代表配置为单次转换模式。 规则模式:置位ADSTART(ADC->CR寄存器)或者外部触发 注入模式:置位JADSTART(ADC->CR寄存器)或者外部触发 在规则序列中,每次转换完成后 转换后的数据存储到16位ADC_DR寄存器 置位ADC_ISR_EOC(结束常规转换)标志(读取或者写1 清零) 如果设置了ADC_IER_EOCIE位,就会产生一个中断 在注入序列中,每次转换完成后 转换后的数据存储到16位ADC_JDRy寄存器 置位ADC_ISR_JEOC(结束常规转换)标志(读取或者写1 清零) 如果设置了ADC_IER_JEOCIE位,就会产生一个中断 在规则序列完成后 ADC_ISR_EOSEOS标志位置位(写1清零) 如果ADC_IER_EOSIE置位,则会产生一个中断 在注入序列完成后 ADC_ISR_JEOS标志位置位(写1清零) 如果ADC_IER_JEOSIE置位,则会产生一个中断 提示:如果想转换单个通道请将 L(队列转换长度,在ADC1->SQR1寄存器中)设置为0(0代表转换1次也就是1个通道)。 3.2 连续转换模式(CONT=1) 当ADC_CFGR_CONT=1,代表配置为连续转换模式。 只有规则通道有连续转换模式。 在规则序列中,每次转换完成后 转换后的数据存储到16位ADC_DR寄存器 置位ADC_ISR_EOC(结束常规转换)标志(读取或者写1 清零) 如果设置了ADC_IER_EOCIE位,就会产生一个中断 在规则序列完成后 ADC_ISR_EOSEOS标志位置位(写1清零) 如果ADC_IER_EOSIE置位,则会产生一个中断 然后,一个新的序列立即重启,ADC连续重复转换序列。 禁止同时置位 ADC_CFGR_DISCEN 和 ADC_CFGR_CONT。 注入通道要想连续转换,需要设置自动注入。 连续转换模式下,ADSTART不会被硬件清除。 不能同时使能ADC_CFGR_DISCEN和ADC_CFGR_CONT。 3.3 不连续模式 当ADC_CFGR_DISCEN=1,开启不连续模式,每次触发都只转换ADC_CFGR_DISCNUM个通道数量,每次转换都会置位EOC标志位,直到转换完ADC->SQR里面的通道(总个数为ADC->SQR1中的L),最后置位EOS标志位。 当ADC_CFGR_DISCEN=0,关闭不连续模式,一次触发转换ADC_SQR1_L个通道,每次转换都会置位EOC标志位,最后置位EOS标志位。 不能同时使能ADC_CFGR_DISCEN和ADC_CFGR_CONT。 4. 触发模式 ADSTART 当EXTEN[1:0] == 0,ADSTART=1立即触发转换 当EXTEN[1:0] != 0,ADSTART=1得等待下个有效硬件触发才进行转换 JADSTART 当JEXTEN[1:0] == 0,JADSTART=1立即触发转换 当JEXTEN[1:0] != 0,JADSTART=1得等待下个有效硬件触发才进行转换 外部触发 当注入队列使能(ADC_CFGR_JQDIS=0),软件不能触发注入通道。 转换过程中,触发会被忽略。 触发极性

触发源

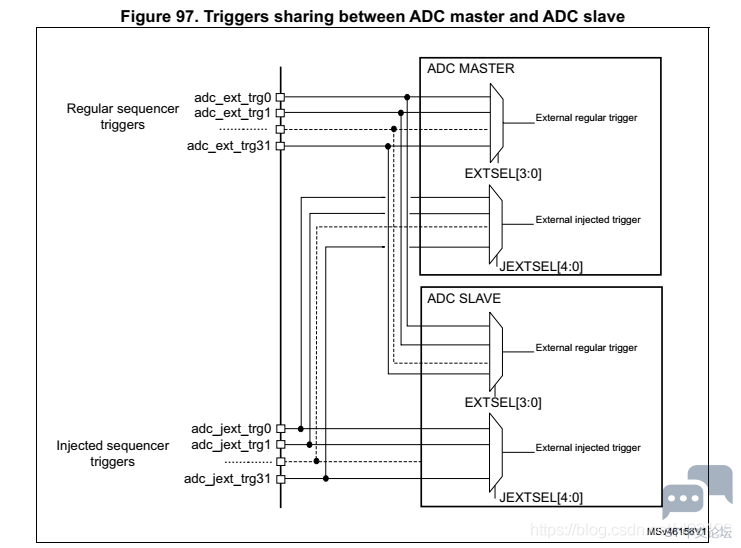

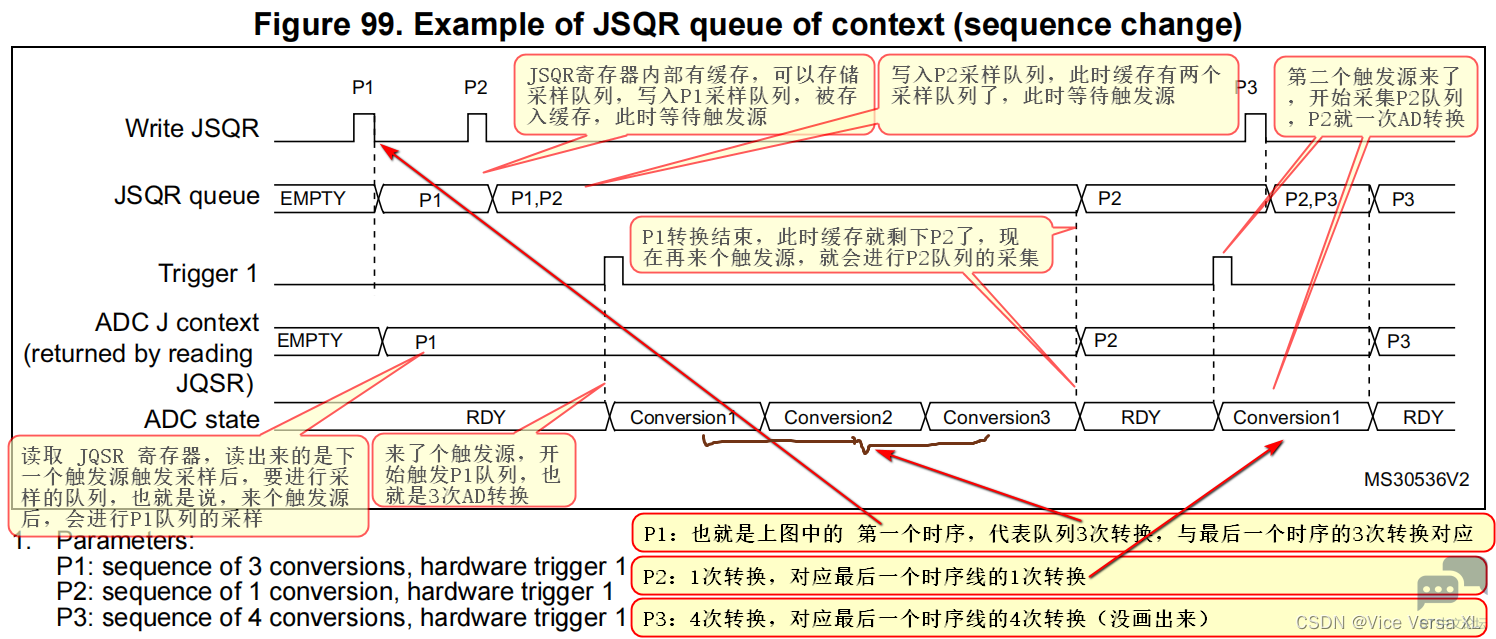

具体触发源见手册的第627页(DM00355726_ENV4) 5. 使用方法 5.1 注入模式 5.1.1 描述 注入模式 的优点就是相比 规则转换模式,队列模式 有更好的灵活性,它可以在ADC使能运行的情况下,修改 触发源 和 采样队列。对于经常变换 通道采样 或者 触发源 的工况下,这种模式更适合应用。 5.1.1 触发注入模式 在选择触发注入模式时,JAUTO 控制位(自动注入) 必须清除 通过外部触发或通过设置 ADC_CR 寄存器中的 ADSTART 位来启动一组常规通道的转换 如果发生外部注入触发,或者在常规通道组转换期间设置了 ADC_CR 寄存器中的 JADSTART 位,则当前执行的规则转换复位,然后启动注入转换序列(所有注入通道转换一次) 然后,恢复上次中断的常规转换 如果在注入转换期间发生常规事件,则注入转换不会中断,而是在注入序列结束时执行常规序列 配置 触发注入 模式的方法如下: 退出 睡眠模式(清除ADC_CR寄存器中的位DEEPPWD) 使能 ADC电压调节器(置位ADC_CR寄存器中的位ADVREGEN),延时等待电压调节器稳定 配置校准的模式(差分 和 单端 ,ADC_CR寄存器中的位ADCALDIF) 使能校准(ADC_CR寄存器中的位ADCAL),等待ADCAL清除,代表校准完毕 如果需要存储校准值可以读取CALFACT寄存器获取校准值,下次上电直接写入该寄存器 配置 ADC12_CCR 寄存器,选择单独工作还是同步工作、时钟配置、传感器使能采样延时等参数 配置ADC_CFGR寄存器,清除位JQDIS,允许注入模式,DMA、采样模式等参数 配置ADC_SMPR寄存器,来确定采样时间 配置ADC_IER寄存器,使能需要的中断 使能ADC(ADC_CR寄存器中的位ADEN),等待ADC就绪(等待ADC_ISR中的位** ADRDY**置位) 允许注入触发(ADC_CR寄存器中的位JADSTART) 可以在任意处配置ADC_JSQR寄存器,选择触发源和采样序列。 下面是 ADC12同步注入模式 ADC1、2 触发模式,每次触发序列为2次转换 触发源为 TIM1的TIGRO2 转换序列为 ADC1 第一次转换通道3 第二次转换同道4 ADC2 第一次转换通道2 第二次转换同道15

下面是触发注入模式,在ADC运行过程中,修改 采样队列 的时序图。

5.1.2 自动注入模式 5.1.3 DMA请求 双ADC模式 当ADC_CCR_DUAL不等于0的时候,ADC进入双ADC模式,双ADC模式下,从ADC的配置位和主模式的配置位共享(CFGR寄存器),只需在主ADC中配置触发源、触发方式、触发极性、注入触发源、注入触发极性就可以,从ADC不用配置。 附录 寄存器表

———————————————— 转载:Vice Versa XL |

NUCLEO-G474RE 扩展 LSM6DSO 传感器数据融合实操演示全解析

经验分享 | STM32G474 高精度定时器同步功能全解析 从内部互联到多芯片协同的实现方案

经验分享 | STM32G4双BANK启动应用演示

STM32G4 LPTIM+DMAMUX 实现并行输出应用示例

实战经验 | LAT1578 SAU对NSC分区的影响

经验分享 | STM32G474 HRTIM Triggered-half模式实现两相交错电源180°相位同步方案

STM32大神笔记,超详细单片机学习汇总资料

经验分享 | 为什么重启ADC的DMA传输要先停掉ADC?

实战经验 | 基于STM32G474的三相LLC+SR PWM产出方案

STM32固件库分享,超全系列整理

微信公众号

微信公众号

手机版

手机版