.png) STMCU小助手

发布时间:2022-10-12 22:59

STMCU小助手

发布时间:2022-10-12 22:59

|

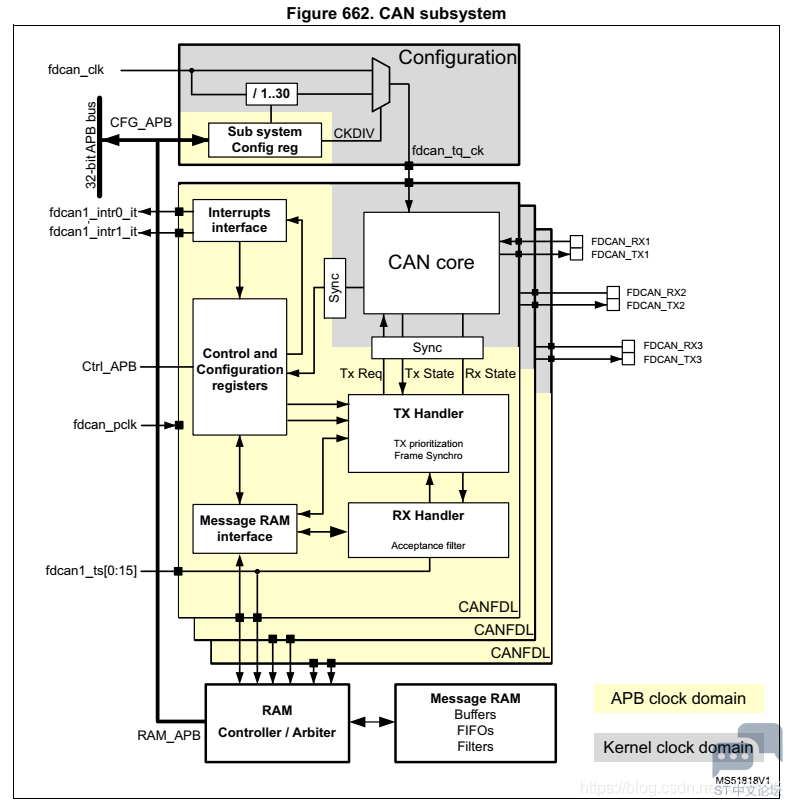

FDCAN 与 经典CAN 的最直观差别就是数据帧部分,FDCAN的数据帧波特率可变,并且数据大小不局限于 8 Bytes ,最高支持 64 Bytes 的数据传输。详细差别见 传送门: CAN FD 与 CAN协议区别–简单易懂协议详解 。 1. FDCAN的框图

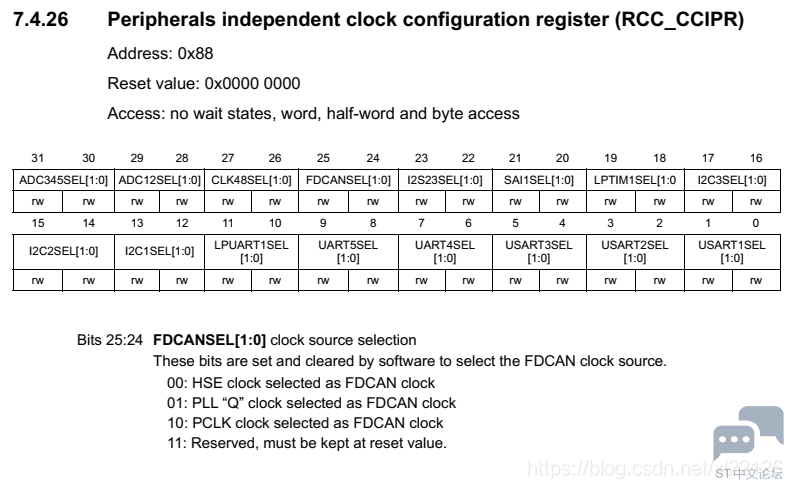

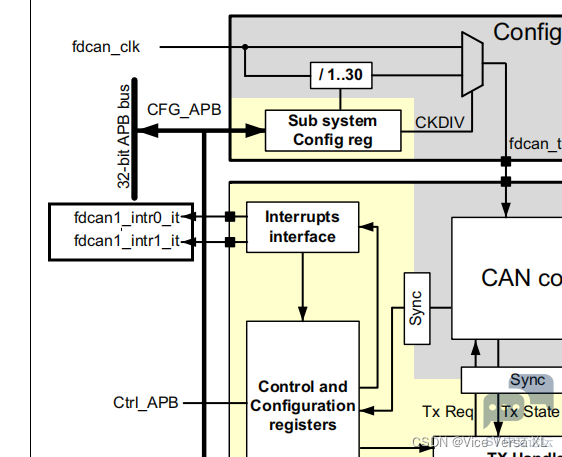

根据上图可以看到,FDCAN 有两个时钟域,APB总线接口和CAN内核时钟。FDCAN的波特率取决于内核时钟;寄存器的配置、消息RAM等,走的是APB时钟。FDCAN的APB时钟在RCC_APB寄存器中配置,内核时钟在RCC_CCIPR寄存器中配置(下一章)。 FDCAN有两个中断线,这两个中断线可以单独的打开或关闭,在FDCAN_ILE寄存器中配置。 其他具体介绍参考DM00355726_ENV4手册的1947页(RM0440手册官方下载传送门)。 2. FDCAN的时钟与波特率 2.1 fdcan_clk 几乎所有通信都可在RCC中配置时钟选择,FDCAN的时钟(fdcan_clk)可在RCC_CCIPR寄存器中进行配置。

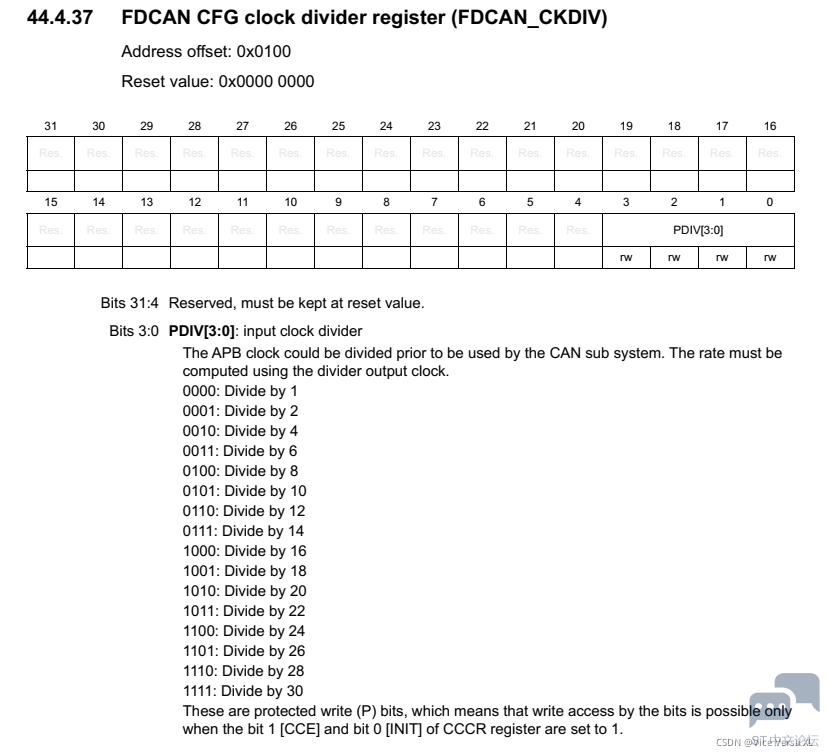

FDCAN1/2/3 的内核时钟是通用的,可以在配置FDCAN1的时候,配置 CKDIV 寄存器进行进一步的分频(INIT标志位置位才可配置该寄存器),这里配置的CKDIV影响到 FDCAN2 和 FDCAN3。 2.2 fdcan_tq_ck 根据系统框图可看到,系统输入的时钟可通过 fdcan_clk 分频得到 fdcan_tq_ck ,在 FDCAN_CKDIV 寄存器中配置分频系数。

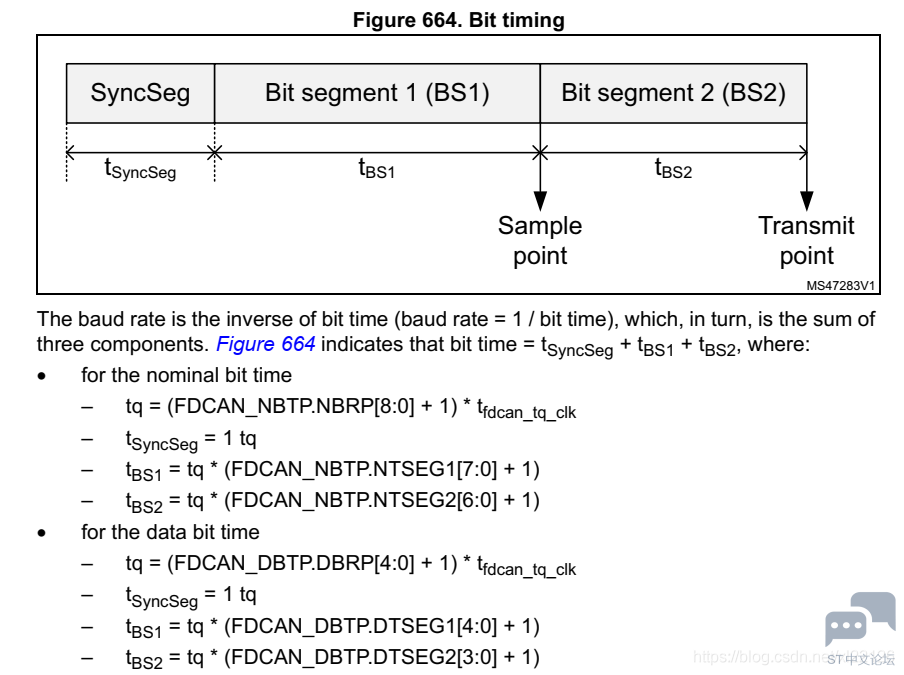

可以认为FDCAN内核用的时钟都是fdcan_tq_ck ,只不过 fdcan_tq_ck 为1分频时候认为是fdcan_clk 。 2.3 波特率 FDCAN模块的bit采样分三段:

波特率公式如下: ![Z)68{@VPG1Y@2)]D{AJ)%RC.png Z)68{@VPG1Y@2)]D{AJ)%RC.png](data/attachment/forum/202210/12/231154ze1cao7kg7lytoz2.png)

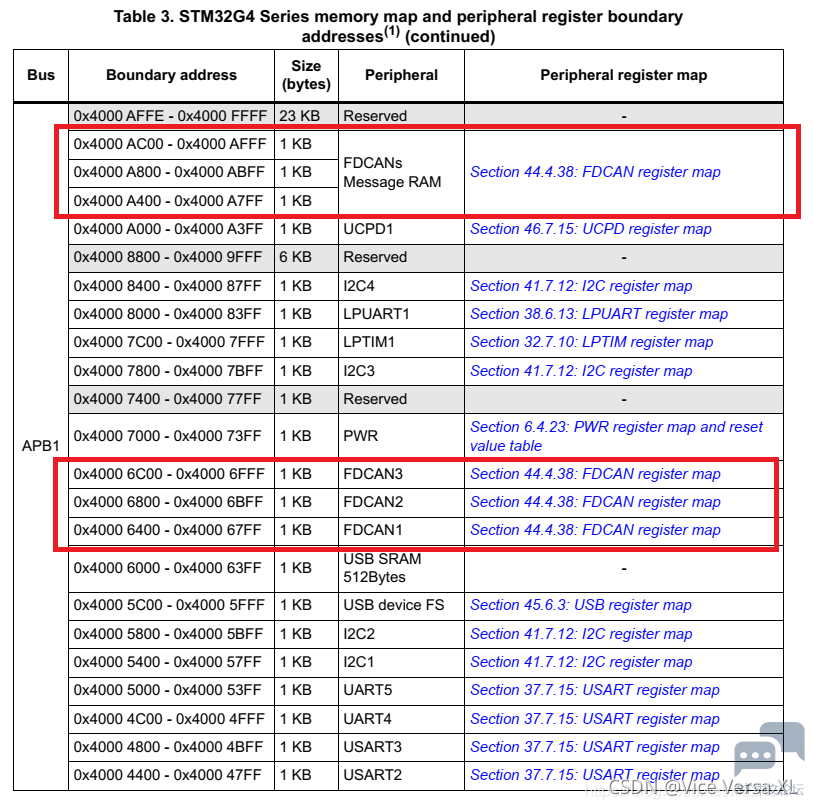

注意: 1、由于 FDCAN 与 经典CAN 的帧格式有点差异,其数据帧波特率可变,因此在这里分出普通CAN和数据bit时间 2、数据 和 普通 bit 时间寄存器名称不一样,数据波特率寄存器 FDCAN_DBTP ,一般帧波特率寄存器为 FDCAN_NBTP 。当使用经典模式CAN时, FDCAN_DBTP 配置被忽略 3. FDCAN的地址分布 3.1 总体分布

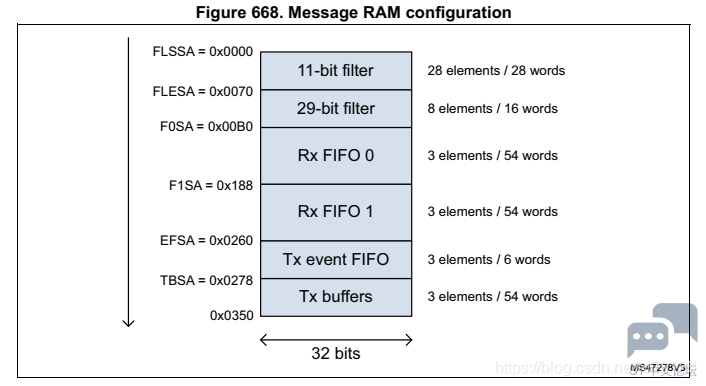

由于头文件中没有该寄存器的宏定义,因此需要自己建立宏定义。 G474的FDCAN外设一共有3组(FDCAN1,FDCAN2,FDCAN3),寄存器配置分为3个,消息RAM也分为3组。 3.2 Message RAM

1个 信息RAM 有 212 words 的大小,即 212 × 4 = 848 Bytes 。 根据3.1和3.2可以先把 消息RAM 的宏定义写好

注意!!! 上面的代码第1行的宏定义部分,偏移为 0x350 而不是 0x400。 曾经我根据 3.1里面的图片进行配置(0x400也就是1KB),结果只有FDCAN1好用,FDCAN2和FDCAN3都不能使用,困扰了我一天来找这个问题,后来使用 0x350 就可以了,可能是手册写错了,也可能是我的理解与有误。 这里是个坑,希望大家能够规避一下。 4. FDCAN中断配置 4.1 中断寄存器 FDCAN中断配置中,涉及的寄存器为 FDCAN_IE 与其他外设的IE一样,中断使能寄存器,在这里选择使用的中断,在代码中会注释 FDCAN_ILE 中断总线使能。FDCAN中将中断分为了两个分支,即有两个中断函数 FDCAN_ILS 中断总线选择。在这个寄存器中配置哪个中断归属于哪个中断分支,默认都为分支0.

5. FDCAN的筛选器 5.1 筛选器的特征 每个筛选器可配置为 • 范围筛选 • 指定ID筛选 • 屏蔽典型bit筛选 每个过滤器元件可配置为接受或拒绝过滤 每个过滤器元素可以单独启用/禁用 过滤器是按顺序检查的,执行在第一个匹配的过滤器元素时停止 相关的寄存器:全局筛选配置(RXGFC)、拓展ID和掩码(XIDAM) 如果需要接收数据,一定要配置筛选器,否则会什么也接受不到。 5.2 11-bit 筛选器的格式

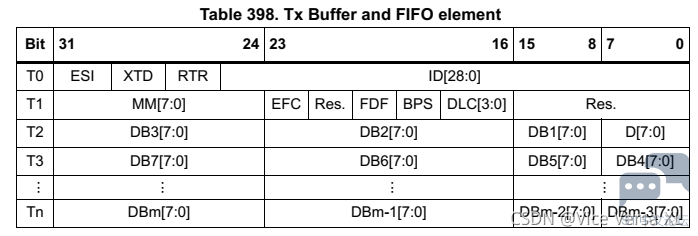

这里根据手册的翻译进行配置就好,29-bit 的筛选器也是如此,手册里全有,我就不放图片了,太占地方。 通过配置筛选器,可以使FDCAN外设接收其他模块发来的信息,在筛选器中配置接收消息的FIFO或者拒收消息。配置筛选器是FDCAN接收的关键。 筛选器的配置不受 INIT 和 CCE 标志位的限制,可随时配置。 6. FIFO模式与Queue模式 FIFO模式与队列模式的区别为: 队列模式的优先级遵循邮箱0优先级最高,其次是1,最后是2,如果当前3个邮箱全有数据,优先发送邮箱0的数据 FIFO模式的优先级是遵循哪个数据先进入的邮箱,与其所在的索引地址无关,即:如果当前3个邮箱全有数据,邮箱2被最先写入,则优先发送邮箱2的数据。 6.1 TX FIFO 的寄存器格式

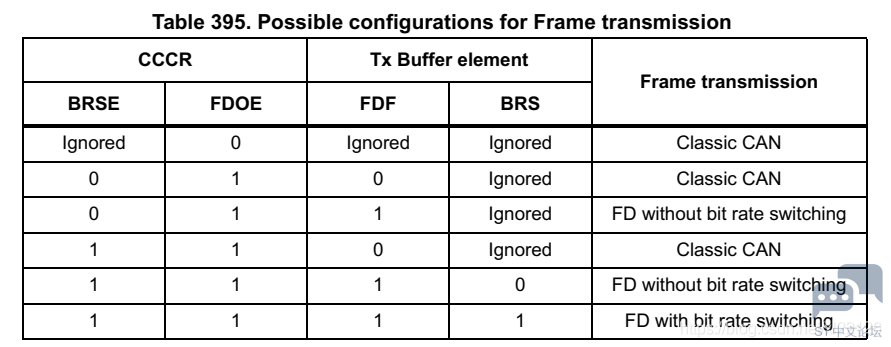

具体说明见手册1969页,我就不复制了,翻一下就能懂每个BIT代表的意思。 根据上表,我们就可以写出对应各个标志位的结构体,方便后期指针使用。 由于其buffer支持 11-bit ID 和 29-bit ID 7. FDCAN的初始化 IO口配置我就不介绍了,想必大家都会配置IO。 1.首先在RCC->APB1RSTR1寄存器中使能RCC_APB1ENR1_FDCANEN,这样FDCAN的寄存器就可以配置了。 2.然后选择FDCAN内核时钟的时钟源,在RCC->CCIPR寄存器的RCC_CCIPR_FDCANSEL中配置。 3.置位INIT标志位,开始配置寄存器(只有INIT标志位置位,才可置位CCE标志位) 4.等待INIT标志位置位 5.置位CCE标志位,解锁受保护的寄存器 6.等待CCE标志位置位 7.配置时钟分频 (FDCAN_CKDIV 寄存器) 8.配置波特率 9.配置中断 10.使能筛选器 11.配置筛选器 清除INIT标志位 到此,FDCAN就配置完了,具体操作见代码 初始化代码见 8. 发送操作 8.1 FDCAN帧模式 FDCAN帧模式由下表各个标志位配置:

根据上表所示,可以通过 CCCR寄存器 和 Tx Buffer 内部的标志位 配合,实现不同模式的CAN。 由于鄙人只想使用 经典CAN,因此将 CCCR寄存器 中的 FDOE 配置为 0,其他标志位我就不管了。 8.2 发送步骤 读取 FDCAN1->TXFQS 是否有可用信箱( FDCAN_TXFQS_TFQF 是否置位) 如果没置位邮箱满标志,则查询 FDCAN_TXFQS_TFQPI 索引,获得的索引就是可以写入的邮箱 将要发送的数据写入刚才读取的索引的 Tx Buffer 中(在这里可以配置发送长度、ID等信息) 置位发送请求 等待发送完成(可以不等待,配置发送完成中断使能后,在中断中置位发送完成标志来判断是否发送完毕) 示例代码见 附录2 发送函数 代码中的部分宏定义是根据手册定义的,由于太长就不放在这里了,完整代码在 代码下载 9. 接收操作 首先配置筛选器来选择接收的消息和接收后存放的FIFO。 接收分为 覆盖模式 和 阻塞模式 。 覆盖模式 顾名思义,就是当FIFO满了以后,接收到新消息后覆盖老消息。 阻塞模式 就是当FIFO满了之后,忽略新消息,保留老消息。 当 Rx FIFO 0 接收到消息后,将会在 FDCAN_RXF0S 寄存器中 F0GI 标志位指示新消息存储索引,当 CPU 读取这些消息后,务必将最后 F0GI 的值写入到 FDCAN_RXF0A 的 F0AI 标志位,来确认来读取完毕,这会将 FDCAN_RXF0S寄存器中的索引标志位 F0GI 设置为 F0AI + 1 并更新 FIFO 0 的存储计数 (FDCAN_RXF0S 寄存器中 F0FL 标志位,范围0~3),如果不确认读取完毕,将会导致指示索引 F0GI 失效。 接收操作可以在中断中进行,通过配置 FDCAN_IE 寄存器中的相应 中断使能标志位 来开启中断,具体示例见初始化代码。如:使能 FIFO0 接收新消息中断就置位 FDCAN_IE_RF0NE 标志位。 因此,接收操作的步骤为: 1.读取接收的数据 2.确认读取完毕 10. 故障 故障处理这里就不介绍了,值得注意的是: 当CAN两个总线短接,超过一定时间后,FDCAN会因为不能检测到有效电平而置位故障标志,同时置位初始化 INIT 标志,导致CAN关闭,排除硬件故障后可直接复位 INIT 标志来恢复故障前的运行状态(也就是说可以正常收发数据了)。 11. 参考资料传送门 11.1 代码下载(0积分) 代码下载(0积分) 11.2 其他 CAN 知识了解 其他 CAN 知识了解 附录1. FDCAN寄存器配置 返回第7章 FDCAN的初始化 返回第9章 接收操作

附录2 发送函数 返回第8章 发送操作

附录3 接收中断程序

———————————————— 版权声明:Vice Versa XL |

NUCLEO-G474RE 扩展 LSM6DSO 传感器数据融合实操演示全解析

经验分享 | STM32G474 高精度定时器同步功能全解析 从内部互联到多芯片协同的实现方案

经验分享 | STM32G4双BANK启动应用演示

STM32G4 LPTIM+DMAMUX 实现并行输出应用示例

实战经验 | LAT1578 SAU对NSC分区的影响

经验分享 | STM32G474 HRTIM Triggered-half模式实现两相交错电源180°相位同步方案

STM32大神笔记,超详细单片机学习汇总资料

经验分享 | 为什么重启ADC的DMA传输要先停掉ADC?

实战经验 | 基于STM32G474的三相LLC+SR PWM产出方案

STM32固件库分享,超全系列整理

微信公众号

微信公众号

手机版

手机版