.png) STMCU小助手

发布时间:2022-11-12 14:35

STMCU小助手

发布时间:2022-11-12 14:35

|

引言 本文档介绍了 STM32H7 系列微控制器上纠错码(ECC)的管理和实现。本应用笔记针对保护内部存储器内容的 ECC 机制,描述了与之相关的硬件、软件信息。除此之外,也可使用外部存储器进行 ECC 保护,但本文档不涉及其实现方法。 本文档介绍了 ECC 保护的一般信息、详细的硬件 ECC 故障管理,以及在 STM32H7 系列微控制器中实现 ECC 的具体方法。本文档提出了安全解决方案软件部分的具体实施方法。 本文档是对参考手册 STM32H745/755 和 STM32H747/757 高级 Arm®32 位 MCU(RM0399)以及 STM32H7A3/B3 高级Arm®32 位 MCU(RM0455)的补充。 1 概述 下表列出了本应用笔记中使用的首字母缩略词。

2 ECC 概述 首个 ECC 由数学家 Richard Hamming 发明。第一个 Hamming 码使用 7 位存储 4 位信息,冗余位用于纠正和检测错误。在 STM32H7 系列器件中,RAM 和 Flash 存储器均使用基于 Hamming 原理的 SEC-DED 算法进行保护,差别在于添加了额外的奇偶校验位。ECC 码能够检测和纠正存储的数据字中的一位错误,并对两位错误进行检测。 在 SRAM 易失性存储器中,杂散的阿尔法粒子可能会导致位值翻转。这一威胁持续存在,出现一位故障的概率不会随硬件的使用年限发生改变。在大量数据长期存储而不重置的应用中(例如电池供电的数据记录器),一位或两位错误故障的问题尤为严重。 在 Flash 存储器中,数据会随时间衰减,尤其是在高温下。存储温度会对 Flash 存储器数据产生影响,但循环(编程)温度的影响更大。Flash 存储器只能对每个存储字进行一定量的重写,这就需要在数据存储的情况下实现平均抹写存储区块。特定产品 Flash 存储器的典型保留时间和生命周期详见产品数据手册。 这两种类型的故障(一位错误和两位错误)均不可避免,但正确使用 ECC 可以防止数据丢失。 ![_G]0O_7HW4C75[]D5()}3DN.png _G]0O_7HW4C75[]D5()}3DN.png](data/attachment/forum/202211/12/143716kze4damssqkse8jp.png)

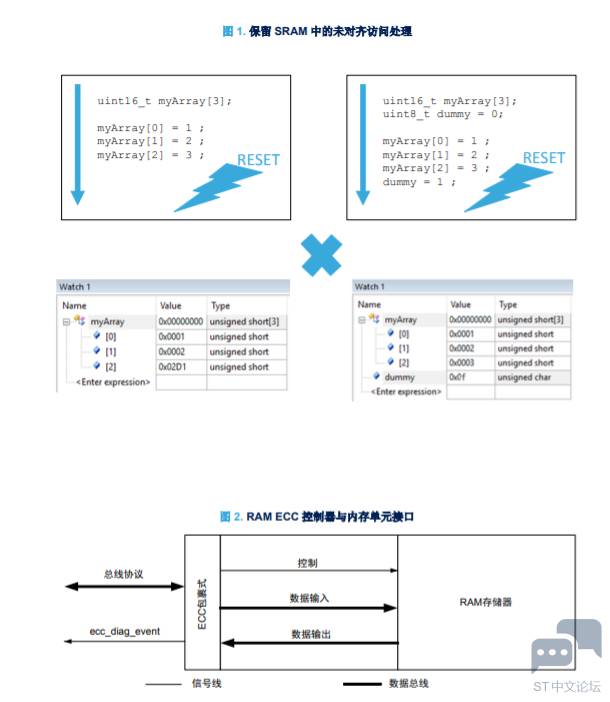

2.1 ECC 的影响 ECC 是嵌入式系统的关键要素之一,旨在符合安全标准的要求,如:IEC60730 C 级、IEC 61508 SIL2,乃至更高级别的标准。 缺乏硬件 ECC 的系统可能依然符合目标安全标准,但需要部署大量的软件。使用 ECC 内存能轻松地将总体诊断覆盖率提高到 90%以上,使系统能更好地符合严格的安全标准。ECC 的另一项优势是潜在的安全性改进,因为 ECC可能会检测到硬件篡改。 2.2 RAM ECC STM32H7 系列器件的 RAM ECC 功能具有类似外设的接口:带有设置寄存器和中断功能,能够对检测到的故障作出快速响应。所有 STM32H7x5 和 x7 SRAM 以及指令/数据高速缓存存储器均受 ECC 保护。AXI-SRAM 和 ITCMRAM 的数据宽度为 64 位。所有其他易失性存储器均以 32 位总线宽度(字长)访问。在 STM32H7x3 上,只有紧密耦合的内存和指令/数据缓存内存受 ECC 保护,其他 SRAM 不受保护。 与普通外设的主要区别在于,RAM ECC 无法进行关闭。ECC 和 RAM 的时钟、供电同步进行,且 ECC 是 RAM 接口的组成部分。例如,禁用备份 SRAM 时,也会禁用与其关联的 RAM ECC 控制器。 ECC 根据数据字计算。如果在易失性存储器中写入了小于字的数据,则在读取-修改-写入的基础上进行修改。如果访问不完整,则 ECC 不会立即写入该值。因为当中可能涉及到紧跟的字节或半字,所以 ECC 会等待下一次写入访问。这是处理备份 SRAM 应用程序中的常见情况。例如,在字符数组中的能量守恒。但是,无法在复位的情况下完成写入操作(内存内容将被保留,且不写入最后一个不完整的字)。 对应的解决方法,是在每个常规字之后写入一个虚拟的不完整字。虚拟写入地址必须在同一内存中(本例中为备份SRAM)。

RAM ECC 控制器分配给每个内部 SRAM 块。控制器分为三个系统域:D1、D2 和 D3。来自所有内部 SRAM 单元/控制器的诊断信息被收集到一个全局控制块中。该全局控制块有一组配置寄存器和一个带事件可屏蔽功能的全局中断信号。 ![_YCR(DBOMFK3AG5Z]WB21ZX.png _YCR(DBOMFK3AG5Z]WB21ZX.png](data/attachment/forum/202211/12/143716e9ydr1df7ppg4fpr.png)

分配给特定 SRAM 块的特定 RAM ECC 控制器会在每次读取该 SRAM 块时,检查数据完整性。有些读取访问类型并不明显,因为某些写入操作包含隐式读取阶段。关于不明显的读取访问,举例来说,是在两个周期内,以读取/修改/写入的方式执行不完整 RAM 写入操作。该写入操作可以是小于 RAM 字的数据写入,也可以是未对齐写入。 完整版请查看:附件 |

zh.DM00623136.pdf

下载399.19 KB, 下载次数: 4

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

经验分享 | STM32H7 TouchGFX 花屏速解:更换 HyperRAM 后 latency 值适配实操

经验分享 | STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H7Sx MCE 加密解密:外部存储安全防护全解析

如何在STM32和Arduino上实现卷积神经网络

详解STM32单片机的堆栈

STM32 开发者指南:ST.com 全新 MCU 产品阵容视觉布局深度解析

微信公众号

微信公众号

手机版

手机版