.png) STMCU小助手

发布时间:2023-1-16 14:00

STMCU小助手

发布时间:2023-1-16 14:00

|

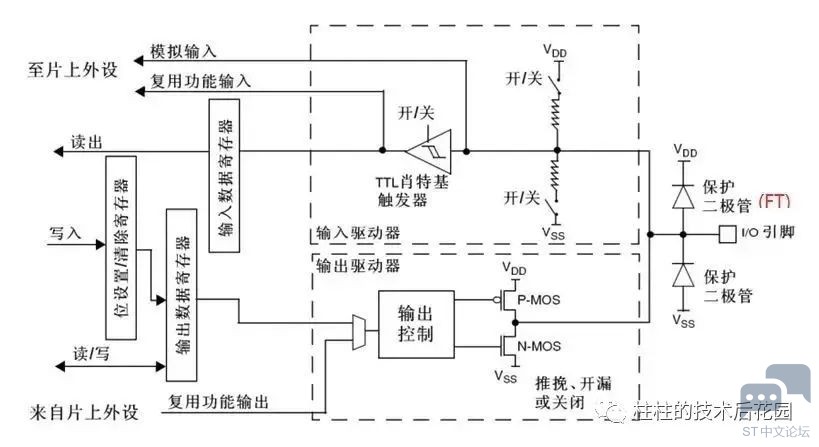

GPIO是通用输入/输出端口的简称,是STM32可控制的引脚。GPIO的引脚与外部硬件设备连接,可实现与外部通讯、控制外部硬件或者采集外部硬件数据的功能。 2 简介 2.1 GPIO内部结构

几点需要注意的地方: 1. 保护二极管:IO引脚上下两边两个二极管用于防止引脚外部过高、过低的电压输入。当引脚电压高于VDD时,上方的二极管导通;当引脚电压低于VSS时,下方的二极管导通,防止不正常电压引入芯片导致芯片烧毁。但是尽管如此,还是不能直接外接大功率器件,须加大功率及隔离电路驱动,防止烧坏芯片或者外接器件无法正常工作。 2. P-MOS管和N-MOS管:由P-MOS管和N-MOS管组成的单元电路使得GPIO具有“推挽输出”和“开漏输出”的模式。这里的电路会在下面很详细地分析到。3. TTL肖特基触发器:信号经过触发器后,模拟信号转化为0和1的数字信号。但是,当GPIO引脚作为ADC采集电压的输入通道时,用其“模拟输入”功能,此时信号不再经过触发器进行TTL电平转换。ADC外设要采集到的原始的模拟信号。这里需要注意的是,在查看《STM32中文参考手册V10》中的GPIO的表格时,会看到有“FT”一列,这代表着这个GPIO口是兼容3.3V和5V的;如果没有标注“FT”,就代表着不兼容5V。 2.2 GPIO工作模式 GPIO支持4种输入模式(浮空输入、上拉输入、下拉输入、模拟输入)和4种输出模式(开漏输出、开漏复用输出、推挽输出、推挽复用输出)。同时,GPIO还支持三种最大翻转速度(2MHz、10MHz、50MHz)。 每个I/O口可以自由编程,但I/O口寄存器必须按32位字被访问。

3.1 输入模式 3.1.1 浮空输入

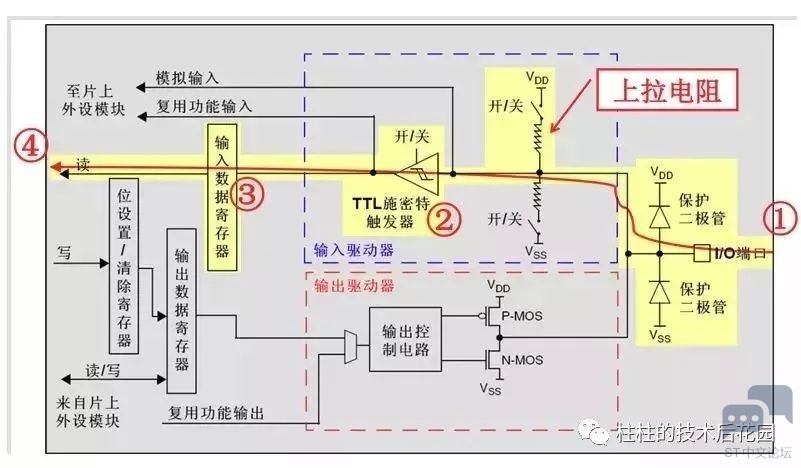

浮空输入模式下,I/O端口的电平信号直接进入输入数据寄存器。也就是说,I/O的电平状态是不确定的,完全由外部输入决定;如果在该引脚悬空(在无信号输入)的情况下,读取该端口的电平是不确定的。 3.1.2 上拉输入

上拉输入模式下,I/O端口的电平信号直接进入输入数据寄存器。但是在I/O端口悬空(在无信号输入)的情况下,输入端的电平可以保持在高电平;并且在I/O端口输入为低电平的时候,输入端的电平也还是低电平。 3.1.3 下拉输入

下拉输入模式下,I/O端口的电平信号直接进入输入数据寄存器。但是在I/O端口悬空(在无信号输入)的情况下,输入端的电平可以保持在低电平;并且在I/O端口输入为高电平的时候,输入端的电平也还是高电平。

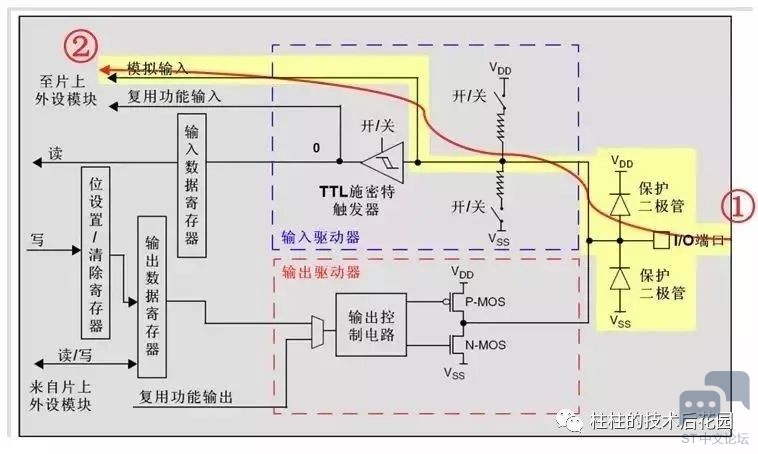

3.1.4 模拟输入

模拟输入模式下,I/O端口的模拟信号(电压信号,而非电平信号)直接模拟输入到片上外设模块,比如ADC模块等等。

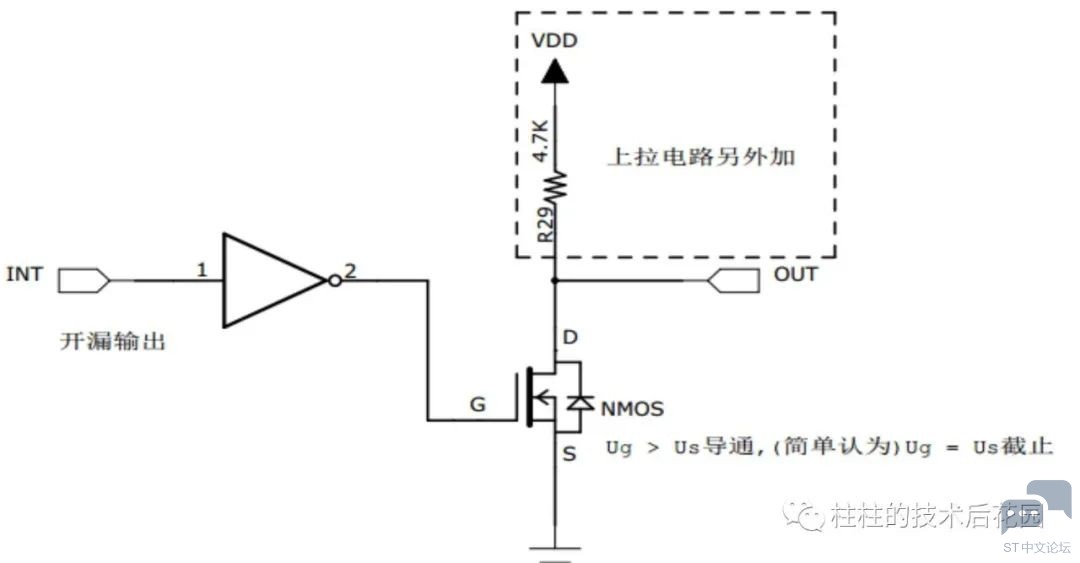

3.2.1 开漏输出

开漏输出模式下,通过设置位设置/清除寄存器或者输出数据寄存器的值,途经N-MOS管,最终输出到I/O端口。 这里要注意N-MOS管,当设置输出的值为高电平的时候,N-MOS管处于关闭状态,此时I/O端口的电平就不会由前面设置输出的高低电平决定,而是由I/O端口外部的上拉或者下拉决定; 当设置输出的值为低电平的时候,N-MOS管处于开启状态,此时I/O端口的电平就是低电平。同时,I/O端口的电平也可以通过输入电路进行读取; 注意,读取到的I/O端口的电平不一定是设置的输出电平。

3.2.2 开漏复用功能

开漏复用输出模式,与开漏输出模式很是类似。只是输出的高低电平的来源,不是让CPU直接写输出数据寄存器,取而代之利用片上外设模块的复用功能输出来决定的。

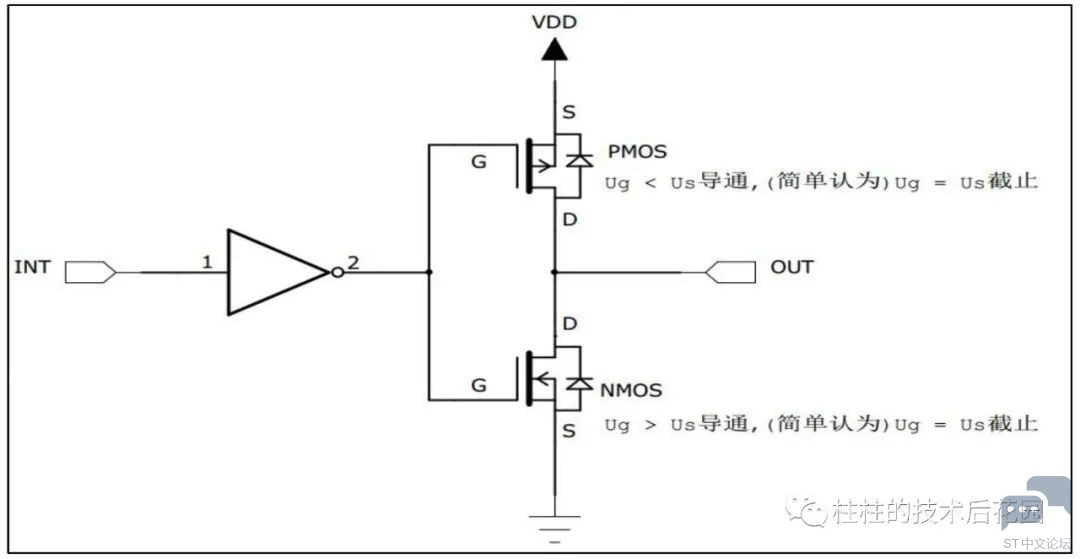

3.2.3 推挽式输出

推挽输出模式下,通过设置位设置/清除寄存器或者输出数据寄存器的值,途经P-MOS管和N-MOS管,最终输出到I/O端口。这里要注意P-MOS管和N-MOS管。 当设置输出的值为高电平的时候,P-MOS管处于开启状态,N-MOS管处于关闭状态,此时I/O端口的电平就由P-MOS管决定:高电平; 当设置输出的值为低电平的时候,P-MOS管处于关闭状态,N-MOS管处于开启状态,此时I/O端口的电平就由N-MOS管决定:低电平。同时,I/O端口的电平也可以通过输入电路进行读取;注意,此时I/O端口的电平一定是输出的电平。

3.2.4 推挽式复用功能

推挽复用输出模式,与推挽输出模式很是类似。只是输出的高低电平的来源,不是让CPU直接写输出数据寄存器,取而代之利用片上外设模块的复用功能输出来决定的。

第三节详细介绍了STM32F103ZET6的GPIO的八种工作模式,我们再引申阐述一下推挽输出和开漏输出的区别、开漏输出的特点,以及“线与”的概念。 4.1 推挽输出和开漏输出的区别

推挽输出等效电路图 推挽输出电路由两个MOS管组成(上方的P-MOS和下方N-MOS),而开漏输出则由上拉电阻和一个N-MOS管组成。推挽输出的工作原理是:当需要输出高电平时,上方P-MOS管导通,下方N-MOS管关闭。而若要输出低电平时,下方的N-MOS管导通,上方的P-MOS管关闭。当引脚高低电平切换时,两个MOS管轮流导通,一个负责灌电流,另一个负责拉电流,使得负载能力和开关速度都有很大的提高。

开漏输出等效电路图 开漏输出的工作原理是:若要输出低电平,则N-MOS管导通,输出接地,输出低电平。若要输出高电平时,N-MOS管关闭,则既不输出高电平又不输出低电平,为高阻态。所以,需要外接上拉电阻,让上拉电阻提供高电平的驱动能力。因为内部管脚为高阻状态,所以,其具有“线与”特性,即将多个开漏极直接直接相连,只有所有的开漏极都是高阻状态,输出才为高电平,否则,为低电平。

4.2 开漏输出的特点 开漏形式的电路有以下几个特点: 1. 利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经Rpull-up ,MOSFET到GND。IC内部仅需很小的栅极驱动电流。 2. 一般来说,开漏是用来连接不同电平的器件,匹配电平用的,因为开漏引脚不连接外部的上拉电阻时,只能输出低电平,如果需要同时具备输出高电平的功能,则需要接上拉电阻,很好的一个优点是通过改变上拉电源的电压,便可以改变传输电平。比如加上上拉电阻就可以提供TTL/CMOS电平输出等。(上拉电阻的阻 决定了逻辑电平转换的沿的速度 。阻 越大,速度越低功耗越小,所以负载电阻的选择要兼顾功耗和速度)。 3. OPEN-DRAIN提供了灵活的输出方式,但是也有其弱点,就是带来上升沿的延时。因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大;反之延时大功耗小。所以如果对延时有要求,则建议用下降沿输出。 4. 可以将多个开漏输出的Pin,连接到一条线上。通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系。这也是I2C、SMBus等总线判断总线占用状态的原理。

4.3 “线与” 在一个结点(线)上, 连接一个上拉电阻到电源 VCC 和 n 个 NPN 的集电极C 或 NMOS晶体管的漏极D, 这些晶体管的发射极E或源极S都接到地线上,只要有一个晶体管饱和, 这个结点(线)就被拉到地线电平上。

因为这些晶体管的基极注入电流(NPN)或栅极加上高电平(NMOS),晶体管就会饱和, 所以这些基极或栅极对这个结点(线)的关系是或非 NOR 逻辑. 如果这个结点后面加一个反相器, 就是或 OR 逻辑。 其实可以简单地理解为:在所有引脚连在一起时,外接一上拉电阻,如果有一个引脚输出为逻辑0,相当于接地,与之并联的回路“相当于被一根导线短路”,所以外电路逻辑电平便为0,只有都为高电平时,与的结果才为逻辑1。 转载自:硬件工程师炼成之路 |

|

很好的资料。开示例代码,不太容易理解的,在这里很容易明白。 |

OpenBLT移植到STM32F103战舰开发板上适用于所有STM32F103系列的Bootloader

TFT LCD 与 FSMC 的硬件连接大容量 STM32F10xxx FSMC 接口

单片机:初学者该了解的STM32F103基础知识

2025软件工具兔哥知道

STM32之继电器模块

STM32固件库分享,超全系列整理

【MCU实战经验】基于STM32F103的二轮平衡车(6轴上位机 源代...

10张图带你完全掌握STM32 GPIO,从入门到精通,收藏就够了!

如果你解决了这些问题,就可以直接学STM32

STM32的分类和选型

微信公众号

微信公众号

手机版

手机版