.png) STMCU小助手

发布时间:2023-3-11 22:23

STMCU小助手

发布时间:2023-3-11 22:23

先来一张中文参考手册中的系统架构图,可以看到,STM32H7系列包含两个SDMMC控制器:SDMMC1和SDMMC2。

在芯片手册中的架构图能够更直观地看出来:

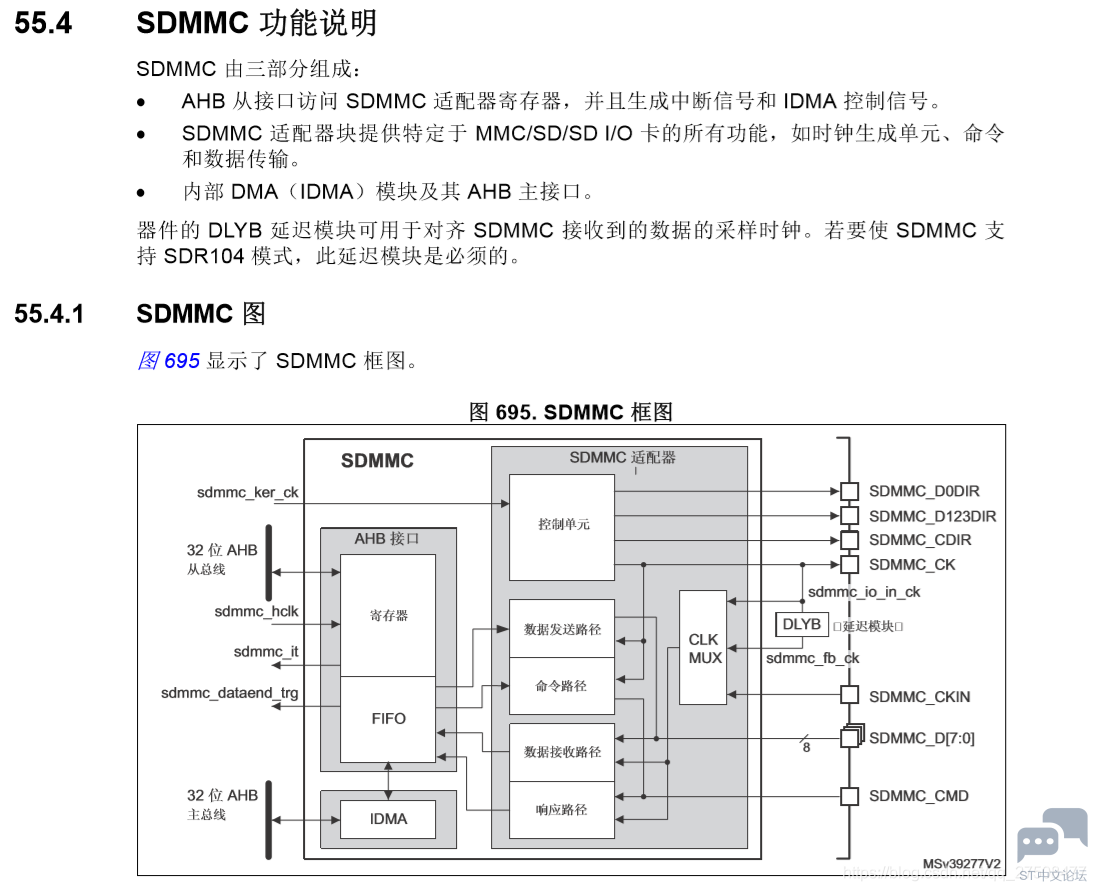

SDMMC内部集成一个IDMA,H7系列有很多总线主设备,包括DMA1、DMA2、BDMA、MDMA、DMA2D,还包括IDMA和以太网DMA这种专用DMA。

查看系统架构图和关于总线主设备的描述: SDMMC1和SDMMC2相比,和SRAM1、SRAM2都没有构成总线矩阵,只能访问AXI SRAM区域的内存。

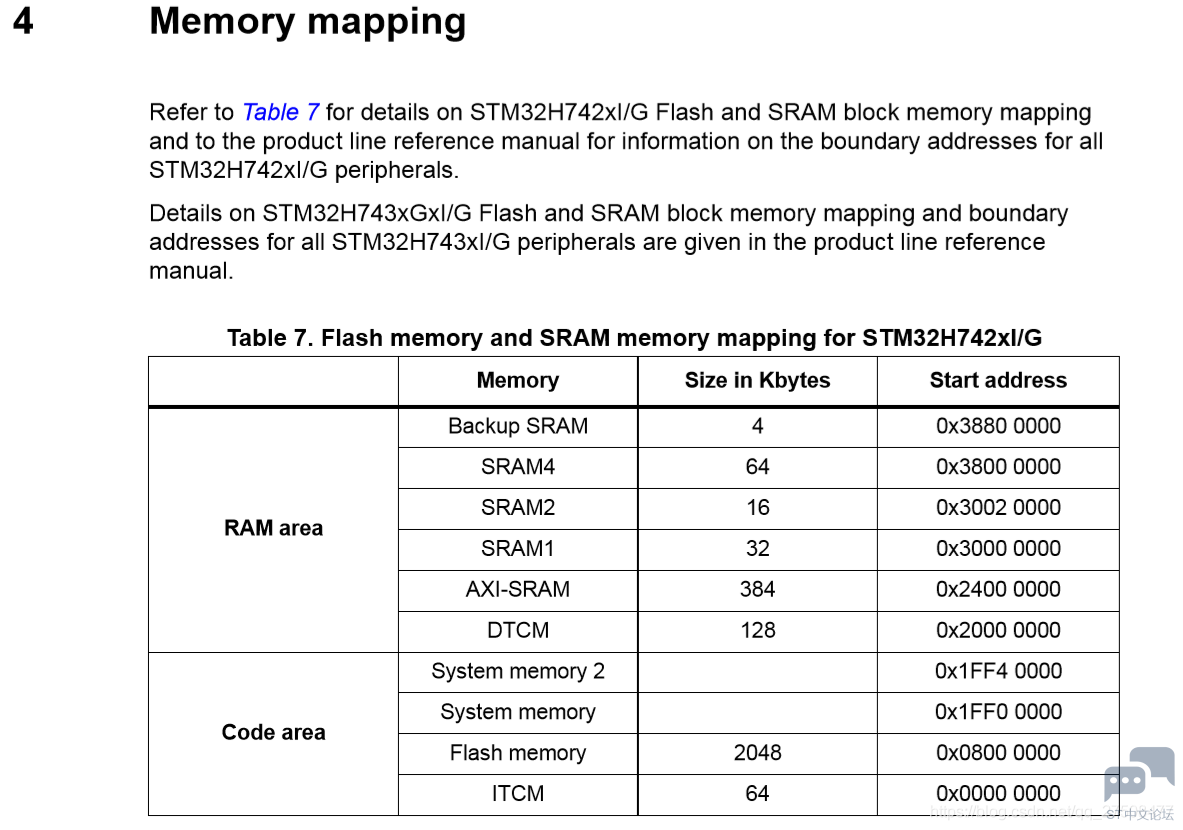

所以我们的使用IDMA进行SD卡的访问时,buffer必须放在AXI SRAM上面。 观察SRAM的分配,可以知道AXI SRAM分布在从0x24000000开始的512K区域上:

那么我们第一种情况,在编译器上只描述一部分内存DTCM:

在进行变量定义的时候强制指定地址:

可以看到指定的两个数组已经存在了AXI内存上,其他的都是DTCM内存上:

如果我们的工程配置上直接分配好了内存区域,这里使能了DTCM和AXI-SRAM内存:

这里我们并没有强制指定地址:

但是因为SRAM2的size要大一些,所以优先分配到SRAM2:

所以也是被分配在了AXI内存区域上。 ———————————————— 版权声明:小盼你最萌哒 |

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

经验分享 | STM32H7 TouchGFX 花屏速解:更换 HyperRAM 后 latency 值适配实操

经验分享 | STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H7Sx MCE 加密解密:外部存储安全防护全解析

如何在STM32和Arduino上实现卷积神经网络

详解STM32单片机的堆栈

STM32 开发者指南:ST.com 全新 MCU 产品阵容视觉布局深度解析

微信公众号

微信公众号

手机版

手机版