.png) STMCU小助手

发布时间:2021-12-15 11:00

STMCU小助手

发布时间:2021-12-15 11:00

|

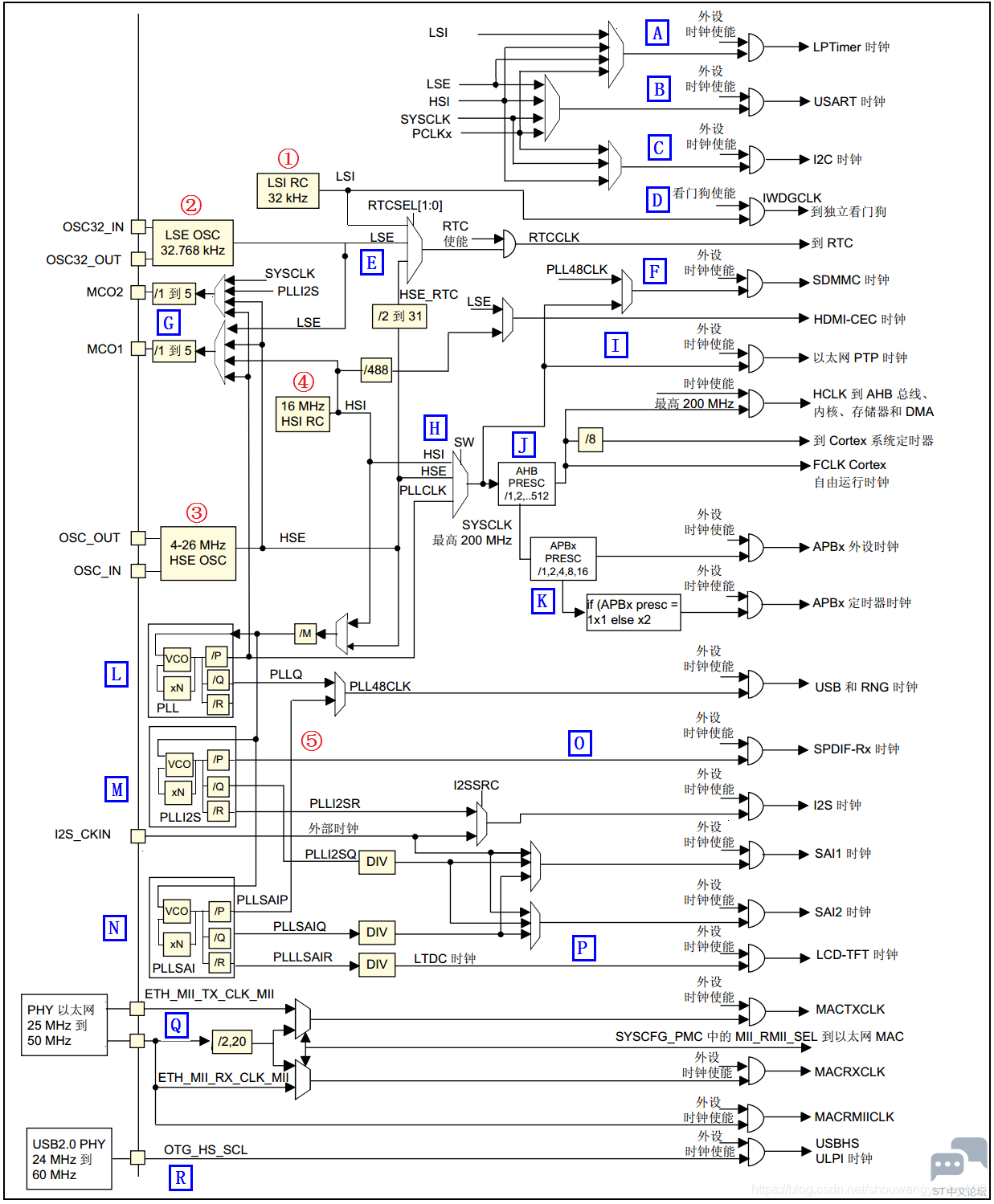

众所周知,时钟系统是CPU的脉搏,就像人的心跳一样。所以时钟系统对于单片机来讲是一个非常重要的东西。STM32F7的时钟系统比较复杂,有多个时钟源,为什么STM32要有多个时钟源呢?因为首先STM32本身非常复杂,外设非常的多,但是并不是所有外设都需要系统时钟这么高的频率,比如看门狗以及RTC只需要几十 k 的时钟即可。同一个电路,时钟越快功耗越大,同时抗电磁干扰能力也会越弱,所以对于较为复杂的 MCU 一般都是采取多时钟源的方法来解决这些问题。 1、STM32F7 的时钟系统图

2、STM32F7 时钟源 在STM32F7中,有5个最重要的时钟源,为LSI、LSE、HSE、HSI、PLL。分别对应上图的1~5: 简介如下:

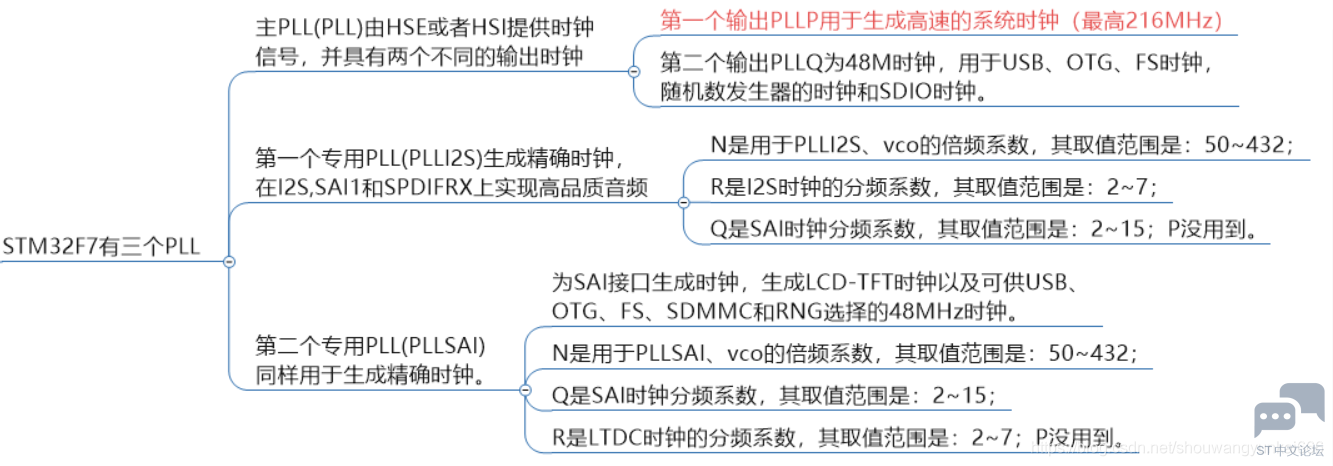

值得注意的是HSE:高速外部时钟。阿波罗 STM32F7 开发板接有 25MHz 外部晶振。 HSE 可以直接做为系统时钟或者 PLL 输入时钟,同时它经过2~31分频后也可以作为RTC时钟。 3、STM32F7 系统时钟 主 PLL 时钟第一个高速时钟输出 PLLP 用于生成高速的系统时钟,下面是 PLLP 的计算方法,其他PLL时钟计算方法类似。 下图是主PLL的时钟图。

从上图可以看出。主 PLL 时钟的时钟源要先经过一个分频系数为 M 的分频器,然后经过倍频系数为 N 的倍频器出来之后还需要经过一个分频系数为P(第一个输出PLLP)或者Q(第二个输出PLLQ)的分频器分频之后,最后才生成最终的主 PLL 时钟。 例如我们的外部晶振选择 25MHz。同时我们设置相应的分频器 M=25,倍频器倍频系数 N=432,分频器分频系数 P=2,那么主PLL 生成的第一个输出高速时钟 PLLP 为: PLL=25MHz * N /(M * P)= 25MHz * 432/(25 * 2)= 216MHz 这个 216MHz 就是我们最高的系统时钟。 如果我们选择 HSE 为 PLL 时钟源,同时 SYSCL K时钟源为 PLL,那么 SYSCLK时钟为 216MHz。 正点原子的实验基本都是采用这样的配置。 4、STM32F7 常用时钟 A ~ R 表示上图中标示的地方。 A、 这是低功耗定时器LPTimer时钟,从图中可以看出,LPTimer有四个时钟源可以选择,分别为LSI、HSI、LSE和PCLKx,默认情况下LPTimer选用PCLKx作为时钟源。 B、 这里是USART时钟源。从图中可以看出,USART 时钟源可选为 LSE、HSI、SYSCLK以及PCLKx,默认情况下USART选用PCLKx作为时钟源。 C、 这里是硬件I2C时钟源,从图上可以看出,I2C可选时钟源为HSI、SYSCLK以及PCLKx。默认情况下I2C选用PCLKx作为时钟源。 D、 这是STM32F7独立看门狗IWDG时钟,来源为LSI。 E. 这里是RTC时钟源,可选LSI、LSE和HSE的2~31分频。 F. 这是SDMMC时钟源,来源为系统时钟SYSCLK或者PLL48CLK,其中PLL48CLK来源为PLLQ或者PLLSAIP。 G、 这是STM32F7输出时钟MCO1和MCO2。MCO1是向芯片的PA8引脚输出时钟。它有四个时钟来源分别为:HSI,LSE,HSE和PLL时钟,MCO1时钟源经过1~5分频后向PA8引脚输出时钟。MCO2是向芯片的PC9输出时钟,它同样有四个时钟来源分别为:HSE,PLL,SYSCLK以及PLLI2S时钟,MCO2时钟源同样经过1~5分频后向PC9引脚输出时钟。 H、 这是系统时钟 SYSCLK时钟源,可选HSI、HSE和PLLCLK。HSI是内部16MHz时钟精度不够,HSE是外部晶振产生时钟频率较低,大部分情况下系统都会选择PLLCLK作为系统时钟。 I、 这是以太网 PTP 时钟,来源为系统时钟 SYSCLK。 J、 这是AHB总线预分频器,分频系数为2(N=0-9)。系统时钟SYSCLK经过AHB预分频器之后产生AHB总线时钟HCLK。 K、 这是APBx预分频器(分频系数可选1,2,4,8,16),HCLK(AHB总线时钟)经过APBx预分频器之后,产生PCLKx。这里大家还要注意,APBx定时器时钟是PCLKx经过倍频后得来,倍频系数为1或者2,如果APBx预分频系数等于1,那么这里的倍频系数为1,否则倍频系数为2。 L-N、 这是PLL时钟。L为主PLL时钟,M为专用PLL时钟PLLI2S,N为专用PLL时钟PLLSAI。主PLL主要用来产生PLL时钟作为系统时钟,同时PLL48CLK时钟也可以选择PLLQ或者PLLSAIP。PLLI2S主要用来为I2S、SAI和SPDIFRX产生精确时钟。PLLSAIP则为SAI接口生成时钟,生成LCD-TFT时钟以及可供USB OTGFS、SDMMC和RNG选择的48MHz时钟PLL48CLK。 O、 这是SPDIFRX时钟,由PLLI2SP提供。 P、 这是LCD-TFT时钟,由PLLSAIP提供。 Q、 这是STM32F7内部以太网MAC时钟的来源。对于MI接口来说,必须向外部PHY芯片提供25Mhz的时钟,这个时钟,可以由PHY芯片外接晶振,或者使用STM32F7的MCO输出来提供。然后,PHY芯片再给STM32F7提供ETH MII TX CLK和ETH MIIRXCLK时钟。对于RMII接口来说,外部必须提供50Mhz的时钟驱动PHY和STM32F7的ETHRMILREFCLK,这个50Mhz时钟可以来自PHY、有源晶振或者STM32F7的MCO。我们的开发板使用的是RMIⅡ接口,使用PHY芯片提供50Mhz时钟驱动STM32F7的ETH RMIIREFCLK。 R、 这里是指外部PHY提供的USB OTG HS(60MHZ)时钟。 5、STM32F7 总线时钟APB1和APB2 APB1和APB2都是总线时钟,一个是高速时钟,一个是低速时钟;他们下面挂的外设不同,因为不同的外设需要的时钟不同。 APB2是高速时钟,负责AD,I/O,串口1,高级定时器TIM; APB1是低速时钟负责DA,串口2,3,4,5,普通定时器TIM, USB , IIC , CAN; APB1和APB2的配置如下图所示:

6、STM32F7 ADC时钟配置 6.1、ADC的最大工作频率 STM32F767IGT6包含有3个ADC。 STM32F767的ADC最大的转换速率为2.4Mhz,也就是转换时间为0.4lus(在ADCCLK=36M,采样周期为3个ADC时钟下得到),不要让 ADC 的时钟超过36M,否则将导致结果准确度下降。 STM32F767的ADC最大工作频率是 36 Mhz,而ADC时钟(ADCCLK)来自APB2,APB2 频率一般是 108Mhz。 ADC的工作频率主要通过通用控制寄存器 ADC_CCR 配置: 下图是我从STM32F7中文参考手册中截取出来的。

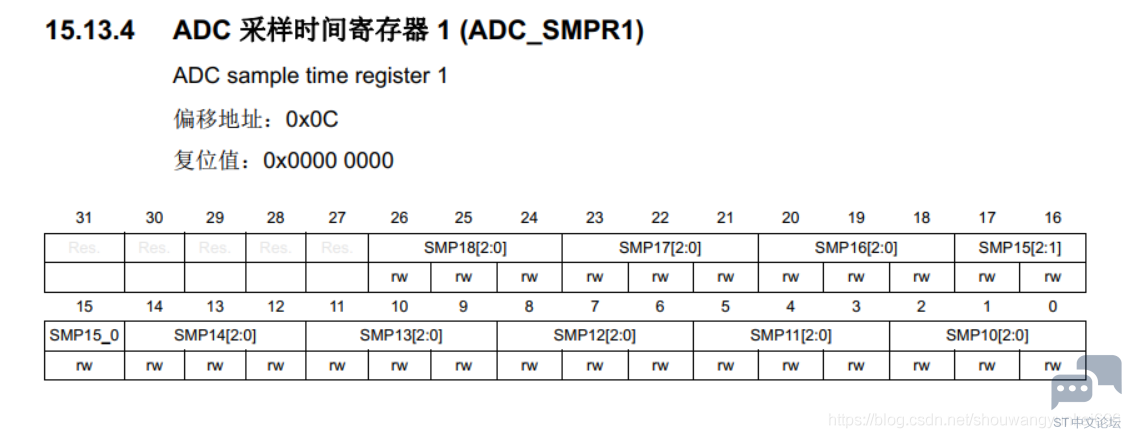

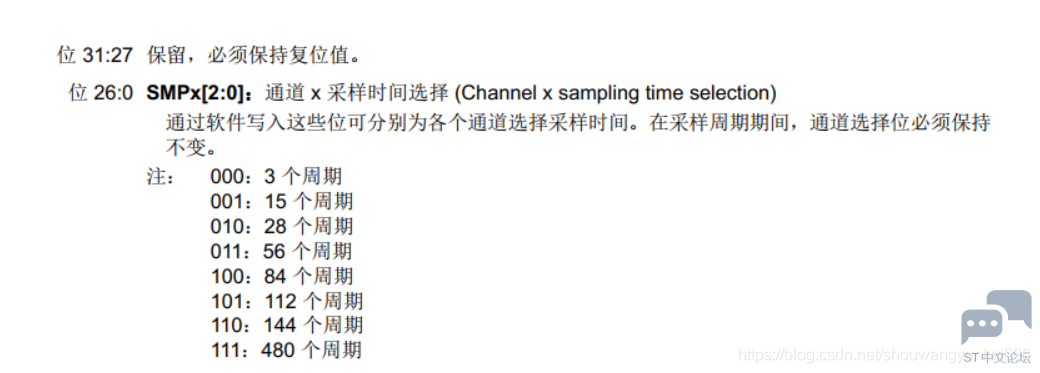

我们一般采用 4 分频配置ADC频率,得到ADC最大工作频率为 27 MHz。 6.2、ADC的采样频率 ADC的采样时间由 ADC 采样时间寄存器(ADC_SMPR1和ADC_SMPR2)控制。

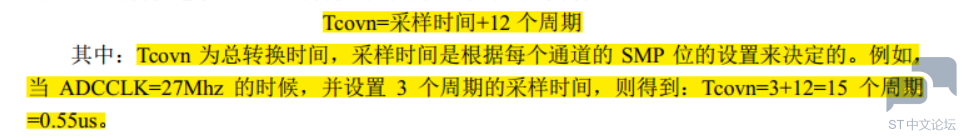

寄存器 ADC_SMPR2 与 ADC_SMPR1 类似。 ADC的转换时间:

所以,ADC 的采样频率是:

以上主要是参考正点原子的资料,如有问题,欢迎指正。 |

STM32F745 USART1 Bootloader启动失败排查与解决的流程分析

STM32芯片命名规则

STM32 引脚到底有多少?为什么一个引脚能当好几个用?

入门嵌入式,为什么STM32是“优选起步”?

嵌入式-单片机-STM32 EXTI中断

STM32单片机进行除零运算,为何程序不崩溃?

STM32 LL为什么比HAL高效?

STM32时钟详解

2025国庆中秋活动体验报告2——TouchGFX的UI设计

2025国庆中秋活动体验报告1——TouchGFX环境配置

微信公众号

微信公众号

手机版

手机版