|

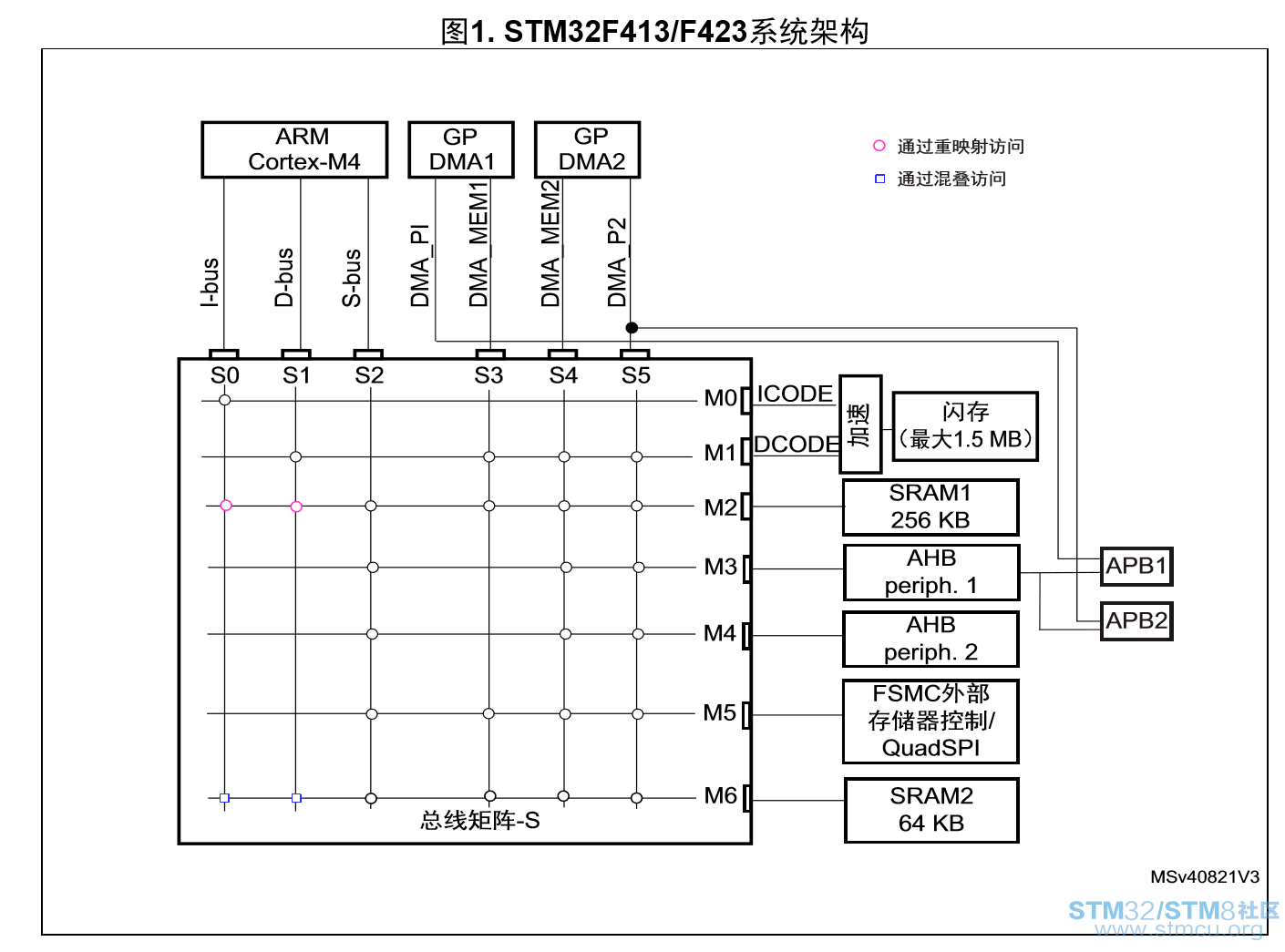

AN5024:如何利用STM32F413/F423系列SRAM的性能优势 数据摘要 前言 在嵌入式设计中,对大量数据的需求不断增加。存储器(特别是RAM)已成为十分宝贵的资 源,了解该存储器的最佳使用方式是获得最佳性能的关键所在。 本应用笔记旨在帮助用户通过研究不同场景,从STM32F413/F423微控制器的更高SRAM性能 和更低功耗中获益。 主要目标是介绍架构设计和系统模块功能,可以对它们进行调整以优化应用。 1 STM32F413/F423系统架构概述 优化系统性能的第一步是了解系统的高层架构。 图 1显示了STM32F4系列的简化框图。

1.1 STM32F413/F423内核总线 STM32F413/F423器件基于带有FPU(浮点单元)内核的Cortex®-M4内核,它使用哈佛体系 结构,结合存储器映射总线。 总线矩阵提供从主设备到从设备的访问,可实现并发访问和高效运行。 • I-bus:内核用来从包含代码的存储器(内部闪存/SRAM)取指令的指令总线。 • D-bus:内核用来进行文字加载和对/从包含代码或数据的存储器(内部闪存/SRAM)进 行调试访问的数据总线。 • S-Bus:内核用来访问外设或SRAM中数据的系统总线。也可通过该总线取指令。该总线 的访问目标是内部SRAM,AHB 1外设包括APB外设和AHB2外设。 1.2 嵌入式SRAM STM32F413/F423具有320 K字节SRAM。 该内置SRAM分为两块: • 映射到地址0x2000_0000的SRAM1,所有AHB主设备均可访问。 • 映射到地址0x2004_0000的SRAM2,所有AHB主设备均可访问。 在STM32F413/F423中,可按以下方式访问SRAM2: • 可通过I-Code总线取指令。通过D-Code总线执行数据访问。 • 可通过系统总线取指令和访问数据。 • 数据访问是别名。指令访问不是别名。 独立总线在加载或存储指令时十分有用,因为可以同时取指令和访问数据,无需插入总线矩 阵仲裁。 当SRAM2被映射到地址范围0x1000 0000至0x1000 FFFF时,CPU可通过I-bus和D-bus访问 SRAM2存储器。 系统总线的访问周期时间取决于访问类型: • 系统总线数据访问不会增加内核的延时。 • 指令访问会增加一个等待状态的内核延时。 将代码和数据存入两个SRAM块有助于提高并行能力和整体性能。 注: 对于典型应用,通过在SRAM2中插入关键代码和在SRAM1中插入数据和堆栈可获得最佳性 能。 ...................... 阅读更多内容,请下载文档 下载地址1>>下载地址2>> 更多中文文档>> |

微信公众号

微信公众号

手机版

手机版