|

大家好,最近在使用STM32L451VET6时发现如下情况,请帮忙 在STM32L451VET6中使用MSI(默认4M)时钟提供系统时钟,发现串口波特率紊乱引起数据通信问题。经过阅读RM0349资料,发现MSI时钟有硬件校准机制,如下,我的理解是当使能LSE,通过配置RCC_CR寄存器位MSIPLLEN位,使MSI处于PLL模式时,会开启自动校准,这个校准会一直持续。 RM0394关于MSI硬件校准的描述

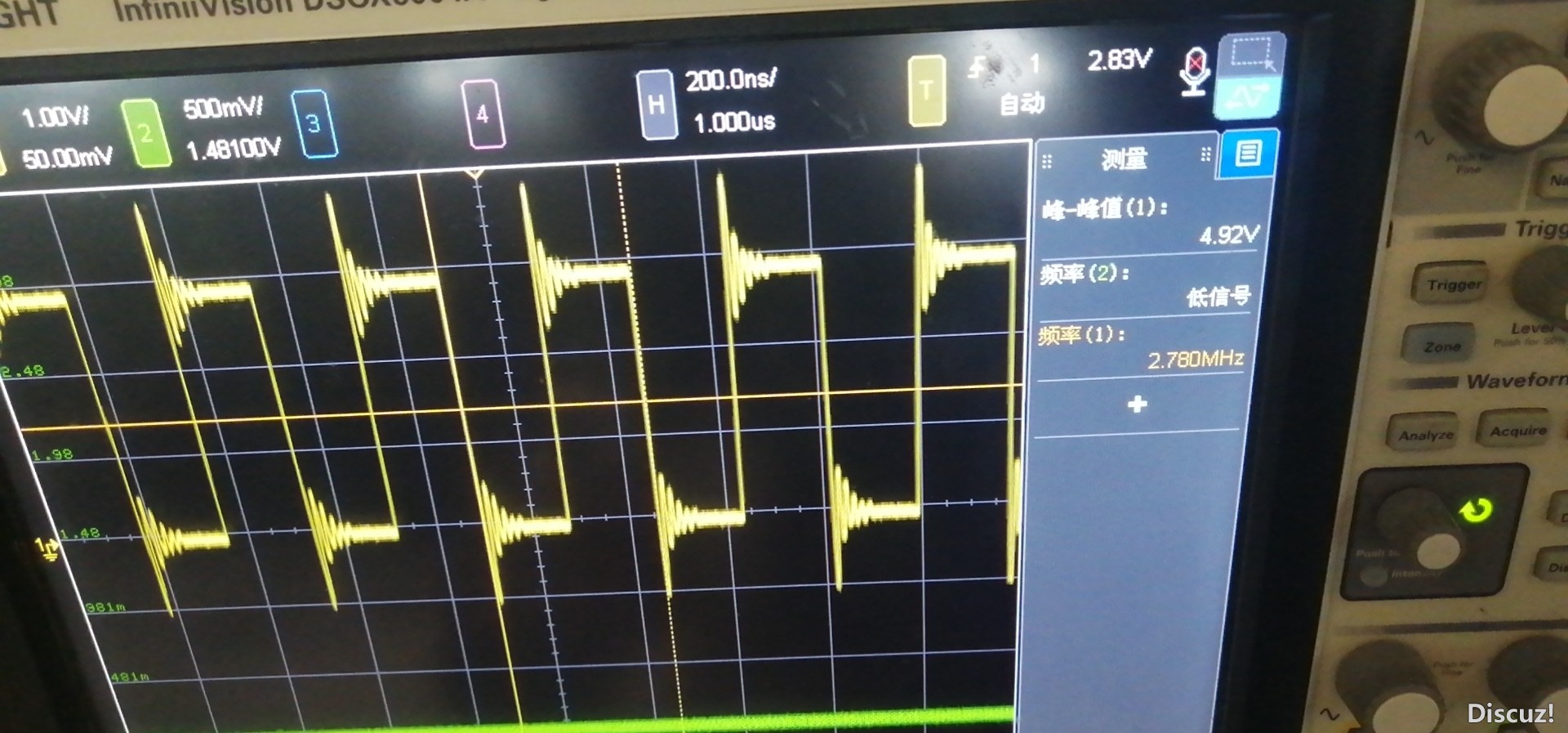

在我的应用中,发现一个问题, 在我的IAP最小系统中,使用MSI(4MHz)作为系统时钟,未使能LSE,但是OSC32引脚上有8KLSE时钟信号,此时PA8的MCO输出MSI时钟为2.780MHz,即MSI时钟信号发生了变化; MSI时钟信号

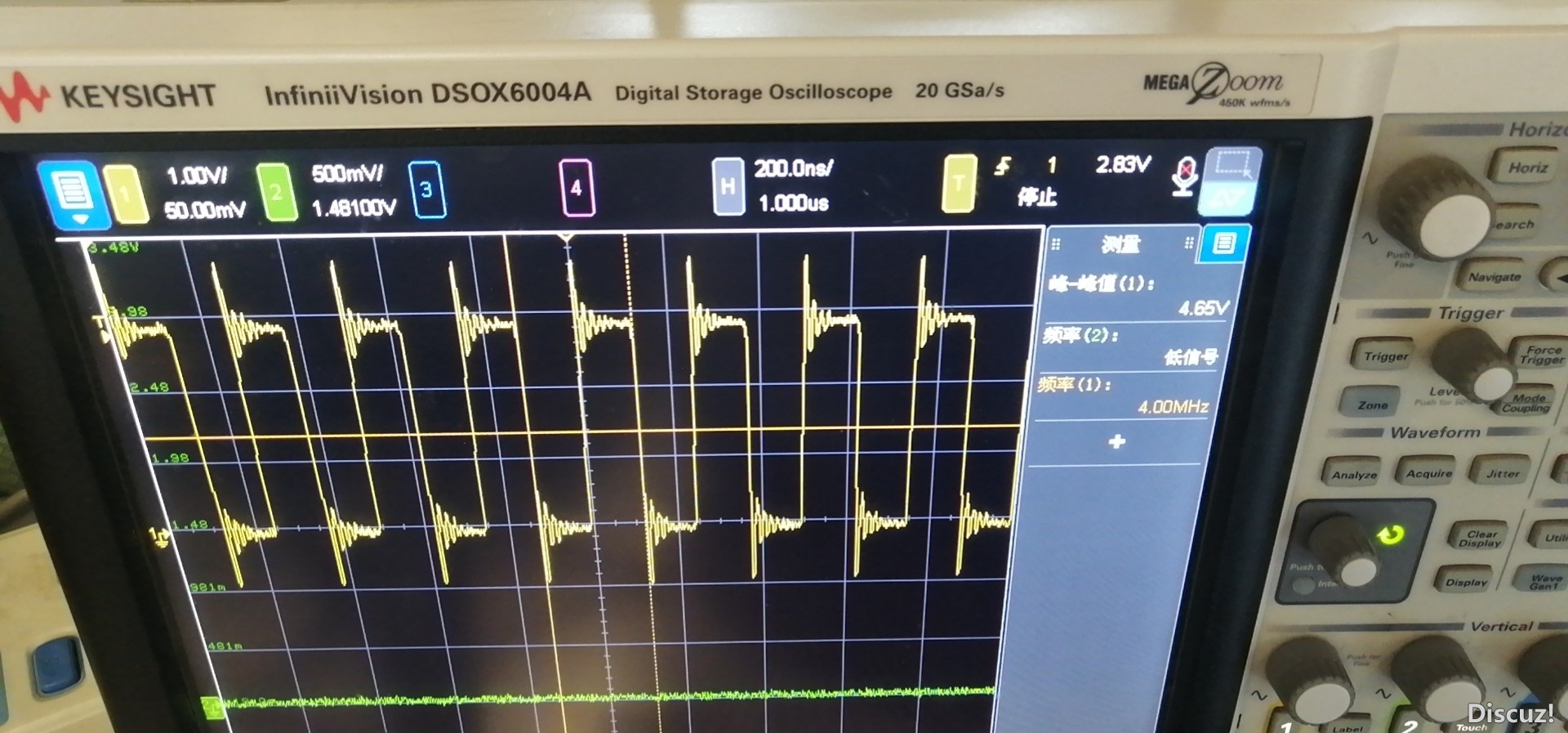

在进入APP程序后,使能LSE,此时LSE的时钟信号依然为8K,再次测试PA8的MCO,输出MSI时钟为4M,此时MSI时钟信号恢复到4MHz; MSI时钟信号

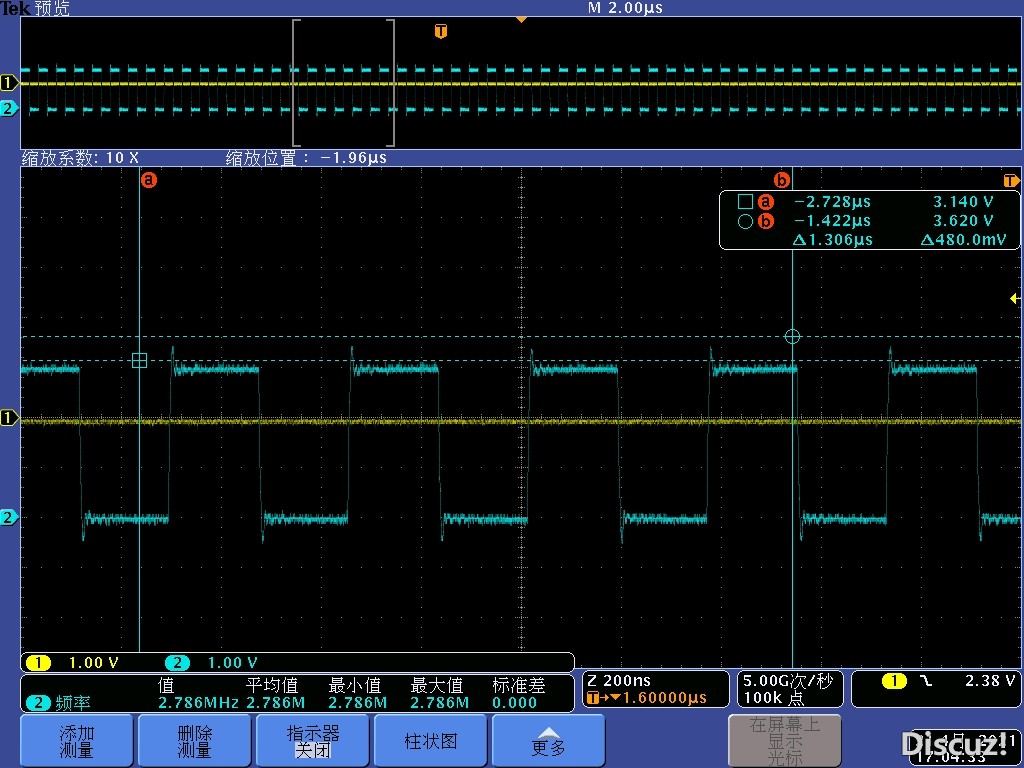

针对此现象我咨询ST相关的FAE,给出解释是当LSE使能后,MSI就会一直校准,且当LSE时钟不为32.768K的时候,PLL锁相环是不工作的。 为排除IAP与APP跳转产生的干扰,我对此我做了如下实验: 1、系统时钟由MSI提供(4Mhz),未使能LSE,但OSC32的引脚上提供的了一个8K的时钟信号,通过PA8的MCO功能输出MSI为2.786MHz,如下: LSE

MSI

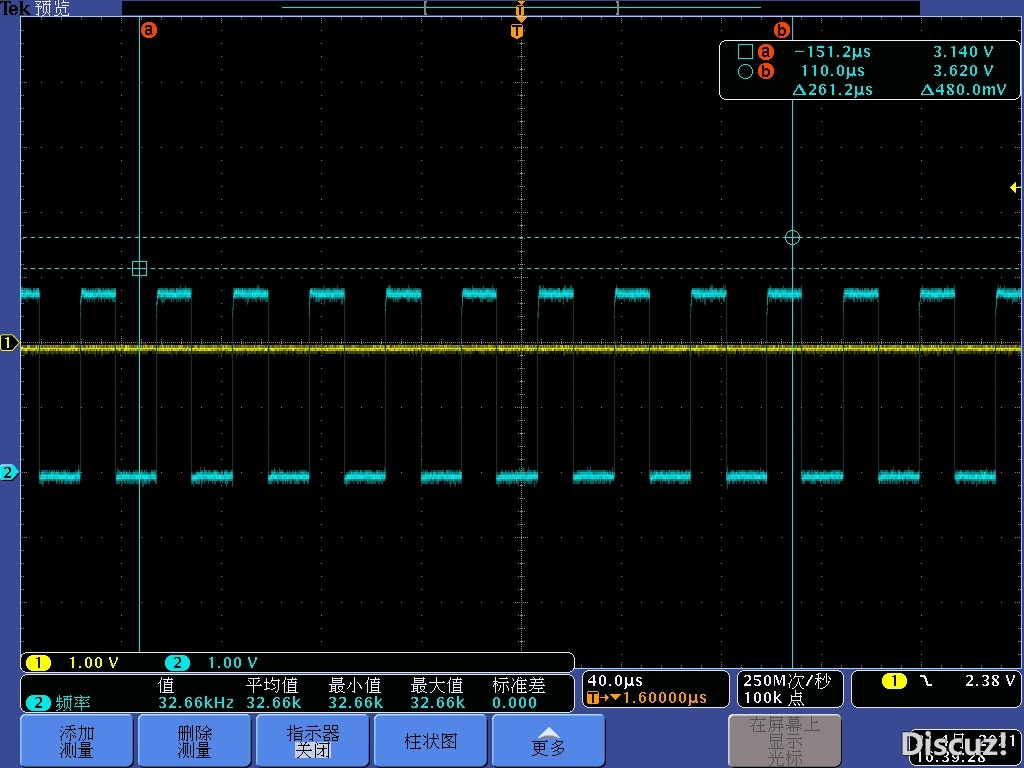

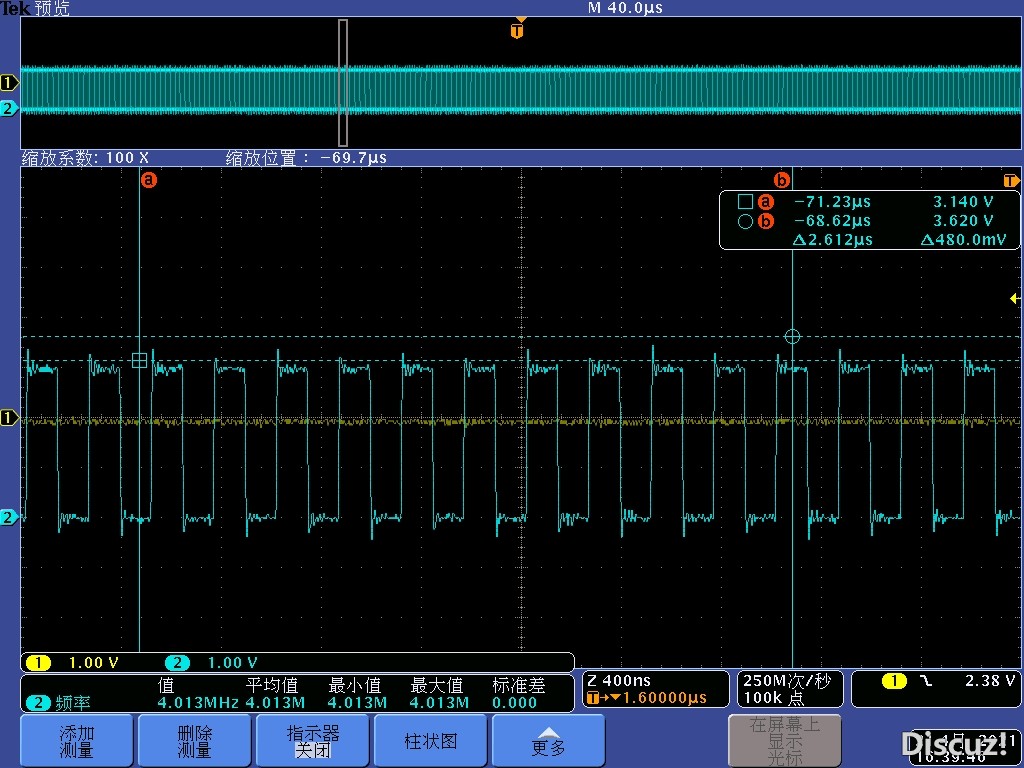

2、系统时钟由MSI提供(4Mhz),未使能LSE,但OSC32的引脚上提供的了一个32.66K的时钟信号,通过PA8的MCO功能输出MSI为4.013MHz,如下: LSE

MSI

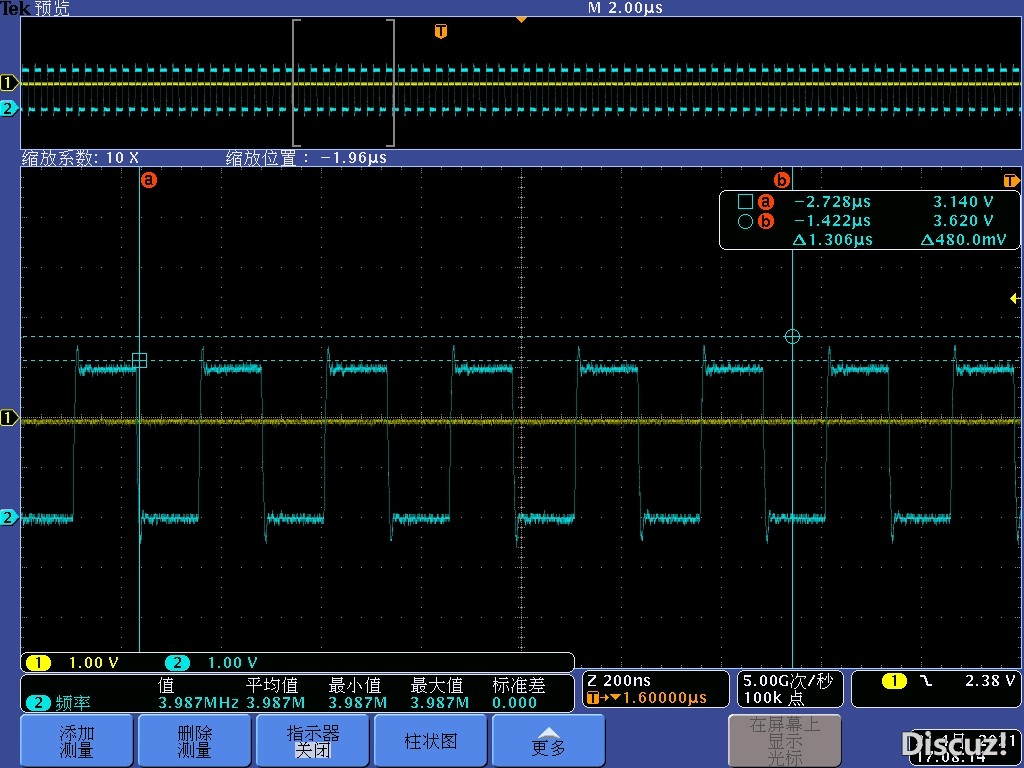

3、系统时钟由MSI提供(4Mhz),硬件上断开OSC32与时钟信号之间的通路,通过PA8的MCO功能输出MSI为3.987MHz,如下: MSI

针对我的现象,我的疑问在于,LSE和MSI的校准存在一个什么关系,才会导致硬件上给LSE提供一个不为32.768K的信号且软件上不使能LSE的情况下,影响到MSI时钟的精度,请教给位技术大佬帮忙分析,谢谢! |

串口DMA收发出现ORE错误

STM32U5系列上电时序

STM32L476项目运行提示没有crypto.h

STM32生产产地和版本

50台设备共用一条CAN总线,会概率性丢包

STM32L431CCT6芯片的ADC差分采集

stm32l4R7ZI的uart4在stop2模式下唤醒偶发数据接收丢失或者乱码

smt32l432kcu6 TIM_DMA 例程,TimHandle.Init.RepetitionCounter = 3; 应该输出4个波形,但是启动时第一次会输出8个波形后面才会正常输出4个波形

motor profiler 链接nucleo 476rg时提示如图所示的通信错误,此时未连接IHM08M1,电脑上有476RG产生的串口,STLINK,U盘标识

STM32L496要加热才能运行

微信公众号

微信公众号

手机版

手机版

如果说你选择MSI作为PLL的时钟源,将MSI配置在PLL-Mode上,二者才会有关联。硬件会自动基于LSE对MSI进行校准操作。

当然,MSI本身也可以直接作为系统时钟。