|

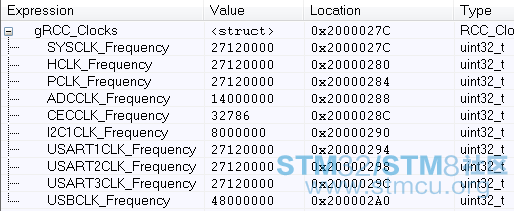

本帖最后由 donsbin 于 2017-8-21 21:36 编辑 外挂8M的晶振,锁相环通过HSE一分频然后倍频。 通过RCC_GetClocksFreq(&gRCC_Clocks);接口读取时钟信息。 论坛下的DEMO 通过IAR编译DEBUG读取数据如下,主频变成了13.5M的了

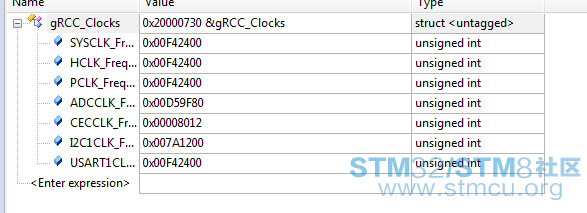

然后我又用MDK DEBUG了下,16M。正常了

是不是我IDE配置问题??  |

|

这好像这不是标准库,也不是HAL库啊,眼生。 |

|

| 标准库也试过了,一模一样 |

调试时出现 HardFault_Handler 问题该如何解决?

stm32 数据掉电保存问题

手动按键复位可以保存变量, 但是断电马上上电却不能了. 有什么办法可以解决吗?

RST问题请教

HAL_I2C_Mem_Read_IT读取INA226多个寄存器只有第一个寄存器是对的,其他全为0XFF

stm32电源部分

ST MotorControl Workbench 生成代码过程中报错Java的非法反射警告

HAL_TIM_IC_Start_DMA的回调函数是HAL_TIM_IC_CaptureCpltCallback吗?为什么进不去?

方波控制,光标这一段,相电流为啥上升了,之前怀疑是这个时候,同时开了三个MOS管,但实测波形,跟段波形有点滞后,而且时间也没那么长。

请问大家有没有遇到过芯片内存的数据和下载的不一样的?

微信公众号

微信公众号

手机版

手机版