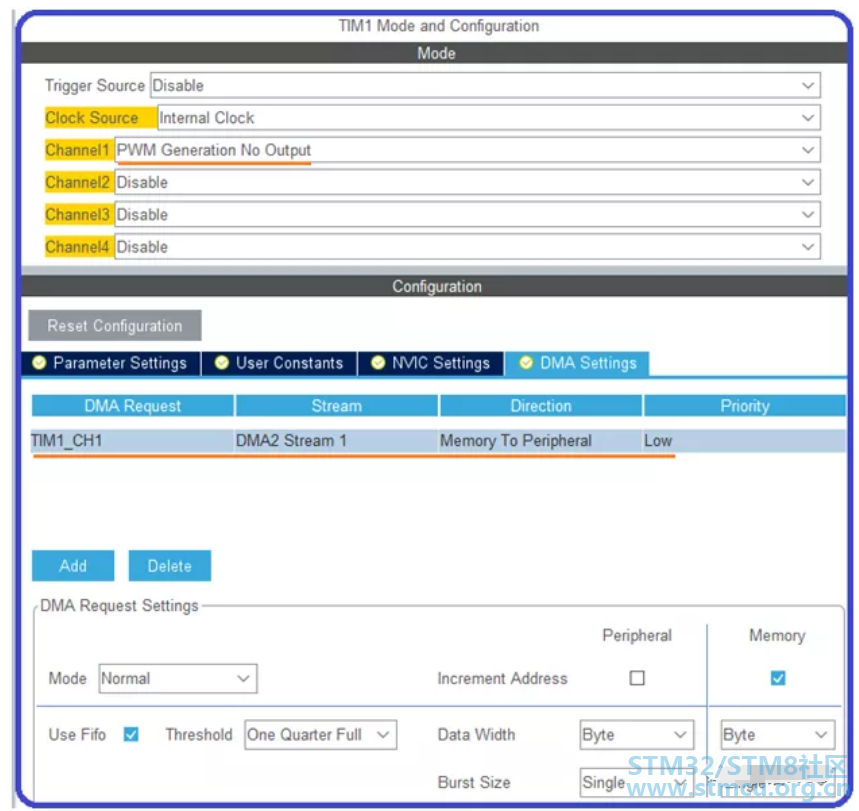

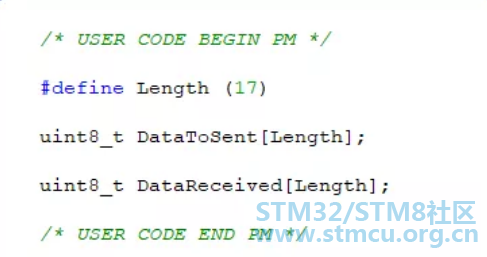

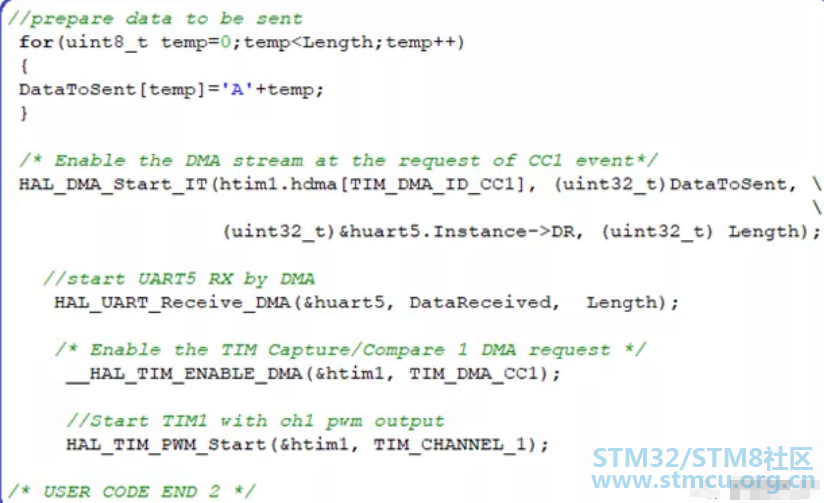

大致情况是这样的,我用TIMER1通道1的比较事件触发DMA,将内存数据写进UART5的数据发送寄存器DR,并将UART5的TX/RX脚物理短接,同时开启UART5的DMA接收模式,即DMA将UART5接收到的数据写到指定的接收内存区。下面重点介绍UART5的DMA方式的接收过程。 首先使用STM32CubeMx完成基本配置。 下面是关于TIM1的相关配置,使用通道1的比较事件触发DMA,将内存数据写入UART的发送数据寄存器。为什么还要搞个定时器来触发,其中一个原因是为了后面好演示结果。

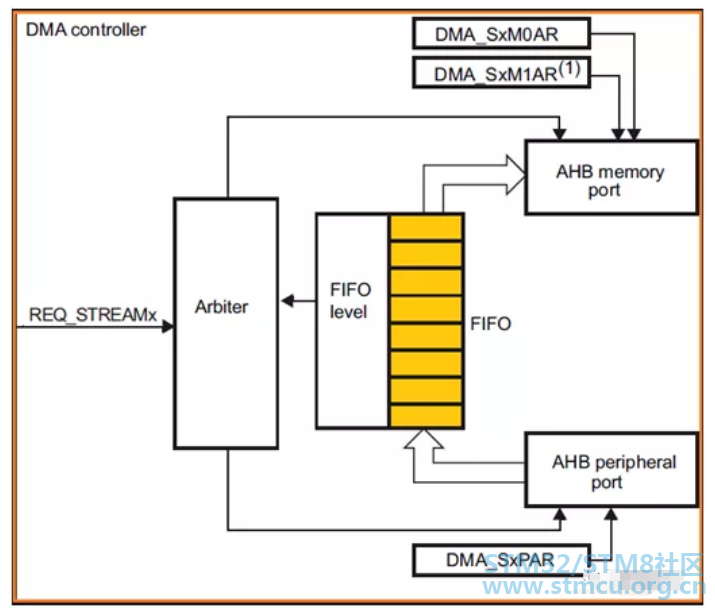

对于STM32F4来讲,每个DMA stream都有4个字的FIFO可用。它用来暂存来自DMA源端的数据,每当FIFO里存放的数据达到设定的阈值后,数据就会被移走。阈值可以设置为从1个字到4个字的深度。

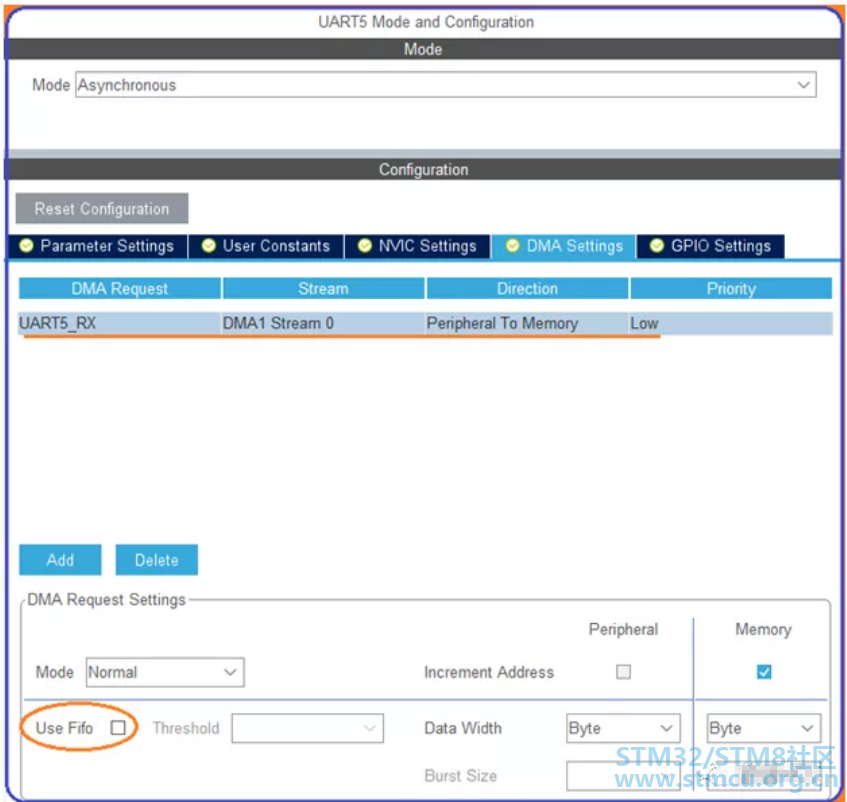

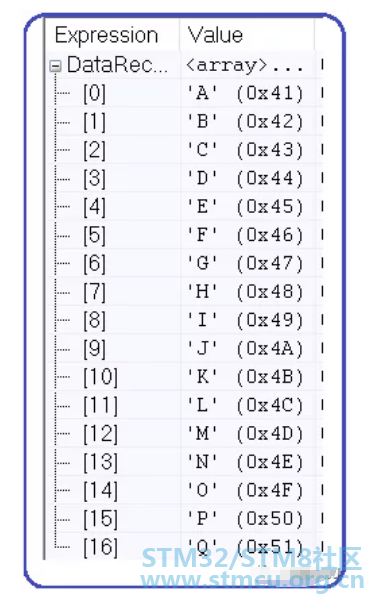

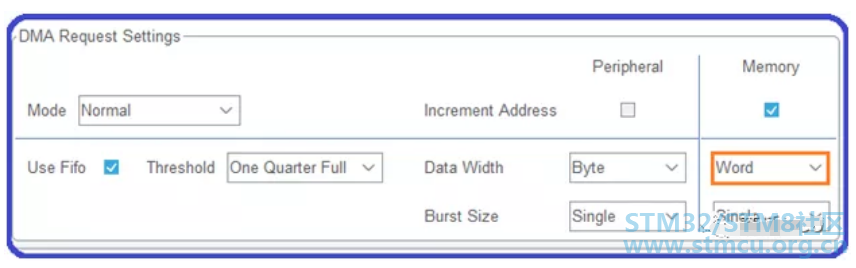

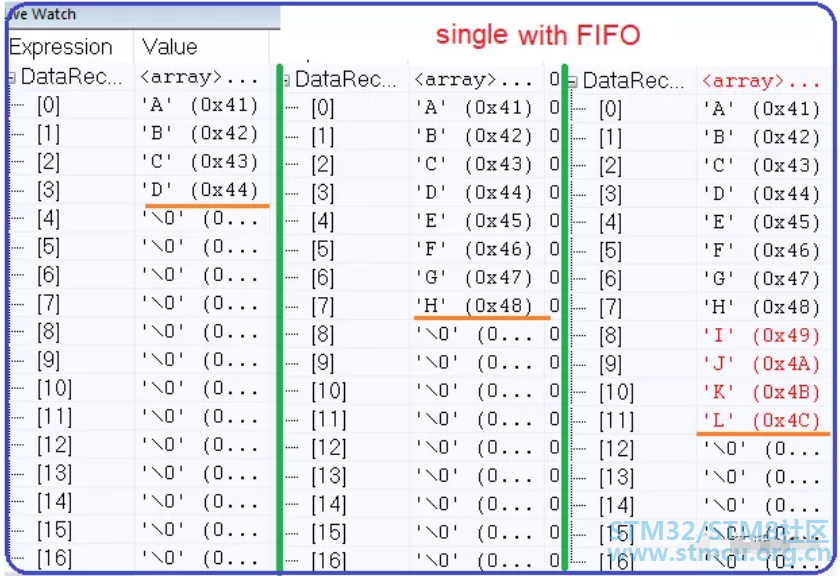

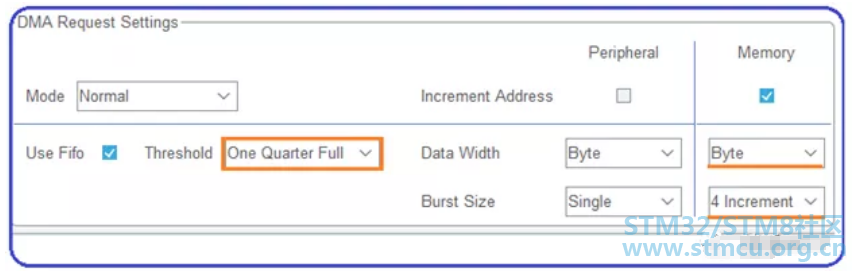

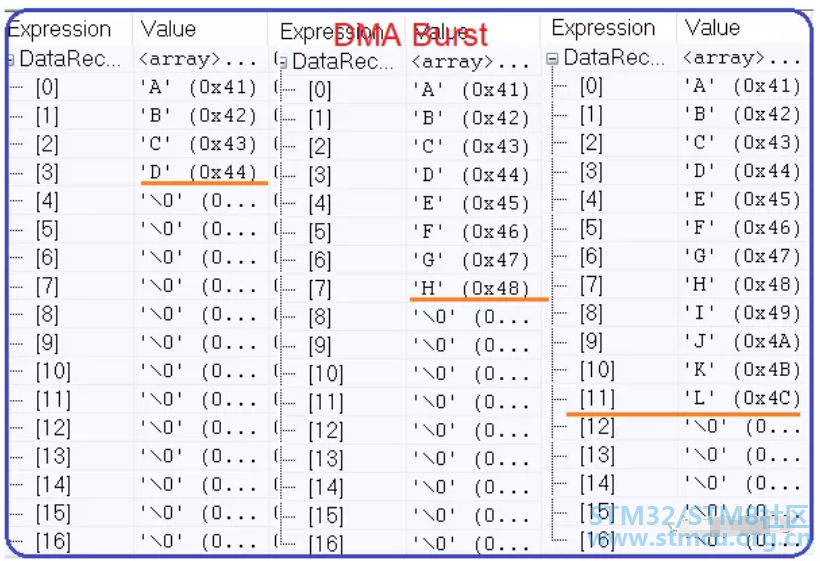

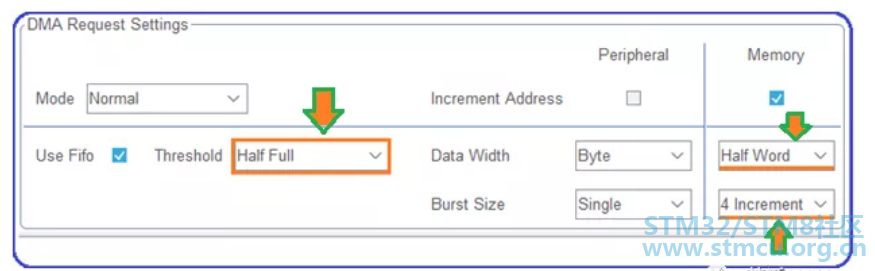

这里以UART5的数据接收为例。当启用FIFO时,目的端数据宽度可以从字节/半字/字格式自由设置。首先,当UART5的DMA接收配置成下面这样时,即DMA single模式。

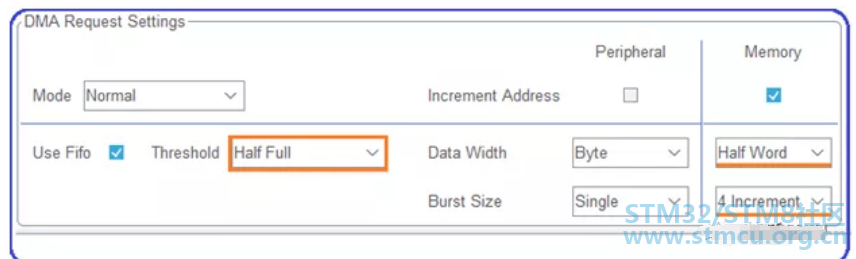

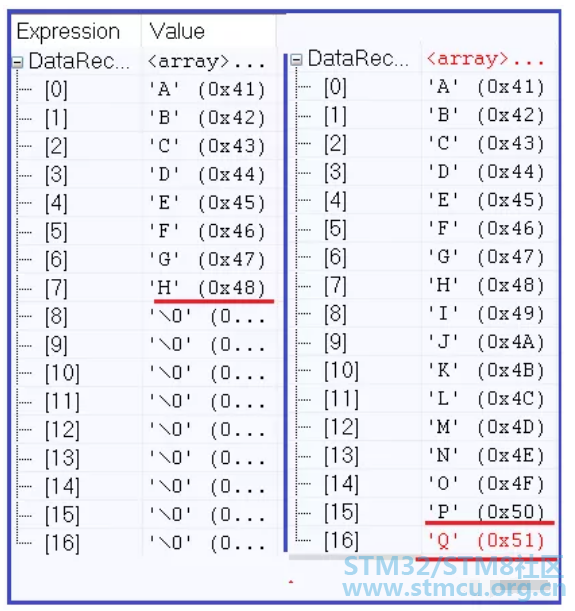

我们还是以上面的应用为例,调整配置并开启BURST模式后具体看看。

本文主要基于带FIFO的DMA传输的实现做了简单而比较直观的演示,顺便对DMA的burst传输做了些简单介绍,更多细节需阅读STM32参考手册相关内容。相信具体的实现示例配合技术手册阅读理解后再运用起来会更加得心应手。 文章出处:茶话MCU |

无刷直流电机控制应用+基于STM8S系列单片机---电子书

MCSDK FOC应用详解

STM32F10xxx 正交编码器接口应用笔记 及源代码

基于STM32定时器ETR信号的应用示例

《无刷直流电机控制应用 基于STM8S系列单片机》

STM32定时器触发SPI逐字收发之应用示例

【银杏科技ARM+FPGA双核心应用】STM32H7系列10——ADC

【银杏科技ARM+FPGA双核心应用】STM32H7系列57——MDK_FLM

【STM32图书分享之九】—《STM32F 32位ARM微控制器应用设计与实践》

STM32 USB的程序,包含固件、驱动和测试用的应用程序

微信公众号

微信公众号

手机版

手机版