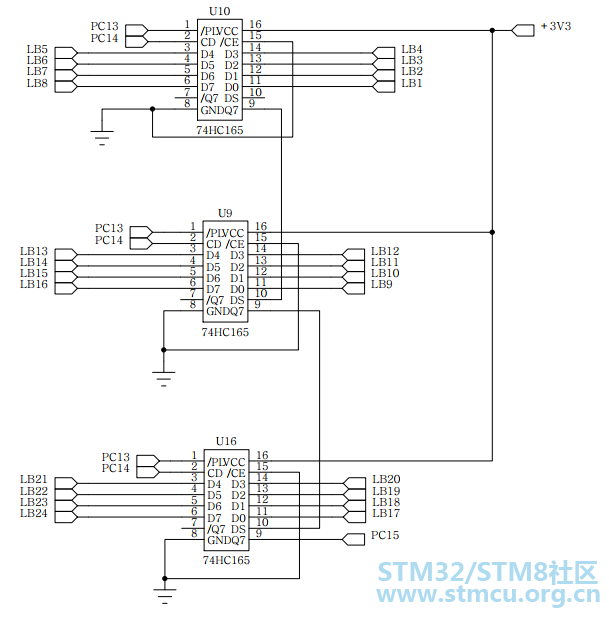

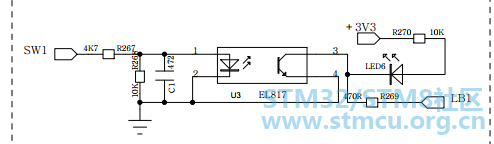

电路图部分:

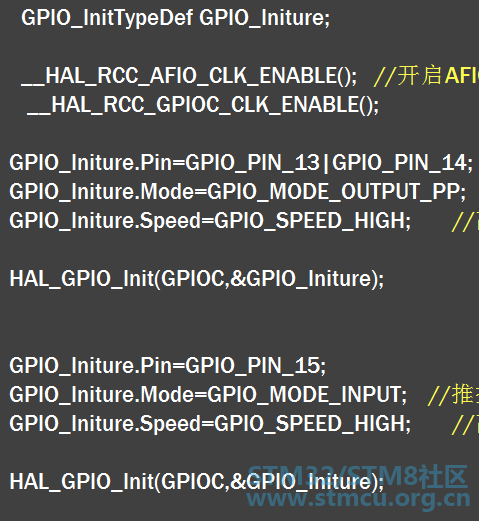

软件部分:

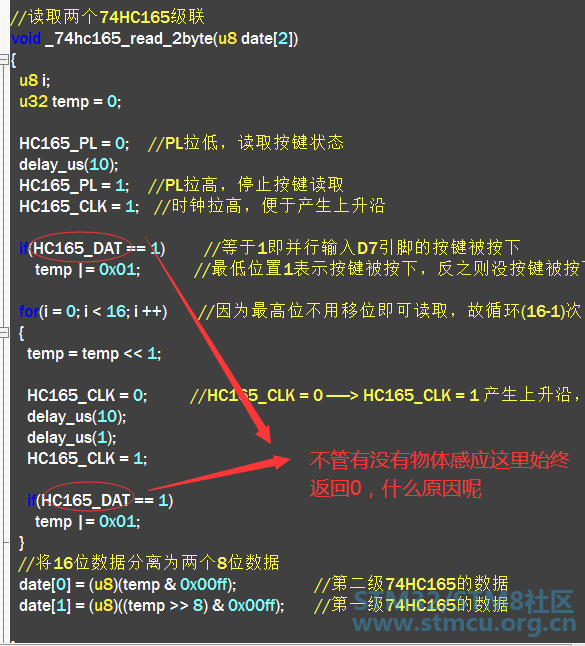

#define HC165_PL PCout(13) //pl #define HC165_CLK PCout(14) //cp #define HC165_DAT HAL_GPIO_ReadPin(GPIOC,GPIO_PIN_15) //Q7 探物传感器的状态是:电平为高(没有物品) 低电平(有物品) 各位大佬帮看看什么原因 |

要在STM32F103C8T6上实现TIM+DMA+ADC采集电压,cubemx配置为什么,代码怎么写

PCF8563(RTC)读取时间有误

pwm关闭输出

VL53L5CX无法使用

请教STM32F103的DMA空闲接收问题

3.3v单片机能刷写1.8v的spi flash吗?

STM32CubeMX配置STM32F103C8T6 RTC分频器问题

STM32F103RCT6断电以后,ADC会漏电

STM32F103VCT6通过串口1烧录程序问题

F103的IIC支持高速400K频率吗?

微信公众号

微信公众号

手机版

手机版

2. 你确定你那个for循环中CLK的波形没问题? CLK拉高之后稍微延时一下

会不会是 AFIO 设定接脚, 没切换到 GPIO?

会不会是 AFIO 设定接脚, 没切换到 GPIO?