.png) STMCU小助手

发布时间:2021-12-11 12:00

STMCU小助手

发布时间:2021-12-11 12:00

|

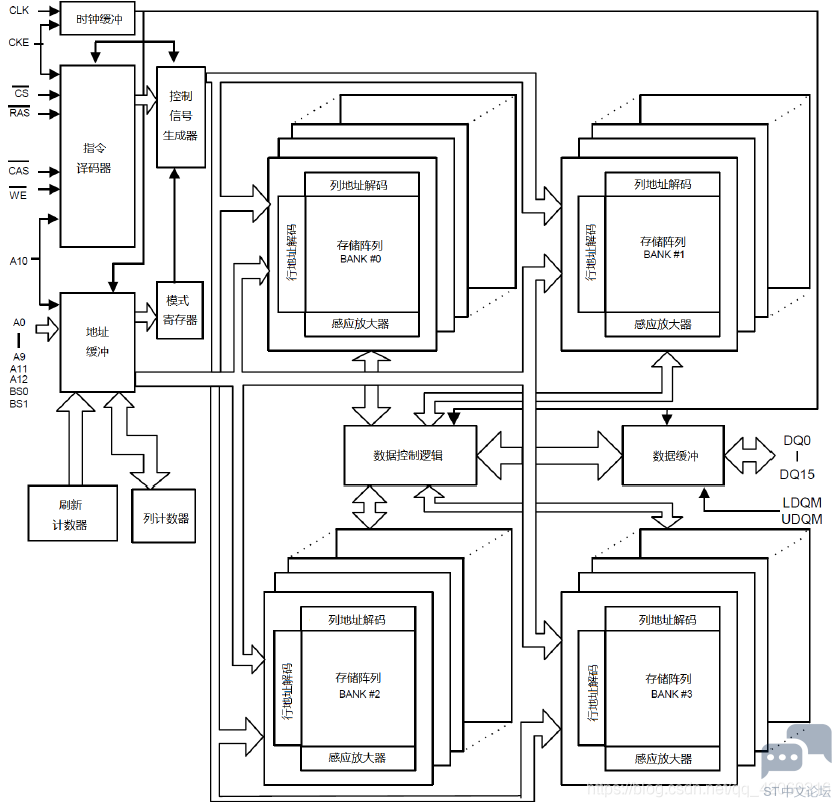

SDRAM SDRAM英文名是 Synchronous Dynamic Random Access Memory ,即同步动态随机存储器,相较于 SRAM(静态存储器) SDRAM 具有:容量大和价格便宜的特点。 STM32F767 支持 SDRAM ,我们可以外挂 SDRAM ,从而大大降低外扩内存的成本,如下SDRAM 型号为: W9825G6KH 的结构框图。

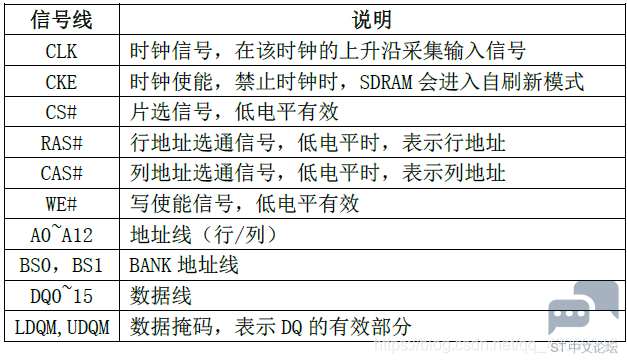

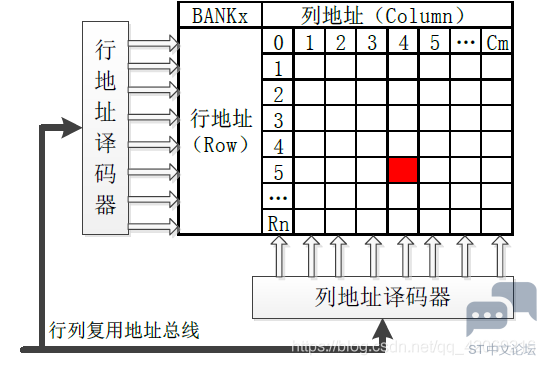

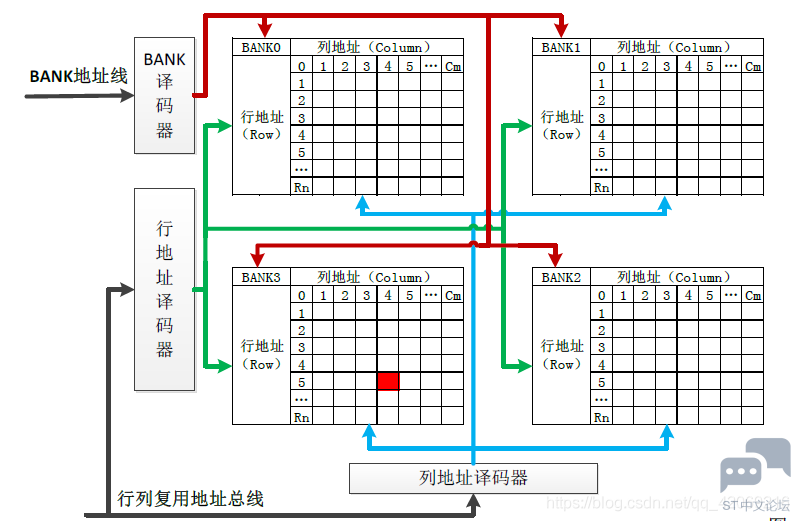

一个SDRAM 芯片内部,一般又有4 个存储单元(BANK),所以,在SDRAM 内部寻址的时候,先指定BANK 号和行地址,然后再指定列地址,就可以查找到目标地址。 SDRAM信号线 寻址的时候,首先RAS 信号为低电平,选通行地址,地址线A0~A12 所表示的地址,会被传输并锁存到行地址译码器里面,最为行地址,同时BANK地址线上面的BS0,BS1 所表示的BANK地址,也会被锁存,选中对应的BANK,然后,CAS 信号为低电平,选通列地址,地址线A0~A12 所表示的地址,会被传输并锁存到列地址译码器里面,作为列地址,这样,就完成了一次寻址。

存储单元

存储结构 W9825G6KH 的存储结构为:行地址:8192 个;列地址:512 个;BANK 数:4 个;位宽:16 位;这样,整个芯片的容量为:81925124*16=32M 字节。

数据传输 在完成寻址以后,数据线DQ0~DQ15 上面的数据会通过数据控制逻辑写入(或读出)存储阵列。 特别注意:因为SDRAM 的位宽,可以达到32 位,也就是最多有32 条数据线,在实际使用的时候,我们可能会以:8 位、16 位、24 位和32 位等宽度来读写数据,这样的话,并不是每条数据线,都会被使用到,未被用到的数据线上面的数据,必须被忽略,这个时候就需要用到数据掩码DQM 线来控制了,每一个数据掩码线,对应8 个位的数据,低电平表示对应数据位有效,高电平表示对应数据位无效。 W9825G6KH中,假设以8 位数据访问,我们只需要DQ0 ~DQ7 的数据,而DQ8~DQ15的数据需要忽略,此时,我们只需要设置LDQM 为低电平,UDQM 为高电平,就可以了。 控制命令

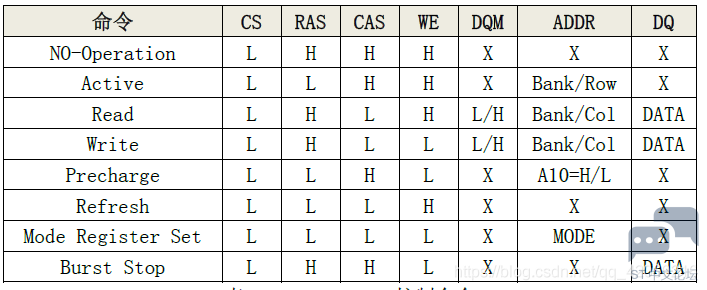

空操作命令 NO-Operation,空操作命令,用于选中SDRAM,防止SDRAM接受错误的命令,为接下来的命令发送做准备。 激活命令 Active,激活命令,该命令必须在读写操作之前被发送,用于设置所需要的Bank和行地址(同时设置这2个地址),Bank地址由BS0,BS1(也写作BA0,BA1,下同)指定,行地址由A0~A12指定 读写命令 Read/Write,读/写命令,在发送完激活命令后,再发送列地址就可以完成对SDRAM的寻址,并进行读写操作了,读/写命令和列地址的发送,是通过一次传输完成的。列地址由 A0~A9 指定, WE 信号控制读 写命令,高电平表示读命令,低电平表示写命令。 预充电命令 Precharge,预充电指令,用于关闭Bank中所打开的行地址。由于SDRAM的寻址具体独占性,所以在进行完读写操作后,如果要对同一Bank的另一行进行寻址,就要将原来有效(打开)的行关闭,重新发送行/列地址。Bank关闭现有行,准备打开新行的操作就叫做预充电(Precharge)。 预充电命令可以通过独立的命令发送,也可以在每次发送读 写命令的时候,使用地址线A10 ,来设置自动预充电。在发送读 写命令的时候,当 A10=1 ,则使能所有 Bank 的预充电,在读 写操作完成后,自动进行预充电。这样,下次读 写操作之前,就不需要再发预充电命令了,从而提高读 写速度。 刷新命令 Refresh,刷新命令,用于刷新一行数据。SDRAM里面存储的数据,需要不断的进行刷新操作才能保留住,因此刷新命令对于SDRAM来说,尤为重要。预充电命令和刷新命令,都可以实现对 SDRAM 数据的刷新,不过预充电仅对当前打开的行有效(仅刷新当前行),而刷新命令,则可以依次对所有的行进行刷新操作。 总共有两种刷新操作:自动刷新(Auto Refresh )和自我刷新 (Self Refresh ),在发送 Refresh 命令时,如果 CKE 有效(高电平),则使用自动刷新模式,否则使用自我刷新模式。不论是何 种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。 自动刷新:SDRAM 内部有一个行地址生成器(也称刷新计数器)用来自动 的依次生成要 刷新的行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址。刷新涉及到所有 Bank ,因此在刷新过程中,所有 Bank 都停止工作,而每次刷新所占用的时间为 9 个时钟周期 PC133 标准),之后就可进入正常的工作状态,也就是说在这 9 个时钟期间内,所有工作指 令只能等待而无法执行。刷新操作必须不停的执行,完成一次所有行的刷新所需要的时间,称 为刷新周期,一般为 64ms 。显然,刷新操作肯定会对 SDRAM 的性能造成影响,但这是没办法 的事情,也是 DRAM 相对于 SRAM (静态内存,无需刷新仍能保留数据)取得 成本优势的同 时所付出的代价。 自我刷新:主要用于休眠模式低功耗状态下的数据保存,在发出自动刷新命令时,将CKE置于无效状态(低电平),就进入了自我刷新模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在自我刷新期间除了CKE 之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使 CKE 有效(高电平)才能退出自刷新模式并进入正常操作状态。 设置模式寄存器命令 Mode Register Set,设置模式寄存器命令。SDRAM芯片内部有一个逻辑控制单元,控制单元的相关参数由模式寄存器提供,我们通过设置模式寄存器命令,来完成对模式寄存器的设置,这个命令在每次对SDRAM进行初始化的时候,都需要用到。

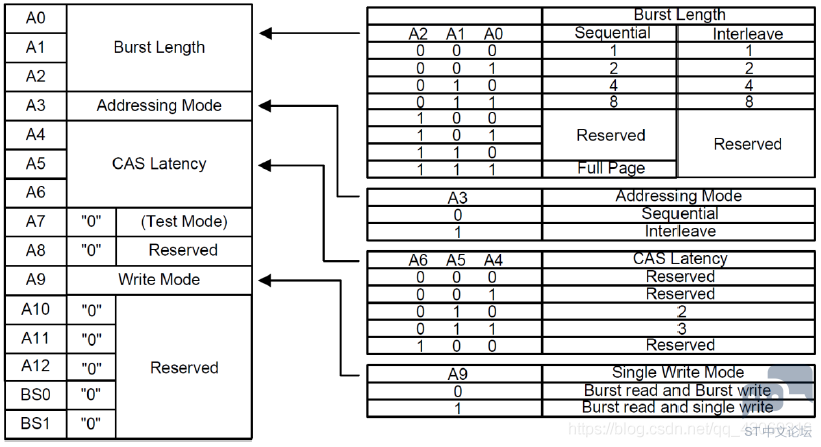

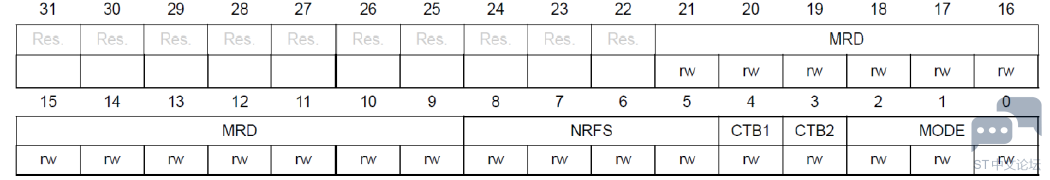

Burst Length突发长度模式(简称 BL ),通过 A0~A2 设置, 是指在同一行中相邻的存储单元连 续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度。 前面我们说的读写操作,都是一次对一个存储单元进行寻址,如果要连续读 写就还要对当前存储单元的下一个单元进行寻址,也就是要不断的发送列地址与读 写命令(行地址不变,所以不用再对行寻址)。虽然由于读 写延迟相同可以让数据的传输在 I/O 端是连续的,但它占用了大量的内存控制资源,在数据进行连续传输时无法输入新的命令,效率很低 。 为此,人们开发了突发传输技术,只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读 写操作而不再需要控制器连续地提供列地址。 这样,除了第一个数据的传输需要若干个周期外,其后每个数据只需一个周期的即可获得。 非突发连续读取模式:不采用突发传输而是依次单独寻址,此时可等效于BL=1 。虽然可以让数据是连续的传输,但每次都要发送列地址与命令信息,控制资源占用极大。 突发连续读取模式:只要指定起始列地址与突发长度,寻址与数据的读取自动进行,而只要控制好两段突发读取命令的间隔周期(与 BL 相同)即可做到连续的突发传输。 至于 BL 的数值,也是不能随便设或在数据进行传输前临时决定,而是在初始化的时候,通过模式 寄存器设置命令,进行设置。 目前可用的选项是 1 、 2 、 4 、 8 、全页( Full Page ),常见的设定是 4 和 8 。 若传输长度小于突发长度,则需要发送 Burst Stop(停止突发)命令,结束突发传输。 Addressing Mode,突发访问的地址模式,通过 A3 设置,可以设置为: Sequential (顺序 或 Interleave (交错)。顺序方式,地址连续访问,而交错模式则地址是乱序的,一般选择连续模式。 CAS Latency列地址选通延迟(简称 CL )。在读命令(同时发送列地址)发送完之后需要等待几个时钟周期, DQ 数据线上的数据,才会有效,这个延迟时间,就叫 CL ,一般设置为 2/3 个时钟周期。 特别注意:列地址选通延迟(CL ),仅在读命令的时候有效果,在写命令的时候,并不需要这个延迟。 Write Mode即写模式,用于设置单次写的模式,可以选择突发写入或者单次写入。 初始化 初始化分为五个步骤 1.上电 给SDRAM供电,是能CLK,并发送NOP(No Operation命令),上电后至少要等待200us,再发送其他命令。 2.发送预充电命令 发送预充电命令,给所用BANK预充电 3.发送自动刷新命令 至少要放松8次自动刷新命令,每一次自动刷新命令之间的时间间隔为tRC 4.设置寄存器模式 发送模式寄存器的值,配置SDRAM的工作参数,配置完成后,需要等待tMRD(也叫tRSC),使模式寄存器的配置生效,才能发送其他命令 5.完成 经过前面四个步骤,SDRAM的初始化就完成了,接下来就可以发送激活命令和读写命令进行数据的读写了。 写操作 1.发送激活命令 此命令同时设置行地址和BANK地址,发送该命令后,需要等待tRCD时间,才可以发送写命令 2.发送写命令 在发送完激活命令,并等待tRCD后,发送写命令,该命令同时设置列地址,完成对SDRAM的寻址。同时,将数据通过DQ数据线,存入SDRAM 3.使能自动预充电 在发送写命令的同时,拉高A10地址线,使能自动预充电,以提高读写效率 4.执行预充电 预充电在发送激活命令的tRAS时间后启动,并且需要等待tRP时间 5.完成一次数据写入 至此完成了一次数据写入操作,发送第二个激活命令,启动下一次数据传输。 读操作 1.发送激活命令 此命令同时设置行地址和BANK地址,发送该命令后,需要等待tRCD时间,才可以发送写命令 2.发送读命令 在发送完激活命令,并等待tRCD 后,发送读命令,该命令同时设置列地址,完成对 SDRAM的寻址。读操作还有一个 CL 延迟( CAS Latency ),所以需要等待给定的 CL 延迟( 2 个或 3 个CLK )后,再从 DQ 数据线上读取数据。 3.使能自动预充电 在发送写命令的同时,拉高A10地址线,使能自动预充电,以提高读写效率 4.执行预充电 预充电在发送激活命令的tRAS时间后启动,并且需要等待tRP时间来完成 5.完成一次数据写入 至此完成了一次数据写入操作,发送第二个激活命令,启动下一次数据传输。 FMC接口驱动SDRAM SDRAM相关寄存器 控制寄存器FMC_SDCR1/FMC_SDCR2

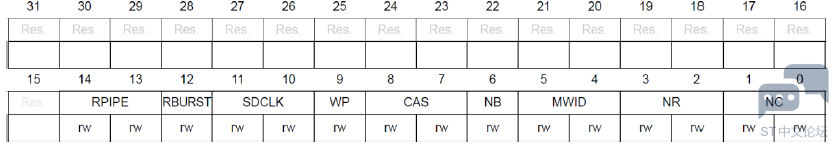

该寄存器只有低15 位有效,且都需要进行配置:

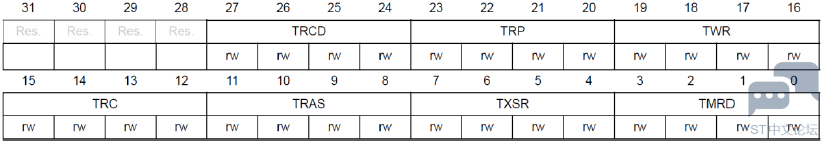

的时序寄存器FMC_SDTR1/FMC_SDTR2 该寄存器用于控制SDRAM的时序

的命令模式寄存器 FMC_SDCMR

刷新定时器寄存器: FMC_SDRTR 以W9825G6KH 为例, W9825G6KH 的刷新周期为 64ms ,行数为 8192行,所以刷新速率为: 刷新速率=64ms/8192=7.81us 而SDRAM 时钟频率 =216Mhz/2=108Mhz 9.26ns , 所以 COUNT 的值为: COUNT=7.81us/9.26ns=844 SDRAM 在接受读请求后,出现内部刷新请求,则必须将刷新速率增加 20 个 SDRAM时钟周期,以获得充足的余量,所以,实际设计的 COUNT 值应该是: COUNT 20=824 。所以设置 FMC_SDRTR 的 COUNT=824 ,就可以完成对该寄存器的配置。

附录 交代 上文中的tRC 、 tMRD 和 tRSC 见 SDRAM 的芯片数据手册。 声明 本文大部分参考于正点原子 |

STM32F745 USART1 Bootloader启动失败排查与解决的流程分析

STM32芯片命名规则

STM32 引脚到底有多少?为什么一个引脚能当好几个用?

入门嵌入式,为什么STM32是“优选起步”?

嵌入式-单片机-STM32 EXTI中断

STM32单片机进行除零运算,为何程序不崩溃?

STM32 LL为什么比HAL高效?

STM32时钟详解

2025国庆中秋活动体验报告2——TouchGFX的UI设计

2025国庆中秋活动体验报告1——TouchGFX环境配置

微信公众号

微信公众号

手机版

手机版