.png) STMCU小助手

发布时间:2021-12-13 23:15

STMCU小助手

发布时间:2021-12-13 23:15

|

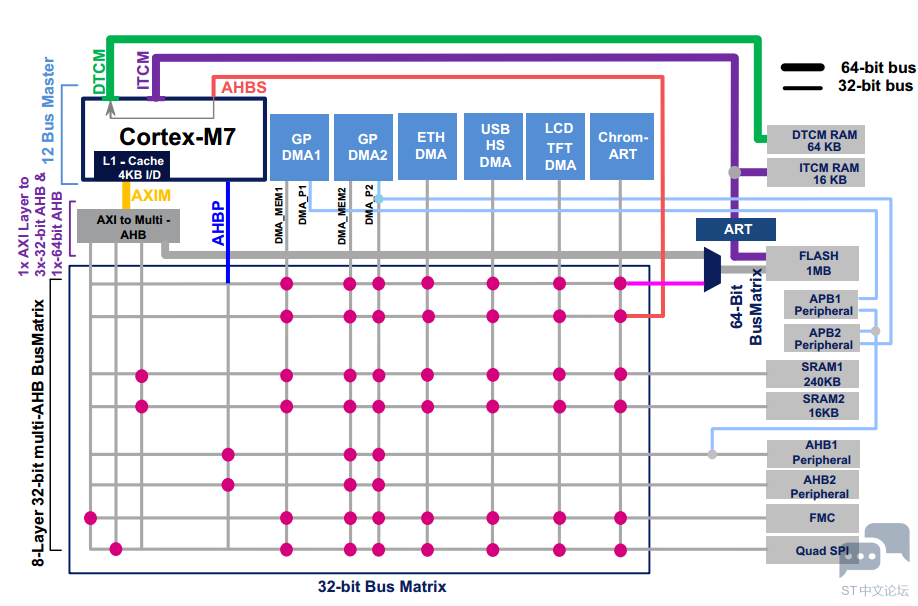

2. STM32F7 新特性——高速缓存 2.1 STM32F7 的存储系统 STM32F7 系列微控制器作为高性能微控制器,为我们带来了很多让人眼前一亮的新特性,其中之一就是独立的指令和数据高速缓冲存储器,也就是所谓的 L1-cache,包括 I-Cache 和 D-Cache。Cache 的大小根据不同型号有所差别,有 4Kbytes、8Kbytes 和 16Kbytes 几种容量。 实际上,这个 Cache 是放在 Cortex 内核里面的,半导体厂商(比如 ST)购买 IP 核的时候可以选择要多大的 cache,之后这款 MCU 的 cache 就已经固定了。这有点像我们去 4S 店买车,根据自身的需求和资金情况选择不同的配置。显然,cache 的容量越大,价格也就越高。本文所使用的 STM32F769I-DISCO 包含 16Kbytes 的 I-Cache 和 D-Cache。

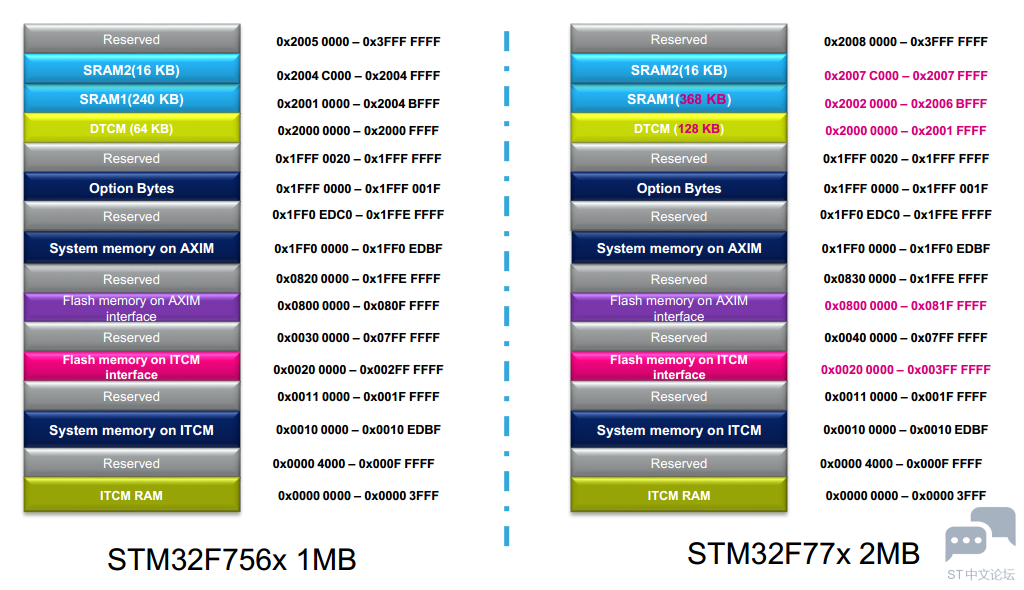

上图是 STM32F7 系列微控制器的系统架构框图,我们可以看到在 Cortex-M7 内核里面有一个 I-Cache 和一个 D-Cache,它们是实实在在的高速存储器。而 DTCM 和 ITCM 则是两个接口,对应 Data TCM 和 Instruction TCM,它们有利于数据和指令的快速读取,可实现内嵌 Flash 的零时延数据读取。但是要注意 TCM 接口是不经过缓存的! 上图的 F7 框图,包含 1 MB Flash 和 320 KB SRAM,其中的 320 KB 的 SRAM 是分离的,它包括 64 KB 的 DTCM RAM、240 KB SRAM1 以及 16 KB SRAM2,而 16 KB 的 ITCM RAM 和 4 KB 的备份 RAM 并不包含在内。 这几个 SRAM 的关系,我们来看下面这个图就比较明白了。

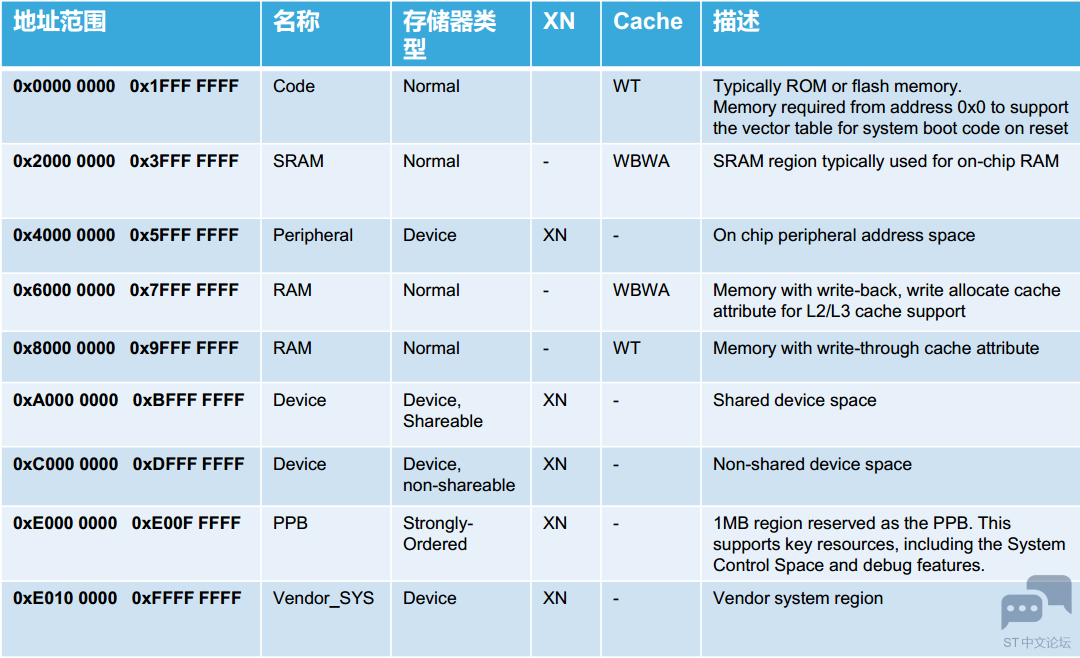

可以看到,DTCM RAM、SRAM1 和 SRAM2 在地址映射上是连续的,比如从 0x20000000 到 0x2007FFFF。 我们还可以看到内嵌的 Flash 有两种接口,分别是 AXIM 和 ITCM 接口,对应于地址 0x08000000 和 0x00200000。那怎么通过不同的接口操作 Flash 呢?——只要操作对应的地址即可。 2.2 Cache 的组织 在前面我们说过,绝大多数控制器的 Cache 都是采用组关联(set-associative)的映射方式,STM32F7 当然也不例外。那么,F7 的 Cache 是如何组织的呢? 通过文档 AN4839,我们可以了解到: // 第5页 A cache is normally implemented using sets of lines where a line is just a short segment of memory. The number of lines in a set is called x-way associative. This property is set in the hardware design. // 第6页 The L1-caches on all Cortex®-M7s are divided into lines of 32 bytes. Each line is tagged with an address. The data cache is 4-way set associative (four lines per set) and the instruction cache is 2-way set associative. This is a hardware compromise to keep from having to tag each line with an address. 也就是说,D-Cache 和 I-Cache 的块大小(cache line)为 32 bytes,采用组关联映射方式。对于 D-Cache,每组(set)包含 4 个缓冲行(line);对于 I-Cache,每组(set)包含 2 个缓冲行(line)。 以 16 KBytes 的 D-Cache 来计算,一共 512 个缓冲行(lines),128 个组(sets),每组包含 4 个 line,每个 line 包含 8 个字,也就是 32 个字节。 2.3 存储器默认映射和属性 STM32F7 系列微控制器的存储器的默认映射和属性如下图所示。

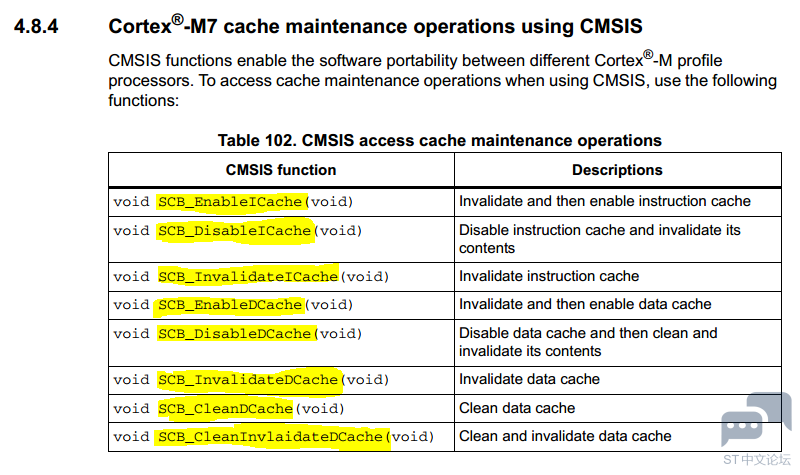

“默认”的意思就是如果没有启动 MPU,并且没有对某些特殊寄存器进行配置,那么存储器的映射地址及其属性就如上图所示。 其中,WT 表示 Write-through(透写),WB 表示 Write-back(回写),WA 表示 Write-allocate(写分配),没有明确标注 WA 的就是 RA(读分配)。XN 的意思是 Execute-Never, 其含义为如果相应的地址空间是 XN,是绝不允许执行代码的。 存储器类型为 Normal 的才能使用 cache,并且 TCM 接口是 not cacheable 的。 当然,这只是默认值,部分存储器地址映射和属性是可以通过 MPU 来配置的。 选取几个有特点的区域稍微讲解一下吧: 0x00000000~0x1FFFFFFF:flash 空间, 属性为 normal, cache 的属性为 Write-through, 即更新 cache 的同时,将数据同时写入相应的物理地址空间。 0x20000000~0x3FFFFFFF:SRAM 空间, 属性为 normal, cache 的属性为 write-back, 即仅更新 cache, 在合适的时候(由 cache 策略决定或者软件强制更新)将数据更新到相应的 SRAM 空间。 0x40000000~0x5FFFFFFFF:芯片内部的外设空间,属性为 device,这一区域是外设寄存器所处的位置,对其读写的过程中不会经过 cache。 2.4 CMSIS 函数 前面说了那么多,我自己都有点晕了。。。对于用户来说,如何正确使用 Cache 才是关键! 下面这张图是在文档 PM0253 中截取的,Cache 相关操作的函数在 cmsis/include/core_cm7.h 头文件中声明。从函数名中可以知道,包括四种 cache 操作:enable、disable、clean 和 invalidate。

查看源代码发现,除了表中的8个函数,还有以下3个函数(都是以 _by_Addr 结尾):

好,那下面我们一一来了解这些函数吧。 SCB_EnableICache() 和 SCB_EnableDCache() 使能 I-cache 或 D-cache。 SCB_DisableICache() 和 SCB_DisableDCache() 禁用 I-cache 或 D-cache。 SCB_InvalidateICache() 使 I-cache 无效,I-cache 被 invalidate 之后,当读取指令时,会忽略相应的 cache-line 中的内容(因为被 validate 了),而从真实的物理地址中去获取相应的指令。 SCB_InvalidateDCache() 使 D-cache 无效,D-cache 被 invalidate 之后,当有 Host(如 core,DMA 等)读取数据时,会忽略相应的 cache-line 中的内容( 因为被 validate 了),从真实的物理地址中去获取相应的数据。 SCB_InvalidateDCache_by_Addr() 根据地址信息无效其对应的 cache-line。 SCB_CleanDCache() Clean 所有的 cache-line,即将 dirty 的 cache-line 全部写到 cache line 对应的真实的物理地址中所谓的 drity 属性,即写操作时, 更新了相应的 cache-line,但是没有更新到真实的物理地址,而这个 clean 的动作, 就是将 cache 中的内容更新到真实的物理地址中。 SCB_CleanDCache_by_Addr() 根据地址信息 clean 其对应的 cache-line。 SCB_CleanInvalidateDCache_by_Addr() 根据地址信息 clean 并 invalidate 其对应的 cache-line。 |

STM32F745 USART1 Bootloader启动失败排查与解决的流程分析

STM32芯片命名规则

STM32 引脚到底有多少?为什么一个引脚能当好几个用?

入门嵌入式,为什么STM32是“优选起步”?

嵌入式-单片机-STM32 EXTI中断

STM32单片机进行除零运算,为何程序不崩溃?

STM32 LL为什么比HAL高效?

STM32时钟详解

2025国庆中秋活动体验报告2——TouchGFX的UI设计

2025国庆中秋活动体验报告1——TouchGFX环境配置

微信公众号

微信公众号

手机版

手机版