|

CM3内核有16个中断, 优先级通过 SCB->SHP[0] to SCB->SHP[11] 设置 - /****** Cortex-M3 Processor Exceptions Numbers ***************************************************/

- NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */

- MemoryManagement_IRQn = -12, /*!< 4 Cortex-M3 Memory Management Interrupt SCB->SHP[0] */

- BusFault_IRQn = -11, /*!< 5 Cortex-M3 Bus Fault Interrupt */

- UsageFault_IRQn = -10, /*!< 6 Cortex-M3 Usage Fault Interrupt */

- SVCall_IRQn = -5, /*!< 11 Cortex-M3 SV Call Interrupt */

- DebugMonitor_IRQn = -4, /*!< 12 Cortex-M3 Debug Monitor Interrupt */

- PendSV_IRQn = -2, /*!< 14 Cortex-M3 Pend SV Interrupt */

- SysTick_IRQn = -1, /*!< 15 Cortex-M3 System Tick Interrupt SCB->SHP[11] */

STM32最多有240个中断(通常外部中断写作IRQs): 优先级通过 NVIC->IP[0] to NVIC->IP[239] 设置 - void NVIC_SetPriority( IRQn_Type IRQn, uint32_t priority )

- {

- /* set Priority for Cortex-M System Interrupts */

- if ( IRQn < 0 )

- {

- SCB->SHP[ ( (uint32_t) ( IRQn ) & 0xF ) - 4 ] =

- ( ( priority << ( 8 - __NVIC_PRIO_BITS ) ) & 0xff );

- }

-

- /* set Priority for device specific Interrupts */

- else

- {

- NVIC->IP[ (uint32_t) ( IRQn ) ] =

- ( ( priority << ( 8 - __NVIC_PRIO_BITS ) ) & 0xff );

- }

- }

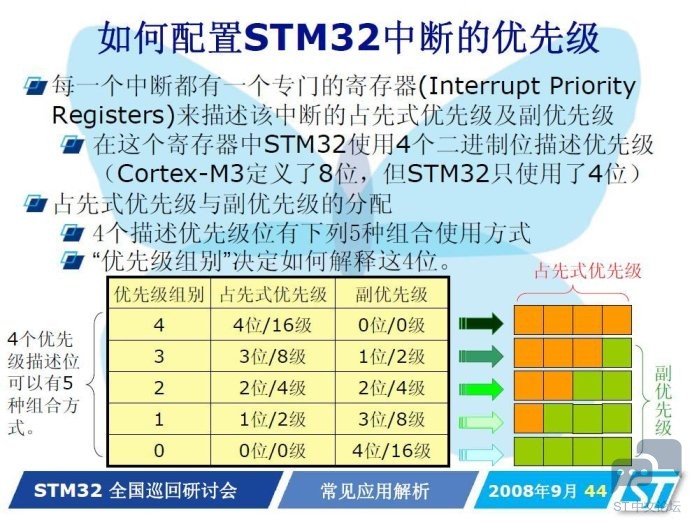

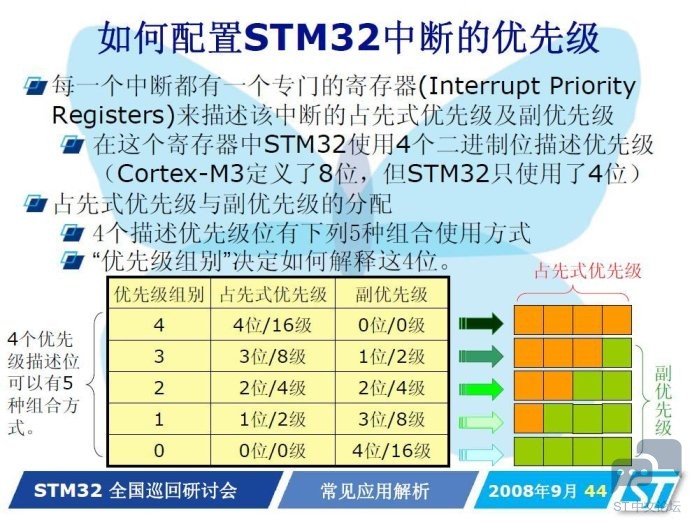

STM32用户能分配的优先级有16级, 也就是用优先级寄存器NVIC->IP[x]的高四位来表示 - /*!< STM32 uses 4 Bits for the Priority Levels */

- #define __NVIC_PRIO_BITS 4

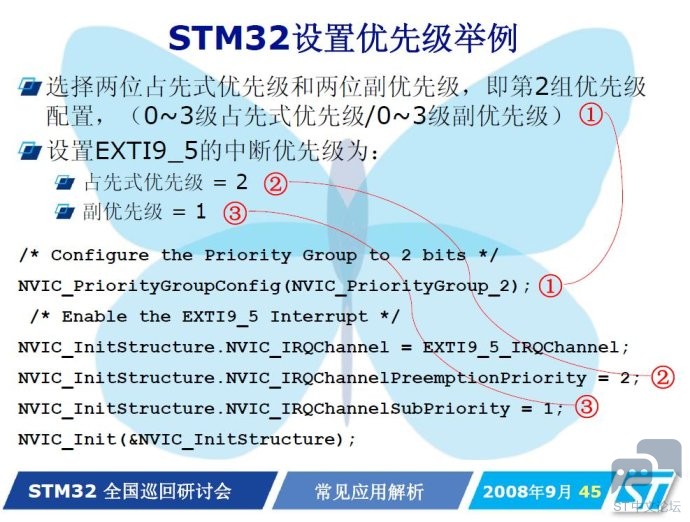

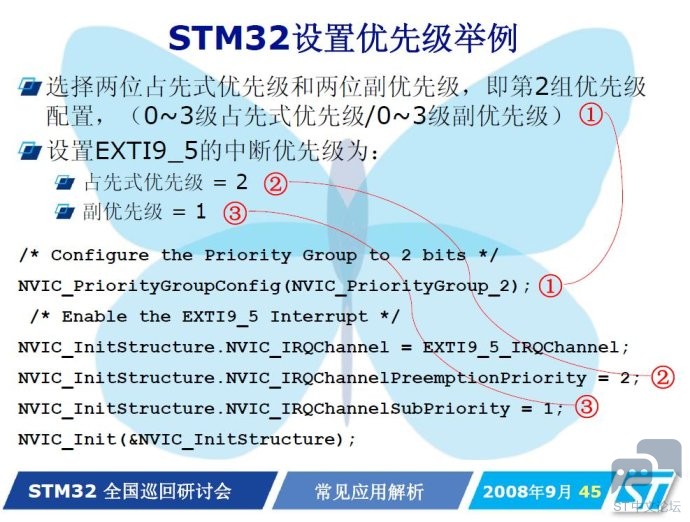

在STM32中将一个中断的优先级分为 : 抢占优先级和响应优先级。上述的4个bit可以灵活分配给抢先优先级和响应优先级 抢占优先级(pre-emption priority) 高抢占优先级的中断会打断当前的主程序/中断程序运行, 俗称中断嵌套

响应优先级(subpriority) 在抢占优先级相同的情况下, 高响应优先级的中断优先被响应 ( 但是不能嵌套 ) 如果有低响应优先级中断正在执行, 高响应优先级的中断要等待已被响应的低响应优先级中断执行结束后才能得到响应 优先级处理 优先级数值较小的优先级较高, 优先级0x00 有最高的优先级, 优先级0xF0 有最低的优先级 在进行优先级判断的时候先是比较抢占优先级, 然后比较响应优先级。 当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,

当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;

如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪一个。 - /*!< 0 bits for pre-emption priority 4 bits for subpriority */

- #define NVIC_PriorityGroup_0 ((uint32_t)0x700)

- /*!< 1 bits for pre-emption priority 3 bits for subpriority */

- #define NVIC_PriorityGroup_1 ((uint32_t)0x600)

- /*!< 2 bits for pre-emption priority 2 bits for subpriority */

- #define NVIC_PriorityGroup_2 ((uint32_t)0x500)

- /*!< 3 bits for pre-emption priority 1 bits for subpriority */

- #define NVIC_PriorityGroup_3 ((uint32_t)0x400)

- /*!< 4 bits for pre-emption priority 0 bits for subpriority */

- #define NVIC_PriorityGroup_4 ((uint32_t)0x300)

|

.png) STMCU小助手

发布时间:2022-2-5 00:00

STMCU小助手

发布时间:2022-2-5 00:00

微信公众号

微信公众号

手机版

手机版