.png) STMCU小助手

发布时间:2022-7-12 22:44

STMCU小助手

发布时间:2022-7-12 22:44

|

前言 STM32F7系列器件是首款基于ARM®Cortex®-M7的32位微控制器。利用ST的ART加速器™和L1缓存的优势,STM32F7系列器件实现了Cortex®-M7的最大理论性能。 基准测试分数稳步达到了1082 CoreMark和462 DMIPS,无论代码是通过嵌入式Flash存储器执行,还是通过内部RAM或者外部存储器(SRAM、SDRAM或者Quad SPI Flash存储器)执行。 STM32F7系列器件的高性能源自: • 强力的超标量流水线和DSP性能提供了一个具有低中断时延的快速实时响应 • 对大容量外部存储的高效访问 • 适合复杂计算的高性能浮点运算能力 本应用笔记呈现了STM32F7的全面架构以及存储接口和特性,它们提供了更高的灵活度以实现最佳的性能以及额外的代码和数据大小。它还提供了有助于提高系统性能和卸载CPU的多主机架构。 本应用笔记同样提供了STM32F7系列器件在多种存储分区配置下(不同代码和数据位置)的架构性能以及使能DMA的架构性能的软件演示。 本应用笔记随附X-CUBE-32F7PERF嵌入式软件包,其中包括两个项目: • Stm32f7_performances项目的目的是演示STM32F7架构在不同配置下的性能,即使用ART accelerator™和高速缓存时代码的执行和数据在不同存储空间中的存储。 • Stm32f7_performances_DMAs目的是演示多主机配置下的架构性能。每个项目都是采用以下可用板子完成:STM32756G-EVAL,STM32F769I-EVAL和STM32F723E-DISCO板。 1 STM32F7系列的系统架构概览 1.1 Cortex®-M7内核 STM32F7系列器件基于高性能的ARM®Cortex®-M7 32位RISC内核,工作频率高达216 MHz。 Cortex®-M7内核具有高性能浮点单元(FPU)。该内核可实现单精度浮点单元或双精度浮点单元(取决于STM32F7系列器件),支持所有ARM®单精度和双精度数据处理指令和数据类型。它还具有一组DSP指令和提高应用安全性的一个存储器保护单元(MPU)。Cortex®-M4到Cortex®-M7的向前兼容性允许为Cortex®-M4编译的二进制数直接在®-M7上运行。 Cortex®-M7的特性是具有分支预测和双指令执行的6/7-级超标量流水线。分支预测允许分支解析以预测下一个分支,因此将环路消耗的周期数从每个环路4和3个周期减少为1个周期。双指令的特征是允许内核同时执行两条指令,并且与指令的顺序无关,由此来增加指令吞吐率。 1.2 Cortex®-M7系统缓存 这些器件嵌入了Cortex®-M7,具有1级缓存(L1-cache),该缓存可分为两个独立的高速缓存:数据缓存(D-cache)和指令缓存(I-cache),支持Harvard架构,可实现最佳性能。这些缓存使得即使在高频率下也可以达到零等待状态。 默认情况下,指令和数据缓存是禁用的。 ARM CMSIS库提供了两个使能数据和指令缓存的函数: • SCB_EnableICache()用于使能指令缓存 • SCB_EnableDCache()用于使能数据缓存 更多关于怎样使能和停用缓存的信息,请参考“ARMv7-M架构参考手册”。 有关STM32F7系列上L1-cache使用的更多详细信息,还请参考STM32F7系列产品上的1级缓存应用笔记(AN4839)。 表 1总结了STM32F7系列中每个器件的缓存空间大小。 ![8X[X{VL`U]38KQXY7(03WXX.png 8X[X{VL`U]38KQXY7(03WXX.png](data/attachment/forum/202207/12/224456s7lvc16xcq48664o.png)

1.3 Cortex®-M7总线接口 Cortex®-M7具有五个接口:AXIM、ITCM、DTCM、AHBS和AHBP。这部分将对它们进行逐一阐述。 除了AHBS接口以外,所有这些接口都是主接口,AHBS接口是一个从接口,可连接其他主接口到Cortex®-M7。 1.3.1 AXI总线接口 AXI作为高级可扩展接口。Cortex®-M7实现了AXIM AMBA4,它是一个64位宽的接口,用以获得更大取指和数据加载带宽。 如果缓存使能,任何不是对TCM或者AHBP接口的访问由适当的缓存控制器处理。用户需要考虑到并非所有的存储区域都可以缓存,这取决于它们的类型。具有共享存储、器件或者强秩序类型的存储区域无法缓存。只有典型的非共享存储器才可以缓存。 更多关于存储器属性和行为的信息,请参考“ARMv7-M架构参考手册”。 为了修改存储区域的类型和属性,可以使用MPU使其可以缓存。这可以通过配置TEX字段和MPU_RASR寄存器中的S、C和B位来完成。 表 2总结了在cortex®-M7复位之后存储区域的属性。 ![1@3KOOK0FC126]LI1$}N6ZI.png 1@3KOOK0FC126]LI1$}N6ZI.png](data/attachment/forum/202207/12/224457g0dxa1zgalbyyaza.png)

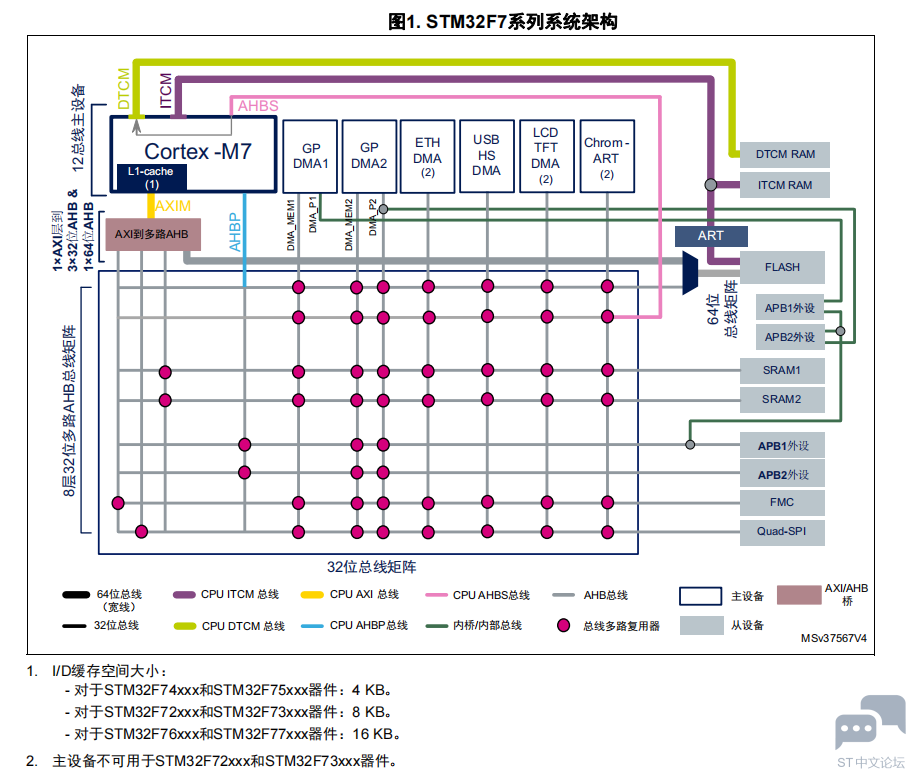

在STM32F7系列器件中,64位AXI主控总线通过一个高性能的AXI到multi-AHB桥接器件来连接内核到总线矩阵,该桥接器件具有四个主接口: • 到内部Flash存储的1x 64位AHB • 到总线矩阵的3x 32位AHB 1.3.2 TCM总线接口 作为紧密耦合的TCM存储器用来提供内核到内部RAM存储器的连接。TCM接口具有哈佛架构,因此这里有一个ITCM(指令TCM)和DTCM(数据TCM)接口。ITCM具有一个64位的存储接口,而DTCM分为两个32位端口:D0TCM和D1TCM。 1.3.3 AHBS总线接口 Cortex®-M7 AHBS(AHB从设备)是一个32位宽接口,可以提供系统到ITCM、D1TCM和D0TCM的访问。然而在STM32F7架构中,AHBS只允许与DTCM-RAM的数据相互传输(见图 1)。AHBS上无法访问ITCM总线,因此不支持DMA与ITCM RAM之间的数据传输。对于DMA与ITCM接口上的-Flash存储之间的数据传输,所有的传输被强制通过AHB总线。AHBS接口可以在内核处于睡眠状态时使用,因此DMA传输可以在低功耗模式下进行。 1.3.4 AHBP总线接口 AHBP接口(AHB外设)是一个单独的32位宽的接口,专门用于CPU和外设的连接。它只用于数据访问。取指令从不在该接口上进行。在STM32F7架构中,这条总线连接Cortex-M7内核的AHBP外设总线到AHB总线矩阵。该总线连接到AHB1、AHB2、APB1和APB2外设。 1.4 STM32F7总线矩阵 STM32F7系列器件的特征是具有一个216 MHz的总线矩阵,该总线矩阵实现内核、主设备和从设备的互连。该总线矩阵允许内核、主设备和从设备之间的多个并行访问路径存在,即使当几个高速外设同时工作时,也可以实现并发访问和高效运行。CPU和它的总线矩阵可以工作在同样的频率,即216 MHz。 一个内部的仲裁器解决了总线矩阵上的冲突和主设备的总线并发访问。仲裁器采用轮询调度算法。 图 1显示了STM32F7系列器件的整体系统架构和总线矩阵连接。

STM32F7总线矩阵互连: • 十二个总线主设备或发起者: – 三条从AXI转AHB桥出来的32位AHB总线 – -一条从AXI转AHB桥出来的64位AHB总线,连接到嵌入式FLASH存储器 – Cortex®-M7 AHB外设总线 – DMA1存储器总线 – DMA2存储器总线 – DMA2外设总线 – 以太网DMA总线(a) – USB OTG HS DMA总线 – LCD-TFT控制器DMA总线(a) – Chrom-Art加速器®(DMA2D)存储器总线(a) • 八个总线从设备: – AHB总线上的内嵌Flash存储器(用于Flash读/写访问、代码执行和数据访问) – Cortex®-M7 AHBS从接口(仅用于DTCM-RAM的DMA数据传输)。 – 内部主SRAM1 – 内部辅助SRAM2 – AHB1外设(包括AHB至APB总线桥、APB1和APB2外设) – AHB2外设 – FMC存储器接口 – Quad SPI存储器接口 1.5 STM32F7存储器 STM32F7器件根据 STM32F72xxx/STM32F73xxx,STM32F74xxx/STM32F75xxx或STM32F76xxx/STM32F77xxx器件(参考表 3,表 4和表 5)嵌入了不同空间大小的闪存、不同空间大小的SRAM、分散架构和外部存储器接口(如FMC和Quad-SPI)。这样的配置为用户分配应用存储资源提供了灵活性,用户可以根据需要配置,并且获得良好的性能与应用代码长度之间的折衷。 1.5.1 嵌入式 Flash 每个STM32F7系列器件都有各自的闪存空间大小(参考表 3、表 4和表 5)。在STM32F72xxx和STM32F73xxx器件中,闪存可以128位宽进行数据读取访问,而在STM32F74xxx和STM32F75xxx器件中,闪存以256位宽进行数据读取访问。在STM32F76xxx和STM32F77xxx器件中,存储器模式使能(单存储区模式中为256位访问,双存储区模式中为128位访问)后,闪存可以128位宽或256位宽进行数据读取访问。 所有器件中,闪存均可通过三个主接口进行读或/和写访问。 • 64位ITCM接口: 它通过ITCM总线(图 2中的路径1)连接嵌入式Flash存储器与Cortex-M7,同时用于程序执行和常量的数据读取。到Flash存储器写访问不允许通过这条总线完成。 Flash存储器可以由CPU通过ITCM从开始地址0x00200000访问。 由于嵌入式Flash存储器相对内核速度较慢,自适应实时加速器(ART)用来释放Cortex-M7内核的性能,同时在高达216 MHz的CPU频率时,允许来自Flash存储器的零等待执行。STM32F7 ART仅适用于ITCM接口上的闪存访问。选择了存储区模式后,它可实现统一的指令缓存,并实现STM32F72xxx和STM32F73xxx器件中128位 x 64行的分支缓存, STM32F74xxx和STM32F75xxx器件中256位 x 64行的分支缓存,STM32F76xxx和STM32F77xxx器件中128/256位 x 64行的分支缓存。ART可用于指令和数据访问,这提高了顺序代码和循环的执行速度。ART同样实现了预取(ART预取)。 • 64位AHB接口: 它通过AXI/AHB桥(图 2中的路径2)连接嵌入式Flash存储器和Cortex-M7。它用于代码执行、读访问和写访问。Flash存储器可以由CPU通过AXI从开始地址0x08000000访问。 • 32位AHB接口: 它用于DMA和Flash存储器的传输(图 2中的路径3)。DMA闪存访问从地址0x08000000开始执行。 对于控制、配置、寄存器访问,Flash存储器接口可以通过AHBP/AHB1外设路径访问,这个路径是一条32位AHB总线(图 2中的路径4)。 如果到Flash存储器的访问在从0x0800 0000开始的地址完成,这就会自动通过AXI/AHB执行。指令或/和数据缓存应该在这种配置下使能以获得对Flash存储器的类似零等待访问。 如果到Flash存储器的访问在从0x0200 0000开始的地址完成,这就会自动通过ITCM总线执行。应使能ART加速器™以获得通过ITCM总线到Flash存储器的等效零等待状态访问。通过设置FLASH_ACR寄存器中的位9来使能ART,通过设置相同寄存器中的位8来使能ART预取。 ![SUMYFH1)NX9EVAU]0]N%TAS.png SUMYFH1)NX9EVAU]0]N%TAS.png](data/attachment/forum/202207/12/224457ubm6l3qhqqumymyu.png)

1.5.2 嵌入式SRAM STM32F7系列器件具有一个带分散架构的大SRAM。它一共分为四个块: • 映射到地址0x0000 0000的指令RAM(ITCM-RAM),仅可供内核访问,即通过图 3中的路径1。它可按字节、半字(16位)、全字(32位)或双字(64位)访问。 ITCM-RAM可以在最大的CPU时钟速度下访问,没有任何延迟。ITCM-RAM由总线竞争保护,因为只有CPU可以访问这片RAM区域。 • DTCM-RAM在TCM接口上映射到地址0x2000 0000,可以被来自AHB总线矩阵上的所有AHB主设备访问:由CPU通过DTCM总线(图 3中的路径5)和由DMA通过内核的专用AHBS总线,即图 3中的路径6。它可按字节、半字(16位)、全字(32位)或双字(64位)访问。DTCM-RAM可以在最大的CPU时钟速度下访问,没有任何延迟。通过主设备(DMA)到DTCM-RAM的并发访问和它们的优先级可以被Cortex-M7中的从控制寄存器(CM7_AHBSCR寄存器)处理。相对于其他主设备(DMA),CUP具有访问DTCM-RAM的更高优先级。更多关于这个寄存器的信息,请参考“ARM® Cortex®-M7处理器技术参考手册”。 • SRAM1可以被所有来自AHB总线矩阵的AHB主设备访问,也就是所有通用DMA和专用DMA。 SRAM1可按字节、半字(16位)或全字(32位)访问。对于可能的SRAM1访问,请参考图 3(路径7)。它可以用于数据读取和代码执行。 • SRAM2可以被所有来自AHB总线矩阵的AHB主设备访问。所有通用DMA和专用DMA均可访问此存储区域。SRAM2可按字节、半字(16位)或全字(32位)访问。对于可能的SRAM2访问增加“路径”,请参考图 3(路径8)。它可以用于数据读取和代码执行。 ![EFNV1[CEI`DMW)J6_D]A5PD.png EFNV1[CEI`DMW)J6_D]A5PD.png](data/attachment/forum/202207/12/224457ar7n81oj6e8nptf7.png)

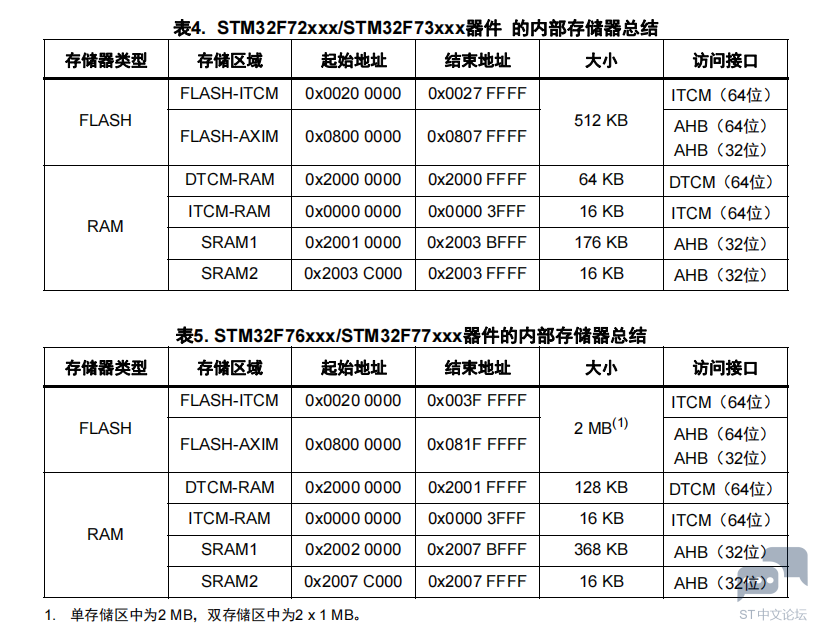

表 3,表 4和表 5总结了STM32F7系列器件的内部存储器映射和存储器空间大小:

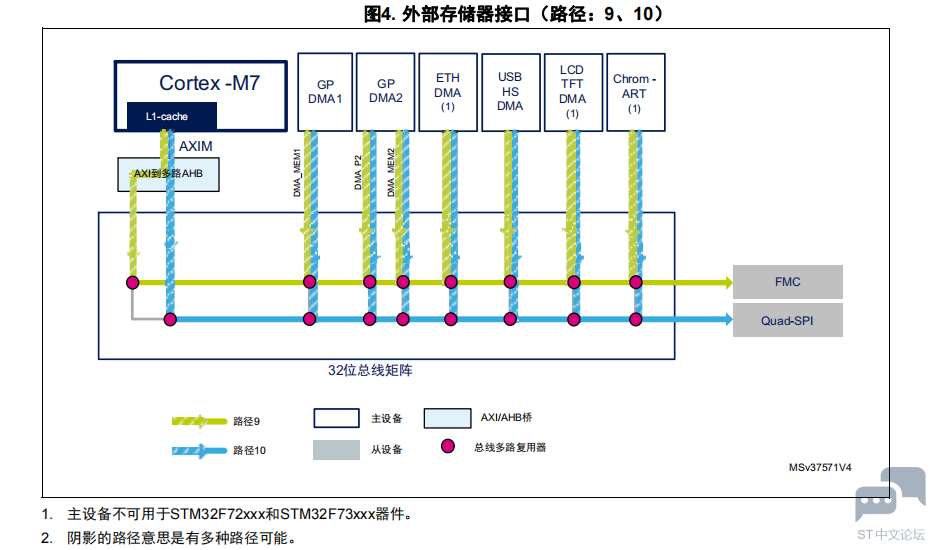

1.5.3 外部存储器 除了内部存储器和存储控制器,比如USB和SDMMC之外,用户可以用可变存储控制器(FMC)和Quad SPI控制器扩展STM32F7的存储。 图 4显示了通过AXI/AHB总线互连CPU、不同的DMA和外部存储的可能路径。如图 4所示,外部存储可以利用Cortex®-M7缓存的优点,因此无论是数据载入/存储或者代码执行位置,都可以获得最高性能。这样性能与和大存储容量就可以相容。 图 4中的路径9显示了使用CPU或DMA可能的FMC访问。 图 4中的路径10显示了使用CPU或DMA可能的Quad-SPI访问。

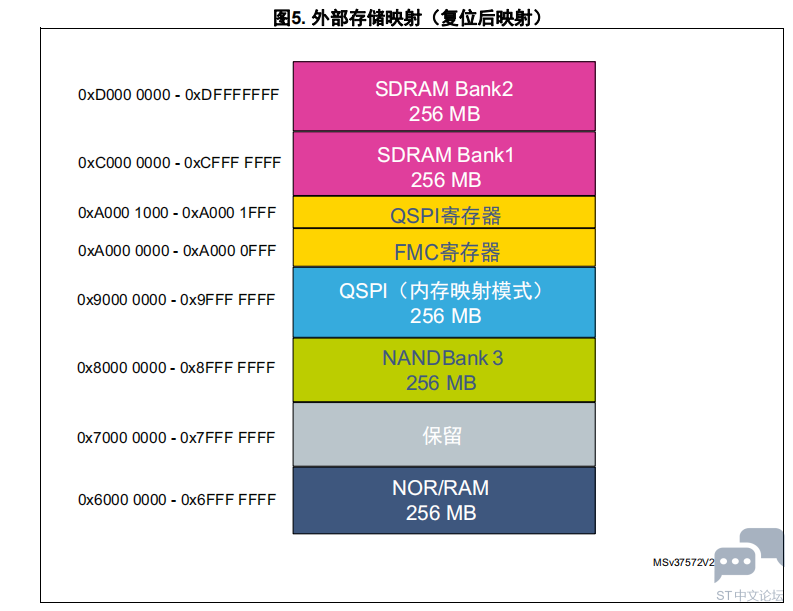

所有的外部存储器可以被所有的主设备访问(CPU和DMA)。因此允许存储器/存储器DMA传输或者外设/存储DMA传输。 图 5汇总了复位之后的外部存储的存储映射和它们的地址范围(SYSCFG_MEMRMP寄存器中的SWP_FMC[1:0]字节设置为0)。

可变存储控制器(FMC)接口 STM32F7 FMC控制器连接存储映射器件,包括SRAM、ROM、NOR/NAND Flash存储和SDRAM器件。它用于程序执行(除了NAND Flash之外)或者数据载入/存储操作。 STM32F7 FMC特征: • 4个同时支持不同存储器的存储区域。 • 每个存储区域有独立的片选控制 • 每个存储区域可独立配置 • 可对时序进行编程,以支持各种器件 • 8/16/32位数据总线 • 外部异步等待控制 • 有两个bank提供与同步DRAM(SRAM)存储器的连接所有FMC外部存储器与控制器共享地址、数据和控制信号。 每个外部器件可以通过唯一的片选信号访问。FMC一次只能访问一个外部器件。 两个默认的SDRAM存储区域不可缓存。因此即使缓存使能,数据和指令也不会通过缓存。为了利用缓存加速的优点,SDRAM存储区域可以由0xC000 0000和0xD000 0000分别重新映射到0x6000 0000和0x7000 0000,这是默认的可缓存区域。通过设置SYSCFG_MEMRMP寄存器中的字段SWP_FMC [1:0] = 01来完成。如果重映射在应用中不适用,Cortex®-M7 MPU可以用来修改默认的SDRAM存储器的性质,使其可以缓存。 所有可能链接到FMC的外部存储器将会受益于数据和L1缓存(图 4中的路径9),使它们有更大的数据或/和代码长度,达到最高性能。 Quad-SPI接口 STM32F7系列器件集成了一个Quad SPI存储接口,它是一个专用的通信接口,连接单、双或者Quad SPI Flash存储器。这种多宽度接口支持传统的单线SPI串行输入输出,也支持双线和四线的串行命令。除此之外,接口支持双倍数据速率(DDR)读出命令,这意味着地址传输和地址读出在通信时钟的两个边沿执行。它允许两倍的数据/指令吞吐率,因此提高了对外部Quad SPI Flash存储器的访问效率。 它可以在以下三种模式下工作: • 直接模式:使用Quad SPI寄存器执行全部操作 • 状态轮询模式:周期性读取外部FLASH状态寄存器,而且标志位置1时会产生中断 • 存储映射模式:外部Flash进行存储映射,系统将其视作内部存储器 在存储映射模式下,STM32F7 Quad SPI接口可以管理高达256 MB的Flash存储器,存储地址从0x9000 0000到0X9FFF FFFF。它映射到一个可执行区域,因此不需要重映射。 相比FMC,Quad-SPI允许连接一个外部Flash存储器,这种连接成本较低(小封装使得PCB面积减小)并且使用GPIO较少。对于任意闪存大小,在单-四模式(4位)下使用6个 GPIO,在双-四模式(8位)下使用10个GPIO。 如图 4(路径10)所示,Quad SPI映射到一个AHB上的专用层,并且可以受益于L1-缓存。这允许以良好的性能执行代码并且从Quad-SPI载入数据。 Quad-SPI同样可以通过所有的在AHB总线矩阵上的主设备访问,特别是Chrom-ART加速器® 和LCD-TFT,使高效的数据传输能够完成,特别是图像,因为图像应用中需要高帧率的显示。 请参考STM32微控制器上的Quad-SPI(QSPI)接口 应用笔记(AN4760),了解如何使用STM32微控制器来配置、编程以及读取外部Quad-SPI存储器。 完整版请查看:附件 |

DM00169764_ZHV4.pdf

下载1.31 MB, 下载次数: 11

STM32F745 USART1 Bootloader启动失败排查与解决的流程分析

STM32芯片命名规则

STM32 引脚到底有多少?为什么一个引脚能当好几个用?

入门嵌入式,为什么STM32是“优选起步”?

嵌入式-单片机-STM32 EXTI中断

STM32单片机进行除零运算,为何程序不崩溃?

STM32 LL为什么比HAL高效?

STM32时钟详解

2025国庆中秋活动体验报告2——TouchGFX的UI设计

2025国庆中秋活动体验报告1——TouchGFX环境配置

微信公众号

微信公众号

手机版

手机版