.png) STMCU小助手

发布时间:2022-7-14 18:00

STMCU小助手

发布时间:2022-7-14 18:00

|

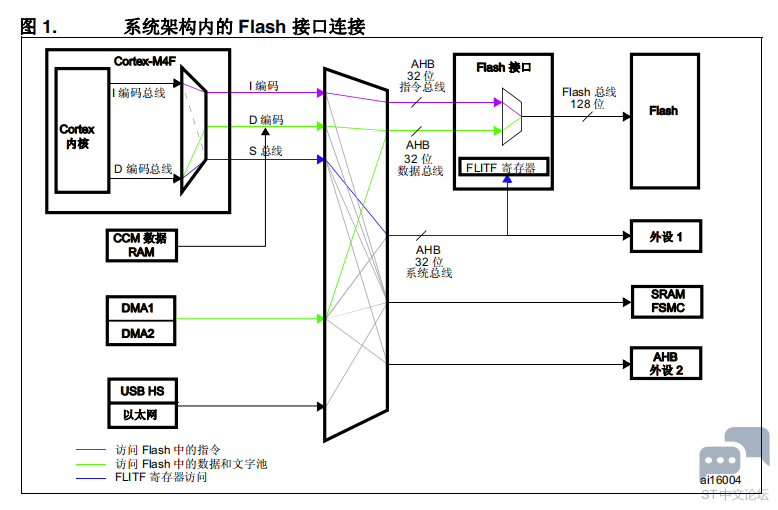

前言 本编程手册介绍了 STM32F405xx、STM32F407xx、STM32F415xx 和 STM32F417xx 微控制器 Flash 的编程方法。为方便起见,本文档将上述产品统称为 STM32F40x 和 STM32F41x(除非另行声明)。 STM32F40x 和 STM32F41x 嵌入式 Flash 可采用在线编程或在应用中编程两种方式。 在线编程 (ICP) 方式适用于更新 Flash 的所有内容,更新时使用 JTAG、SWD 协议或自举程序将用户应用程序加载到微控制器。ICP 可实现快速而高效的设计迭代,并且避免了不必要的器件封装处理或插接。 与 ICP 方法相比,在应用中编程 (IAP) 可通过微控制器支持的任何通信接口(I/O、USB、CAN、UART、I2C 和 SPI 等)将编程数据下载到存储器。使用 IAP 方式时,可以在应用程序运行期间对 Flash 重新编程。但是,部分应用程序必须事先通过 ICP 方式编程到 Flash。 Flash 接口根据 AHB 协议实施指令访问和数据访问。它将实施可加快 CPU 代码执行速度的预取缓冲器,以及执行 Flash 操作(编程 / 擦除)所必需的逻辑。编程 / 擦除操作可在整个产品电压范围内执行。读写保护和选项字节的设置也通过 FLASH 接口来操作。 1 Flash 接口 1.1 简介 Flash 接口可管理 CPU 对 1 MB(64 Kb × 128 位)Flash 进行的 AHB I-Code 和 D-Code 访问。该接口可针对 Flash 执行擦除和编程操作,并实施读写保护机制。 Flash 接口通过指令预取和缓存机制加速代码执行。 1.2 主要特性 ● Flash 读操作 ● Flash 编程/擦除操作 ● 读/写保护 ● I-Code 上的预取操作 ● I-Code 上的 64 个缓存行(128 位) ● D-Code 上的 8 个缓存行(128 位) 图 1 所示为系统架构内的 Flash 接口连接。

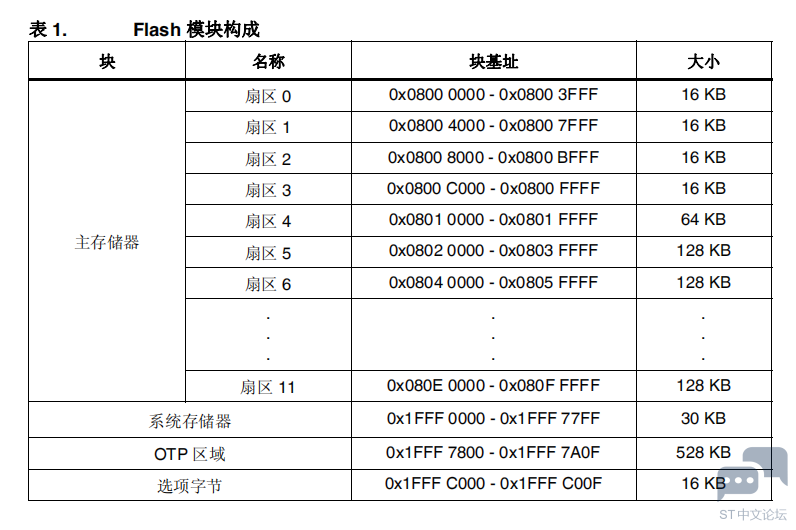

1.3 Flash Flash 具有以下主要特性: ● 高达 1 MB 容量 ● 128 位宽数据读取 ● 字节、半字、字和双字数据写入 ● 扇区擦除与批量擦除 ● 存储器构成 Flash 结构如下: — 主存储器块,含 4 个 16 KB 扇区、1 个 64 KB 扇区 和 7 个 128 KB 扇区。 — 系统存储器,器件在系统存储器自举模式下从该存储器自举。 此区域为意法半导体预留,其中包含自举程序,用以通过以下接口之一对 Flash 进行重新编程:USART1、USART3、CAN2、USB OTG FS 设备模式(DFU:设备固件升级)。自举程序由 ST 在器件制造期间编写,用于防止误写/误擦除操作。 — 512 OTP(一次性可编程)字节,用于存储用户数据。 OTP 区域包含 16 个附加字节,用于锁定相应的 OTP 数据块。 — 选项字节:读写保护、BOR 级别、软件 / 硬件看门狗以及器件在待机或停机模式下的复位。 ● 低功耗模式(有关详细信息,请参见参考手册的“电源控制 (PWR)”部分)

1.4 读接口 1.4.1 CPU 时钟频率与 Flash 读取时间之间的关系 为了准确读取 Flash 数据,必须根据 CPU 时钟 (HCLK) 频率和器件电源电压在 Flash 存取控制寄存器 (FLASH_ACR) 中正确地编程等待周期数 (LATENCY)。表 2 所示为等待周期与CPU 时钟频率之间的对应关系。 注: VOS = ‘0’时,fHCLK 最大值 = 144 MHz。 ![_T1}UE[7$]V@OJ3RQ]SOQ6F.png _T1}UE[7$]V@OJ3RQ]SOQ6F.png](data/attachment/forum/202207/13/181556d2ussas7bpbtt27t.png)

复位后,CPU 时钟频率为 16 MHz,FLASH_ACR 寄存器中的等待周期 (WS) 为 0 个。 强烈建议通过以下软件序列来调整在访问 Flash 时所需的等待周期数和 CPU 频率。 需要提高 CPU 频率时的操作步骤 1. 将新的等待周期数编程到 FLASH_ACR 寄存器中的 LATENCY 位。 2. 通过读取 FLASH_ACR 寄存器,检查在访问 Flash 时是否采用了新的等待周期数。 3. 通过改写 RCC_CFGR 寄存器中的 SW 位来修改 CPU 时钟源。 4. 如有需要,可通过改写 RCC_CFGR 中的 HPRE 位来修改 CPU 时钟预分频器。 5. 通过读取 RCC_CFGR 寄存器中相应的时钟源状态(SWS 位)和/或 AHB 预分频值(HPRE 位),检查是否采用了新的 CPU 时钟源和/或新的 CPU 时钟预分频值。 需要降低 CPU 频率时的操作步骤 1. 通过改写 RCC_CFGR 寄存器中的 SW 位来修改 CPU 时钟源。 2. 如有需要,可通过改写 RCC_CFGR 中的 HPRE 位来修改 CPU 时钟预分频器。 3. 通过读取 RCC_CFGR 寄存器中相应的时钟源状态(SWS 位)和/或 AHB 预分频值(HPRE 位),检查是否采用了新的 CPU 时钟源和/或新的 CPU 时钟预分频值。 4. 将新的等待周期数编程到 FLASH_ACR 中的 LATENCY 位。 5. 通过读取 FLASH_ACR 寄存器,检查在访问 Flash 时是否采用了新的等待周期数。 注: CPU 时钟配置或等待周期 (WS) 配置的更改不会立即生效。为了确保当前的 CPU 时钟频率即为所配置的频率,用户可检查 AHB 预分频系数和时钟源状态值。为了确保所编程的 WS数生效,可读取 FLASH_ACR 寄存器的内容来确认。 完整版请查看:附件 |

DM00023388_ZHV1.pdf

下载986.69 KB, 下载次数: 585

微信公众号

微信公众号

手机版

手机版