.png) STMCU小助手

发布时间:2022-7-14 18:00

STMCU小助手

发布时间:2022-7-14 18:00

|

前言 这份应用笔记是为系统设计者提供的,他们需要对开发板硬件实现的特性有个总体认识,如供电、时钟管理、复位控制、启动模式的设置和调试管理等。该文档说明了STM32F10xxx系列的大容量和中容量产品使用方法,并描述了应用STM32F10xxx开发所需要的最小硬件资源。 详细的参考设计图也包含在这篇文档里,包括主要组件、接口、模式的说明。 1 供电 1.1 简介 该芯片要求2.0~3.6V的操作电压(VDD),并采用嵌入式的调压器提供内部1.8V的数字电源。 当主电源VDD关闭时,实时时钟(RTC)和备用寄存器可以从VBAT供电。 ![UG{FKJ$GI`9CRB1]}@9E1LL.png UG{FKJ$GI`9CRB1]}@9E1LL.png](data/attachment/forum/202207/13/185507oz61zhbbxxb361h0.png)

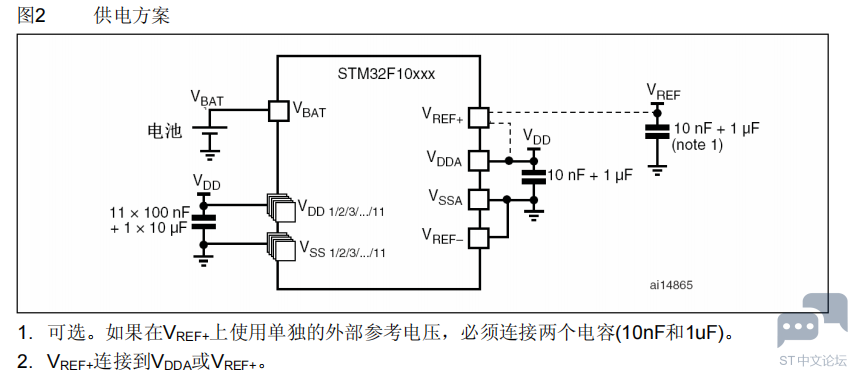

1.1.1 独立 A/D 转换器供电以及参考电压 为提高转换精度,ADC有一个独立的电源供应,它可以被单独滤波和屏蔽以不受PCB噪音的干扰。 ● 一个独立的VDDA引脚给ADC供电 ● VSSA引脚提供一个隔离的接地输入 若有VREF–(取决于封装)时,它必须连到VSSA。 100引脚和144引脚的封装 为保证低电压输入时能得到更好的精度,用户可以连接一个独立的外部参考电压到VREF+,它的电压范围为2.4V到VDDA。 64引脚及更小的封装 没有VREF+和VREF-,它们在内部分别被连接到ADC的供电电源(VDDA)和ADC的地(VSSA)。 1.1.2 备用电池 为了在VDD关闭时仍能保持备份寄存器的内容,VBAT引脚可以有选择地连接到一个由电池或其它电源提供的备用电压。 VBAT引脚也给RTC单元供电,使得RTC在主数字电源(VDD)关闭时仍能正常运行。VBAT的开关由复位模块内的掉电复位(PDR)电路控制。 如果应用中没有外部电池,VBAT必须在外部被连接到VDD。 1.1.3 电压调压器 复位后调压器始终开启。根据应用模式的不同,它也有三种不同的工作模式。 ● 在运行模式下,调压器以正常功耗模式提供1.8V电源(内核、内存和数字外设) ● 在停止模式下,调压器以低功耗模式提供1.8V电源,以保存寄存器和SRAM的内容 ● 在待机模式下,调压器停止供电。除了备用电路和备份域外,寄存器和SRAM的内容全部丢失 1.2 供电方案 电路由稳定的电源VDD供电。 ● 注意: ─ 如果使用ADC,VDD的范围必须在2.4V到3.6V之间 ─ 如果没有使用ADC,VDD的范围为2V到3.6V ● VDD引脚必须连接到带外部稳定电容(11个100nF的陶瓷电容和一个钽电容(最小值4.7μF,典型值10μF))的VDD电源。 ● VBAT引脚必须被连接到外部电池(1.8V < VBAT < 3.6V)。如果没有外部电池,这个引脚必须和100nF的陶瓷电容一起连接到VDD电源上 ● VDDA引脚必须连接到两个外部稳定电容(10nF陶瓷电容+1μF钽电容)。 ● VREF+引脚可以连接到VDDA外部电源。如果在VREF+上使用单独的外部参考电压,必须在这个引脚上连接一个10nF和一个1μF的电容。在所有情况下,VREF+必须在2.4V和VDDA之间。

1.3 复位及电源管理 1.3.1 上电复位(POR)/掉电复位(PDR) STM32集成了一个上电复位(POR)和掉电复位(PDR)电路,当供电电压达到2V时系统就能正常工作。 只要VDD低于特定的阈值——VPOR/PDR,不需要外部复位电路,STM32就一直处于复位模式。更多有关上电/掉电复位阈值的细节,请参考STM32F101xx和STM32F103xx数据手册的电气性能部分。 ![SM82A_~UO{[F3QH]6@A4WA6.png SM82A_~UO{[F3QH]6@A4WA6.png](data/attachment/forum/202207/13/185507uzvo36001fssfsiv.png)

1.3.2 可编程电压监测器(PVD) 用户可以利用PVD对VDD电压与电源控制寄存器(PWR_CR)中的PLS[2:0]位进行比较来监控电源,这几位选择监控电压的阀值。 通过设置PVDE位来使能PVD。 电源控制/状态寄存器(PWR_CSR)中的PVDO标志用来表明VDD是高于还是低于PVD的电压阈值。该事件在内部连接到外部中断的第16线,若该中断在外部中断寄存器中被使能,该事件还将产生一个中断。当VDD低于PVD阈值且/或当VDD高于PVD阈值(根据外部中断第16线的上升/下降沿触发配置)时产生PVD中断。例如,这一特性在实际中可用作执行紧急关闭的任务。 ![]J`C`7V06SSZJVSBA}J~QY2.png ]J`C`7V06SSZJVSBA}J~QY2.png](data/attachment/forum/202207/13/185507d0jd520ct0980lj0.png)

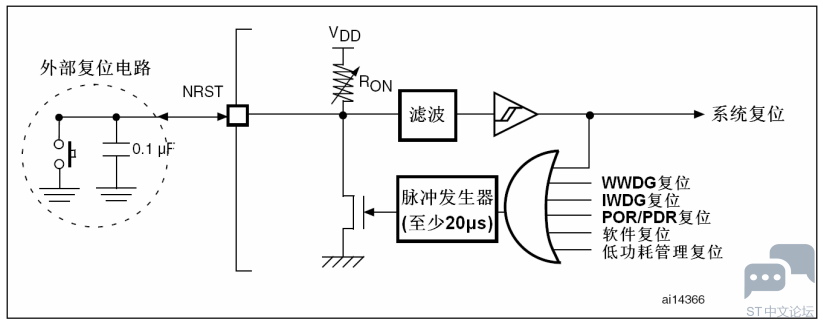

1.3.3 系统复位 系统复位将复位除了时钟控制器CSR中的复位标志和备用域的寄存器以外的所有寄存器(图1)。 当下列事件有一个发生都将产生系统复位: 1. NRST引脚上出现低电平(外部复位) 2. 窗口看门狗计数终止(WWDG复位) 3. 独立看门狗计数终止(IWDG复位) 4. 软件复位(SW复位) 5. 低功耗管理复位 可通过查看控制/状态寄存器(RCC_CSR)中的复位标志来识别复位源。 图5 复位电路

完整版请查看:附件 |

CD00164185_ZHV2.pdf

下载746.54 KB, 下载次数: 2

TFT LCD 与 FSMC 的硬件连接大容量 STM32F10xxx FSMC 接口

单片机:初学者该了解的STM32F103基础知识

OpenBLT移植到STM32F103战舰开发板上适用于所有STM32F103系列的Bootloader

2025软件工具兔哥知道

STM32之继电器模块

STM32固件库分享,超全系列整理

【MCU实战经验】基于STM32F103的二轮平衡车(6轴上位机 源代...

10张图带你完全掌握STM32 GPIO,从入门到精通,收藏就够了!

如果你解决了这些问题,就可以直接学STM32

STM32的分类和选型

微信公众号

微信公众号

手机版

手机版