.png) STMCU小助手

发布时间:2022-10-15 18:54

STMCU小助手

发布时间:2022-10-15 18:54

|

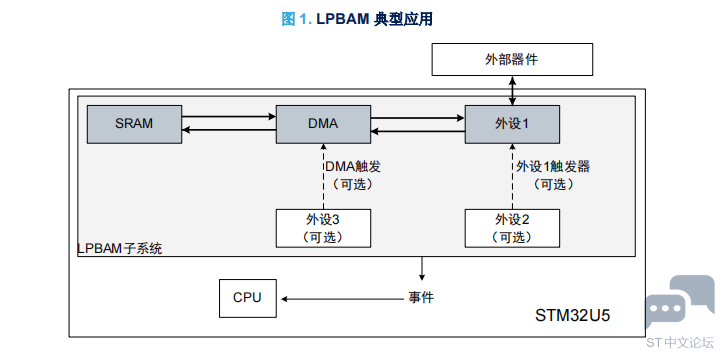

引言5 l9 l- j1 \/ M STM32U5 系列微控制器基于具有 Arm® TrustZone®和 FPU 的高性能 Arm®32 位 Cortex®-M33 CPU。此类产品均采用新型结构制造,得益于其高度灵活性和高级外设集,实现了一流的超低功耗性能。: Q. P5 J! K4 ]* D% J 除了多种 CPU 激活模式配置(可实现更高性能或更低功耗)之外,STM32U5 系列还支持大量低功耗模式,每种模式都具有多个选项。这使得设计人员可以在低功耗性能、短启动时间、可用外设集与 SRAM 数量,以及唤醒源最大数量之间实现最佳折中。3 V" x9 F! G2 Q: P" m 嵌入式 SMPS(开关模式电源)降压转换器可用于带有“Q”后缀的特定部件号(例如 STM32U5xxxxxxQ),从而提高激活和低功耗模式下的能源性能。 STM32U5 器件支持 4 种主要低功耗模式:# d/ |& L7 U. q • 睡眠模式# R: Z9 ^' E/ L CPU 时钟关闭,但所有外设均可保持激活状态。所有外设中断或事件可唤醒 CPU。 • 停机模式 高速时钟默认关闭,所有外设和内存保留均可保持激活状态。四种停机模式可供使用:停机 0、停机 1、停机 2 和停机 3,功耗从高到低。LPBAM(低功耗后台自主模式)是一项创新功能,停机 0、停机 1 和停机 2 模式均支持该功能。借助于LPBAM,一些外设继续与 DMA(直接内存访问)一起自主工作。当外设须保持激活状态时,这大幅降低了应用的功耗。通过 LPBAM,可保持激活的外设数量在停机 2 中要比在停机 0 和停机 1 更少。停机 3 模式不支持 LPBAM。4 p3 _6 B5 V1 [. m" L • 待机模式& Y; E5 R6 [' A! B5 [# k+ b o 内部调压器关闭。大多数外设和 SRAM 保留随后丢失。在待机模式下最多可保留 64 KB SRAM2 和 2 KB BKPSRAM。6 V; w, c0 H3 A • 关断模式 这与待机模式类似,但电源欠压复位和监控被禁用。在该模式下则无法切换到 VBAT。) V5 @3 D4 W' D3 Y2 f. x 通过 LPBAM 和高能效处理,高度灵活的低功耗模式与自主外设相结合,使STM32U575xxxxQ/STM32U585xxxxQ 器件达到行业领先的 EEMBC®ULPBench™分数,高达 535ULPMark™。 1 概述 本应用笔记适用于基于 Arm® Cortex®内核设备的 STM32U5 系列。) {! ]( k s9 E8 H. Y* V 提示 Arm 是 Arm Limited(或其子公司)在美国和/或其他地区的注册商标。, A$ B0 ~" ?* O. I& J 参考文档 [1] 参考手册:基于 Arm 的 STM32U575xx 和 STM32U585xx 高级 32 位 MCU(RM0456): _. ]: O7 z% n- f [2] STM32U575xx(DS13737)和 STM32U585xx(DS13086)的数据表' p, [% i- D. D: E( B9 W [3] 应用笔记用于硬件设置和低功耗的 STM32 微控制器 GPIO 配置(AN4899)' p- H% a& X0 D. v1 _0 Q [4] 应用笔记 STM32U575/585 功耗优化(AN5652)" _4 d6 r" c, Q% n0 c6 a$ Y5 @ K' g [5] EEMBC 组织网址 http://www.eembc.org& n D0 O9 f. c4 a/ c$ I 2 LPBAM 简介' l# R, a' G9 O, A 2.1 LPBAM 概述 LPBAM(低功耗后台自主模式)是一种操作模式,允许外设从设备功耗模式到停机 2 模式独立地正常和自主运行,无需运行任何软件。由于 DMA 链表传输,LPBAM 子系统可以链接不同的操作。DMA 操作可涉及: • 外设数据传输 • 外设配置 使用 LPBAM 自动优化功耗:; G! I: q% f( h/ T • 外设的总线时钟和内核时钟仅在自主外设请求时予以分配。总线时钟(又称系统时钟)通过 AHB 和 APB 分配给所有启用的外设,其中至少包括一个 DMA 和一个 SRAM。 • 内部 RC 振荡器根据外设时钟请求自动开启和关闭。外部振荡器和 PLL 无法用于 LPBAM。9 g9 ^) @! ^2 i7 a3 N T7 \ • 模拟外设在需要时自动开启和关闭。: }0 f- G- K. g$ C) S1 n( R • 该设备可处于低至停机 2 的低功耗模式,无需唤醒来管理外设操作,因此减少了设备唤醒和运行操作期间的能量损失。 即使在停机模式下,大量的硬件触发选择也允许外设自动启动的活动。外设中断在启用时从停机模式唤醒设备。 LPBAM 的典型基本用例是设备处于停机 2 模式下的周期性外设操作(例如 ADC 转换,或通过 I 2C 或 SPI 等通信接口仅限传感器采集)。唤醒源可以是任何外设中断,例如:+ g; ^. Z5 f- K7 L • 外设的传输/转换结束 @9 e0 F4 }2 Z) @+ s7 x • DMA 传输完成 • 错误检测1 g V, i( f' ~3 ~7 p 2 j( N, [' k' p; X

可以使用多个 DMA 通道或在同一通道上链接来自不同外设的操作来构建更复杂的应用。 8 G+ j( \% h% e7 m$ G 2.2 支持 LPBAM 的外设 支持 LPBAM 的外设可分为两类:, }- r: ~. i, _* Y" | • 具有时钟请求功能的自主外设' l- g: _7 K% ?1 n+ T 这些外设支持停机模式下的 DMA 传输。 • LPBAM 被动外设 这些外设不支持 DMA 请求,也不支持生成时钟请求。但借助于 DMA 时钟请求,可以在因 DMA 时钟请求而接收到系统时钟时,对外设本身的寄存机进行重新配置。除此之外,有些也可以为自主外设提供硬件触发。 自主或被动 LPBAM 外设产生的任何中断都会将 STM32U5 器件从 停机 模式唤醒。 提示 停机 3 模式不支持 LPBAM。8 [# i |( g: B2 E . e7 e' d. R2 U( @$ |! ~2 h4 M6 s

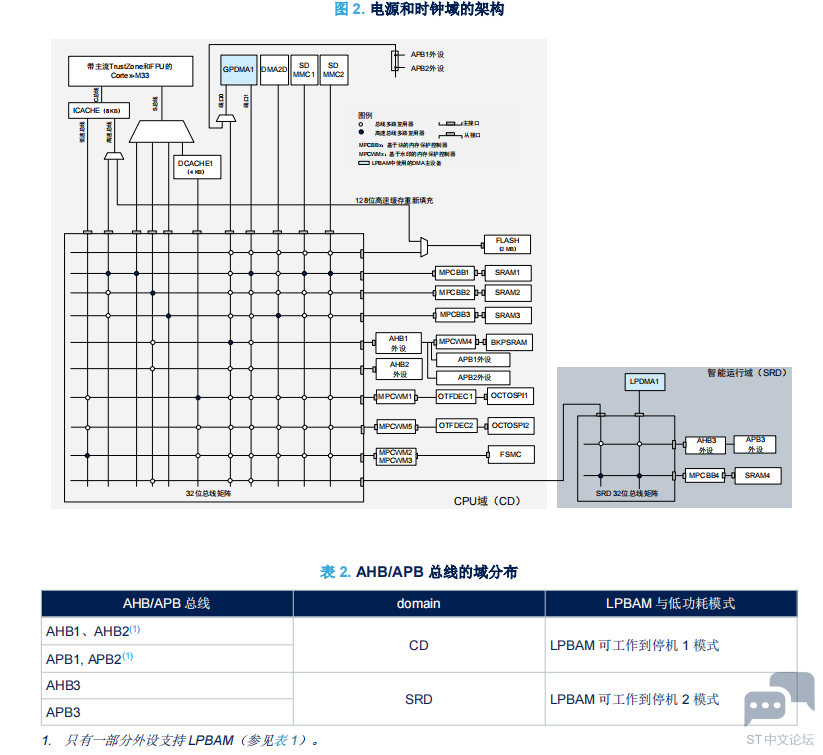

1 l* M5 K8 i) Y) I1 `1 ^ 3 LPBAM 硬件机制0 v; ?2 O F7 V& N; c z 3.1 电源和时钟架构- ^# x+ s: h) L7 q" W3 a STM32U5 分为两个域:CPU 域(CD)和 SmartRun 域(SRD)。下图和下表显示了 AHB 和 APB 外设在这两个域中的分布。; y9 a: c% L3 s8 @- Z: H & J& M P; u+ c; C4 }3 i

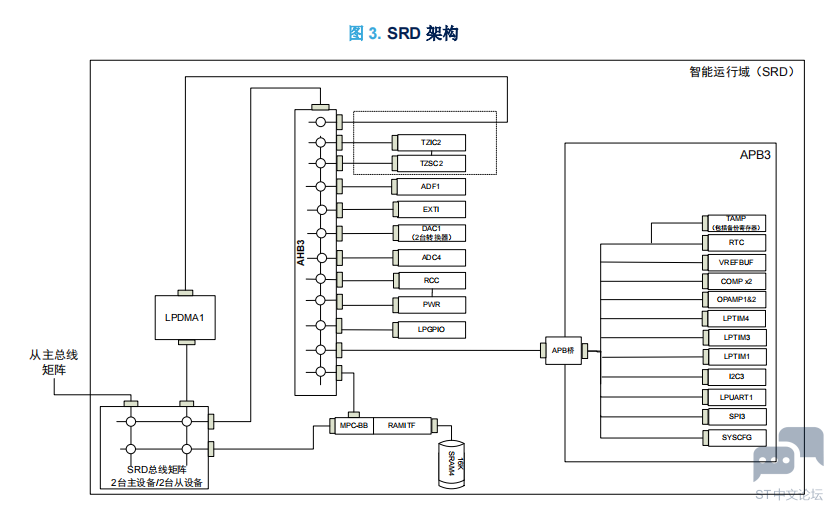

在停机 0 和停机 1 模式下,CPU 域和 SmartRun 域完全供电,而且均可支持 LPBAM 的动态活动。然后可以使用GPDMA1 和 LPDMA1 两者。GPDMA1 可以访问所有设备 SRAM,而 LPDMA1 只能访问 SRAM4。/ K" c j$ m+ _5 C1 \ 在停机 2 模式下,CPU 域处于低泄漏模式,禁止任何动态活动。借助 LPBAM,只有 SmartRun 域完全供电并且可以维持动态活动。只能使用 LPDMA1,其只能访问 SRAM4。LPDMA1 链表项和外设数据缓冲区均须位于 SRAM4中。本应用笔记重点介绍停机 2 模式下的 LPBAM,因为这是最有效的节能源模式。* D9 z2 R2 Z$ {" [/ U9 j' ] 警告: 在停机 0 和停机 1 模式下,映射到 AHB3 和 APB3(属于 SmartRun 域)的自主外设只能与 LPDMA1 和 SRAM4一起使用。主要原因在于当 SRD 外设请求总线时钟时,AHB 和 APB 时钟仅分布在 SmartRun 域中,而不是CPU 域中。6 e. `0 y( K% n 3.1.1 停机 0、停机 1 或停机 2 模式下 LPBAM 活动期间 SRD 中的时钟分布0 X1 p* R0 G8 Z2 O) I y 自主外设可请求其时钟(内核时钟或总线时钟),使其能正常工作,在工作完毕后会自动恢复到默认的关闭时钟状态(STOP 状态)来降低功耗(LSE 和 LSI 低功耗低速振荡器除外)。" w3 u6 h9 J/ p$ a4 W$ B$ M 在停机 2 模式中,只有 SmartRun 域中的外设可正常工作,时钟在该域中运行。下图放大了 SRD 架构,显示了在停机 2 模式下正常工作的所有外设。- l2 G9 S* d9 P9 z! ?

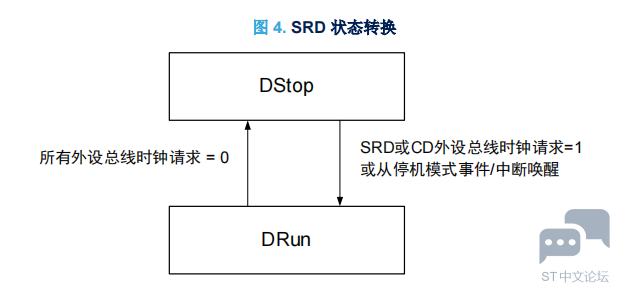

SmartRun 域可以具有两种状态:5 [9 k2 t# K# Z3 u2 m6 j$ J • SRD 处于 DStop 状态:不存在 AHB3/APB3 时钟。9 b3 K7 G; Z, N9 C! a • SRD 处于 DRun 状态:AHB3/APB3 时钟存在,并在停机模式下分配给所有在 RCC 中启用的 SRD 外设(参见表 4)。 / ?- W5 E w3 p z; f 4 @8 {1 O( k# z7 a* C' I

提示 通过设置 PWR-CR2 中的 SRDRUN 位,可强制使 SRD 始终处于 DRun 状态。" n! p+ x1 f0 O1 A) I: e1 p: N 下表详细介绍了域状态和时钟分布。0 q L# _* S9 [: R' c" J7 } & g2 c& d( H7 `; ~/ d

警告: 对于任何需要在停机 0、停机 1 或停机 2 模式期间正常工作或由 LPDMA1 访问的 SRD 外设,都须使用在RCC_AHB3ENR/RCC_APB3ENR、RCC_AHB3SMENR/RCC_APB3SMENR 和 RCC_SRDAMR 寄存器中设置的三个使能位进行配置。* l8 g! H. x" w: T" j2 z 完整版请查看:附件 |

zh.DM00779638.pdf

下载2.12 MB, 下载次数: 9

STM32U5低功耗测试

STM32怎么选型

内存配置的艺术:STM32为嵌入式系统高端UI优化RAM和闪存的三大策略

【STM32U545】实现CAN数据收发

【我的STM32U5 项目秀】+04-MPU6050在STM32U5上的移植

实战经验 | 基于 STM32U5 创建 USBx_CustomHID 通信

STM32U5 x E-BIKE,记录你的骑行多巴胺

基于STM32U5系列TIMER+DMA+DAC应用经验分享

实战经验 | 基于 STM32U5 片内温度传感器正确测算温度

【文末有礼】新款STM32U5:让便携产品拥有惊艳图效

微信公众号

微信公众号

手机版

手机版