.png) STMCU小助手

发布时间:2023-2-26 18:58

STMCU小助手

发布时间:2023-2-26 18:58

|

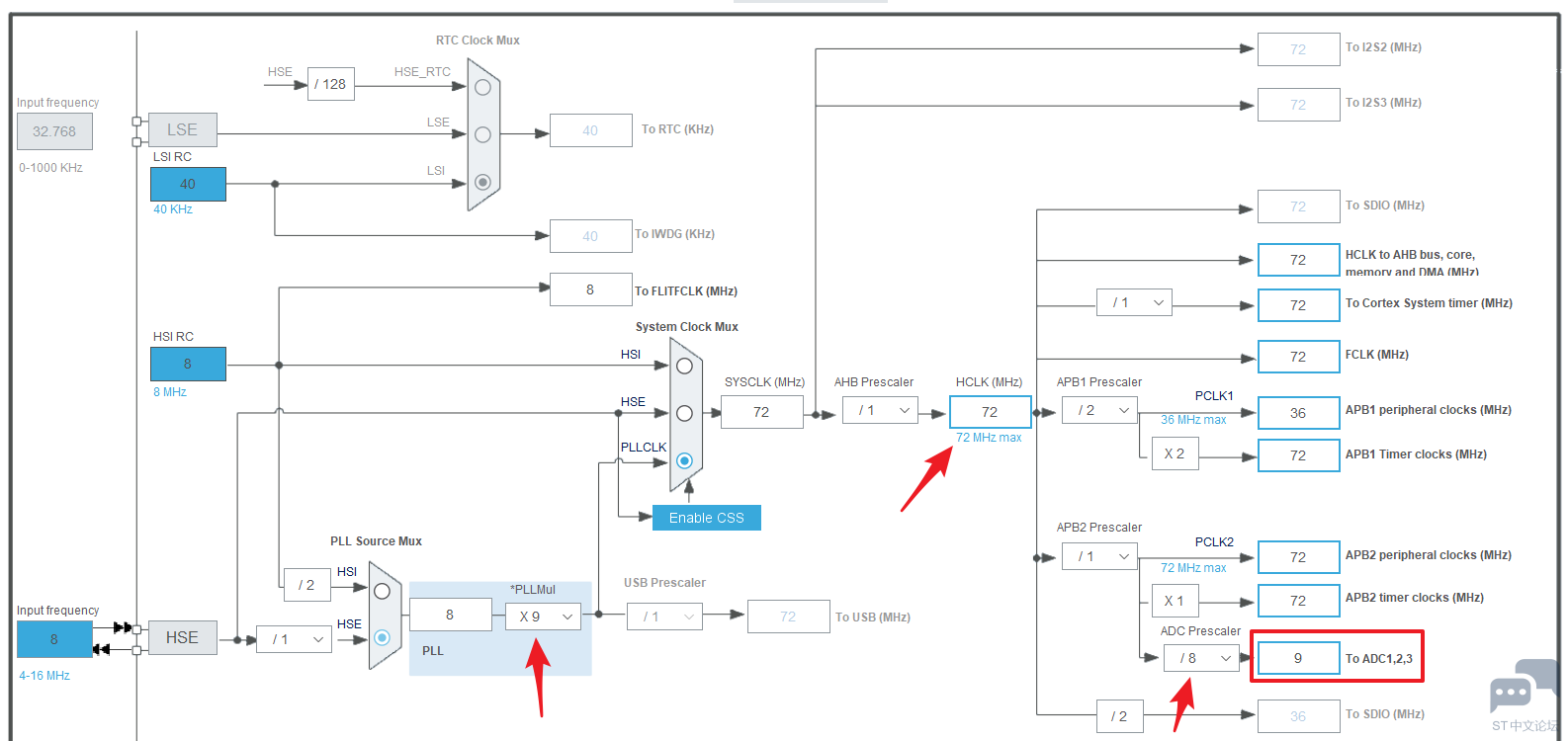

最大采样率 如果设置PLCK2为6分频,那么ADCCLK为:72M/6=12MHz。在外部晶振为8MHZ的情况下,这是F103系列ADC得到的最大时钟频率。

最小采样周期为1.5个周期+12.5周期=14周期。 那么最大采样频率为:12MHZ/14周期=851.142KHZ≈851KHZ 也就是1s可以采样851K个数据,对于STM32F1这个采样率已经是最大能力了。

最小采样率 如果设置PLCK2为8分频,那么ADCCLK为:72M/8=9MHz。在外部晶振为8MHZ的情况下,这是F103系列ADC得到的最小时钟频率。

最大采样周期为239.5个周期+12.5周期=252周期。 那么最大采样频率为:9MHZ/252周期=35.714KHZ≈35.7KHZ 也就是1s可以采样35.7K个数据,对于STM32F1这个采样率时其最小的采样能力。

———————————————— 版权声明:果果小师弟 |

实战经验 | MC SDK V6.x软件HSO功能ADC采样设计说明

经验分享 | 为什么重启ADC的DMA传输要先停掉ADC?

经验分享 | 为什么重启ADC的DMA传输要先停掉ADC?

经验分享 | STM32 ADC过采样话题

经验分享 | STM32双定时器+ADC+DMA实战案例

经验分享 | STM32U5系列TIMER+DMA+DAC应用演示

经验分享 | 基于STM32片内信号的ADC应用演示

经验分享 | STM32F0 ADC结果挪位的问题分析及解决

经验分享 | 三个 ADC 同步模式配置以及 CubeMx 错误配置的解决方法

经验分享 | 为什么ADC结果出现断层?

微信公众号

微信公众号

手机版

手机版