一、UART通信协议 E6 ?' V; n" x" r$ W* R- D' E$ M

UART通用异步收发器(Universal Asynchronous Receiver and Transmitter)是STM32 上常用的串行通信外设,可以灵活地与外部设备进行全双工数据交换,需要注意区别:

! J( c( ~. O+ \; _0 I

" J2 g' C4 N5 J& ]3 a" w& E 【1】USART-通用同步异步收发器(Universal Synchronous Asynchronous Receiver and Transmitter),UART是在USART上裁减了同步通信(时钟同步)的串行通信。0 o: h9 f: l6 E0 G5 r( n( F

1 Q7 S3 w" Y6 \# A$ W/ n+ r; Y! B

【2】串行通信和并行通信区别,串行通信是指设备之间通过一根数据信号线,地线以及控制信号线,按数据位形式一位一位地传输数据的通讯方式,同一时刻只能传输一位(bit)数据;并行通讯:是指使用 8 根或更多()的数据线进行传输的通讯方式,可以同一时刻传输多个数据位的数据(有多少根线就可以一次传输多少bit数据)。6 j3 y, y# U. k2 l

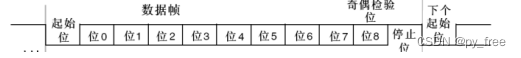

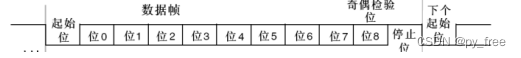

" E8 V# V9 g/ ~9 n* X 串行通信一般是以帧格式传输数据,即是一帧一帧的传输,每帧包含有起始信号、数据信息、校验信息(由我们自己设置)、停止信号。而每帧数据由二进制(0、1组成)转换为TTL电平对外发送,TTL电平中逻辑1采用2.4~5V电平标识,逻辑0采用0~0.5V电平标识。4 h6 r& P. |3 w2 T2 Z

5 _" N4 ?& h/ C$ h: O 串口通讯协议由启始位、主体数据、校验位以及停止位组成,通讯双方的数据包格式要约定一致(一样的起始位 数据 校验位 停止位)才能正常收发数据。. u5 G$ P- V) Z! e0 Z4 A

7 Y+ v' w* l' I I6 h4 U+ S 以传输一个字节数(8bit)为例,数据传输格式如下:! |7 w! S: X7 l% T h1 K* f# B3 x

# N3 _0 ^; A; w

1 ^! U( p, ^% b( R, B

1 ^! U( p, ^% b( R, B

2 s7 i+ W, N& M7 F2 k+ }4 u: T 【1】数据包从起始信号开始,直到停止信号结束。数据包的起始信号由一个逻辑 0 的数据位表示,而数据包的停止信号可由 0.5、1、1.5 或 2 个逻辑 1 的数据位表示:; a$ v$ f" e2 Y1 l% ?5 H% I

7 @' P! ]' ~$ f% c9 q. C5 j, ^# r 1个停止位:停止位位数的默认值。8 k: c! B( J+ O: K8 \* z! Q

1 j' }. l3 s5 S s2 e# G3 \+ b 2个停止位:可用于常规USART模式、单线模式以及调制解调器模式。

5 j! R$ y c+ `7 F( Z) G0 F$ ?! N4 I( V* E4 o* _1 E

0.5个停止位:在智能卡模式下接收数据时使用。

{9 h: o N8 F+ P9 W

J, |! t; B& N' K, j- y; a 1.5个停止位:在智能卡模式下发送和接收数据时使用。

* J) I+ g! N- t

( Y& ^* E% V, r: e3 v 【2】起始位和校验位中间的数据内容为真正需要传输的有效内容。

/ R8 T1 n. F$ X. N4 D0 E: N+ ?

7 K% }9 F; a. ~+ T+ Q 【3】奇偶校验位,指的是停止位前一bit的采用0或1值来标识偶校验还是奇校验。

$ y" T5 c8 X5 A( m- w7 g

! _2 D& ?+ x# ]6 ~ 偶校验,校验位值为0时,要求起始位和校验位中间的数据内容包含'1'的个数为偶数个。

6 |) R* D) w: |" p$ r g1 M9 }9 p/ z

奇校验,校验位值为1时,要求起始位和校验位中间的数据内容包含'1'的个数为奇数个。

" a/ Q/ j7 e, ~# I: Q: r+ ? M2 {- k8 a! O

注:奇偶校验位也是不严禁的,如果起始位和校验位中间的数据内容出现多次错误,例如先发送一个奇校验的01001100的数据,但是接收方得到01111100的奇校验数据,认为是正确的,但其实是出错了,这种情况是存在的,但概率会很少,毕竟单字节数发送,同时出现两个以上数据位错误的概率是极少的。通常我们在实际使用UART通信时,都不设置奇偶检验。& _# Z' [9 S% k5 X/ _) Z

6 l8 [2 V" [- B5 i1 `0 A

/ c; o7 Q$ D) N* ]$ C/ n3 H二、UART数据收发原理$ V" i2 a* o9 J! v0 @

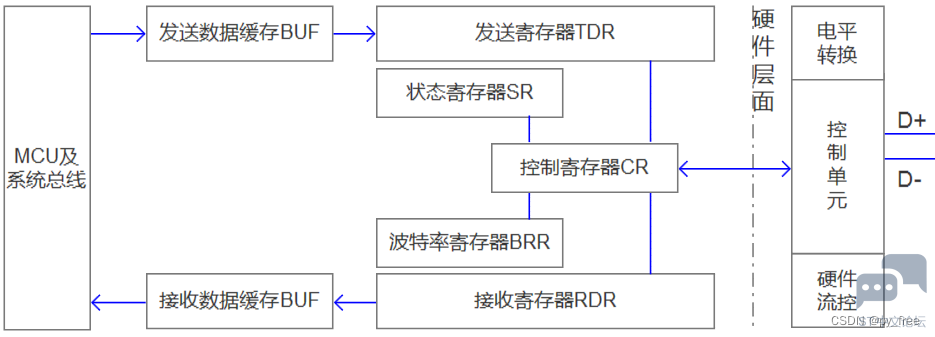

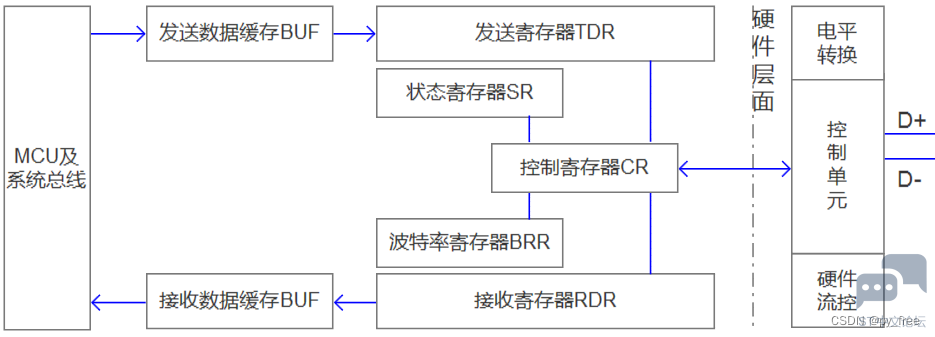

从数据转换层面上来说,UART数据收发主要涉及的几个寄存器,数据寄存器(Data Register)、控制寄存器(Control Register)、状态寄存器(Status Register)、波特率寄存器(BaudRate Register ),在HLA底层实现数据收发过程如下图。5 l2 X0 ^4 }* B0 v

* ]- ?8 T$ g' |" D" v: r5 f

+ `8 }# J/ n+ R V) s% {$ Y7 w/ Q

/ g ^+ F! i4 ~* h 2.1 数据寄存器UART_DR0 S, t- h" d/ M5 ~3 p2 y

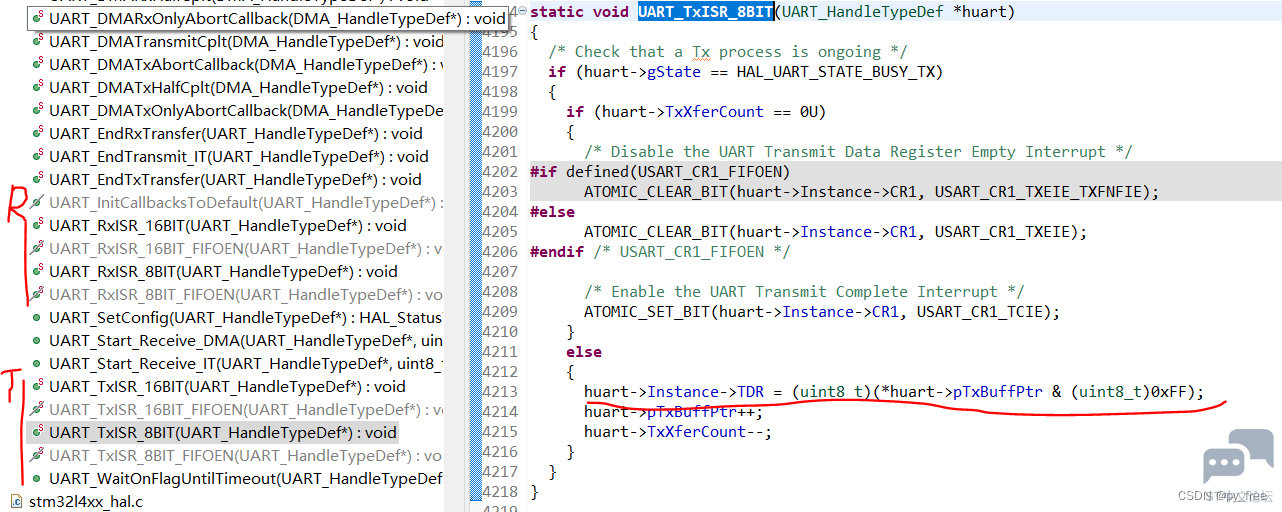

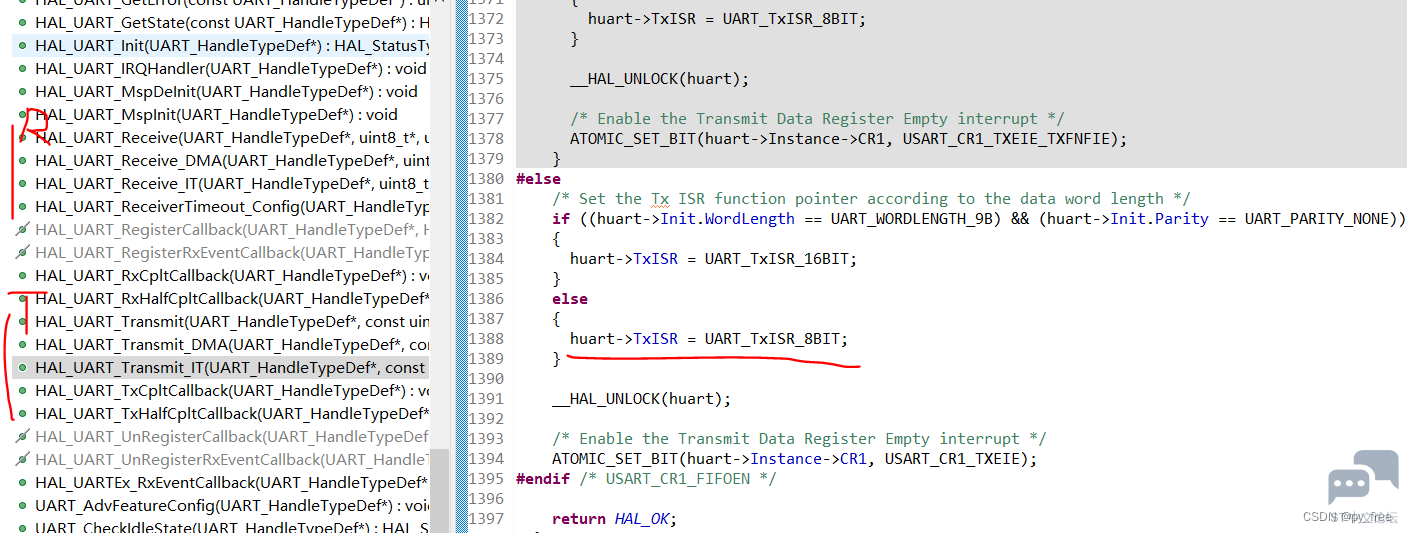

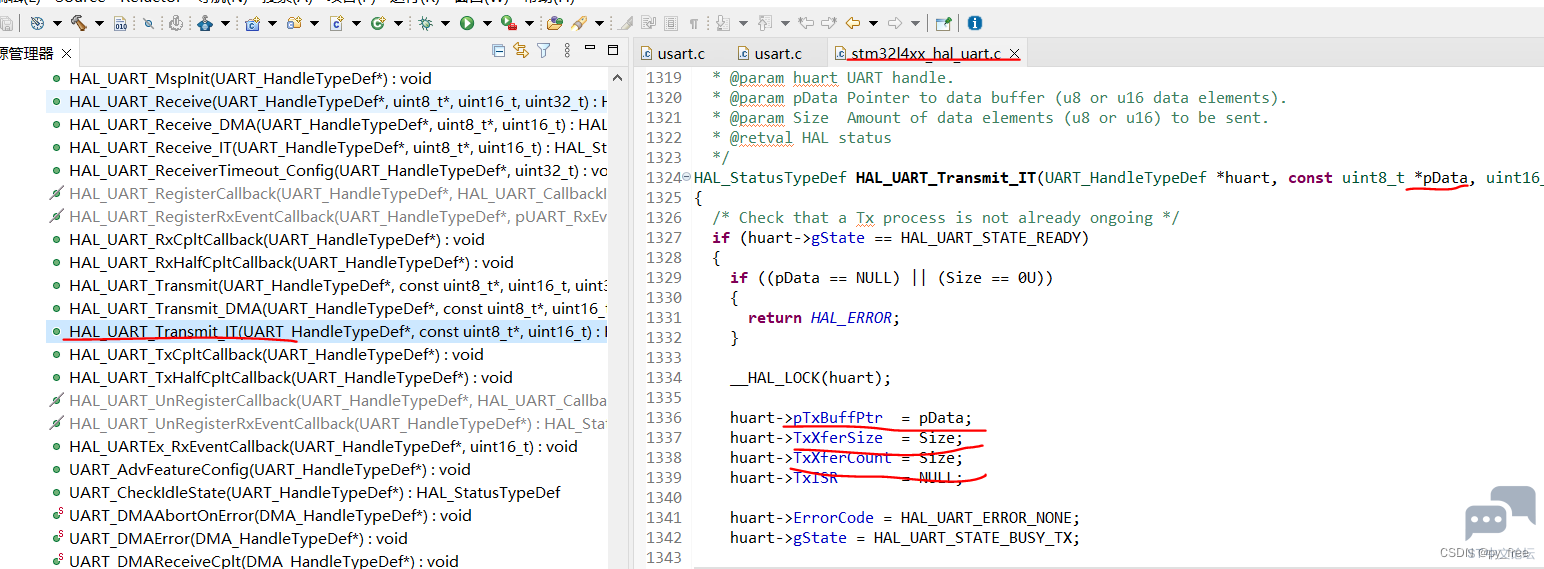

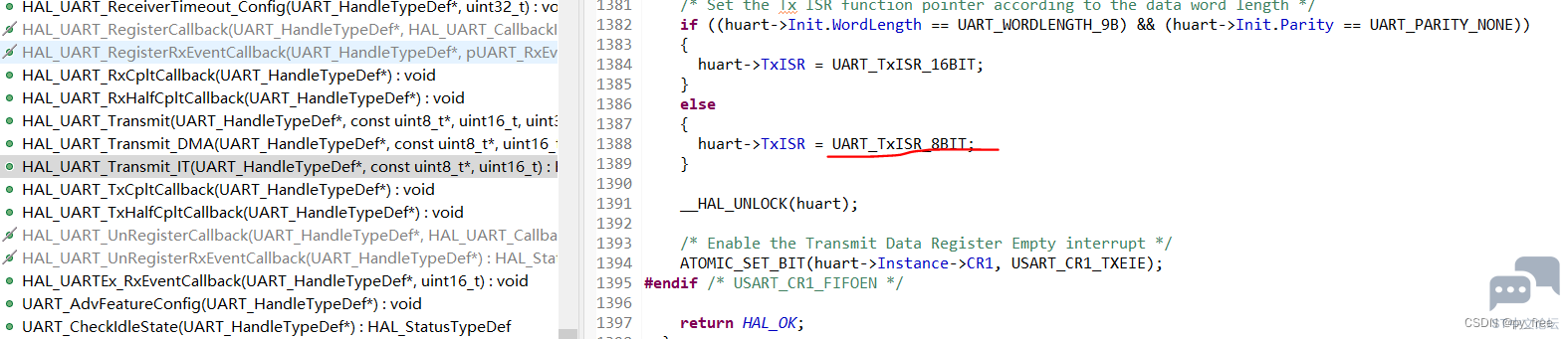

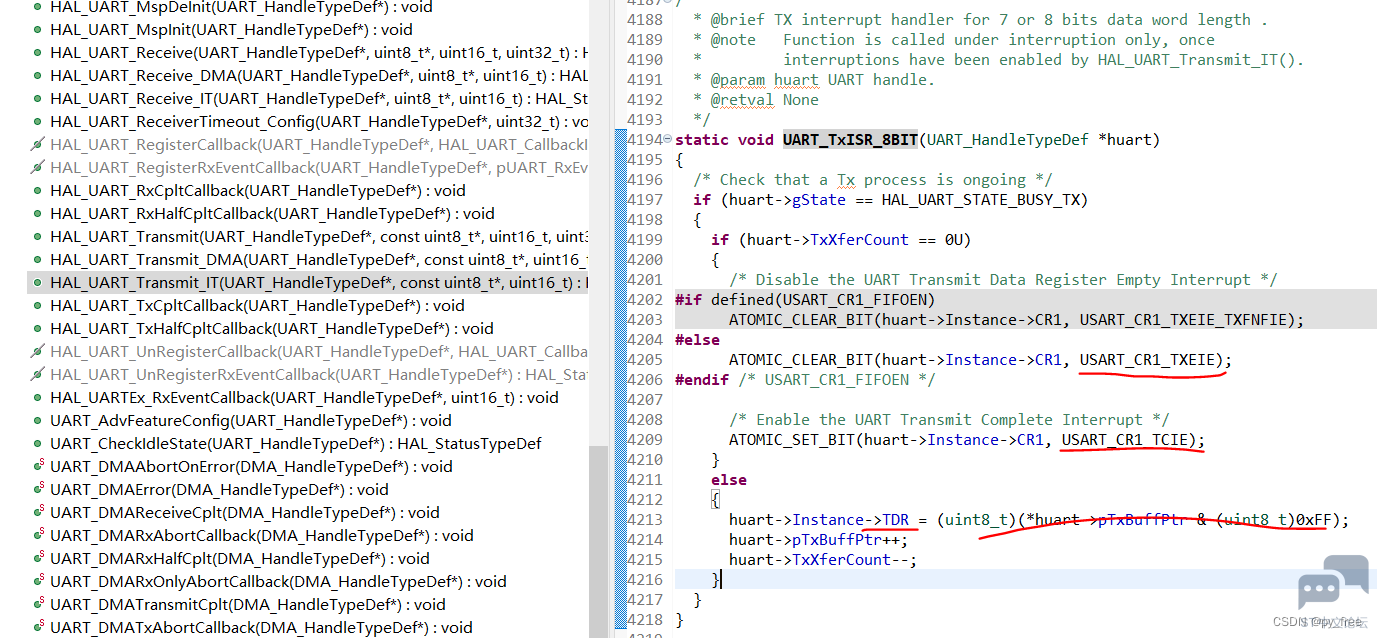

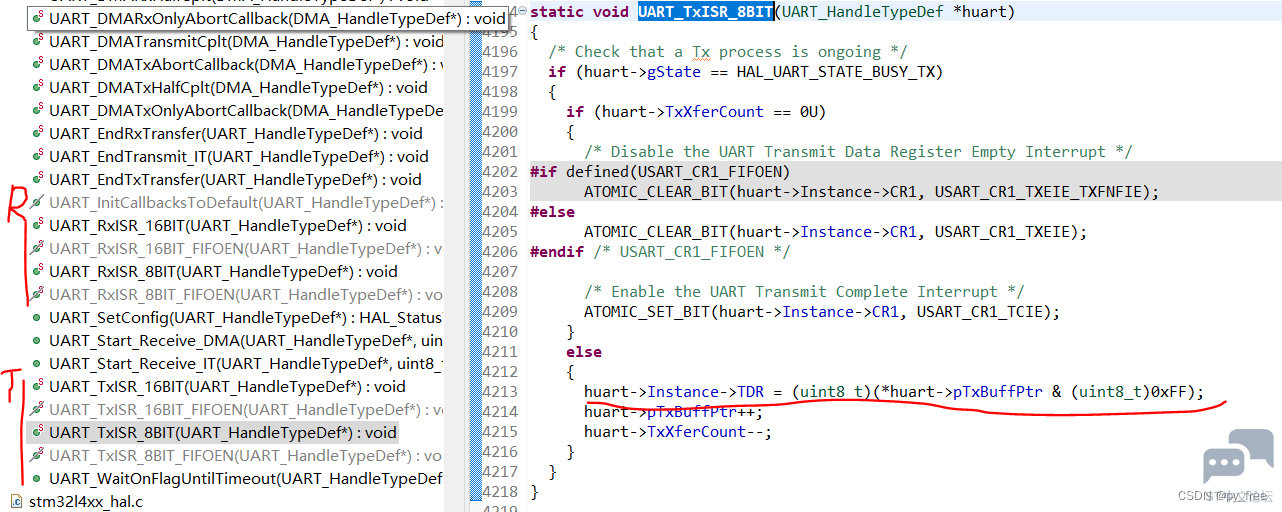

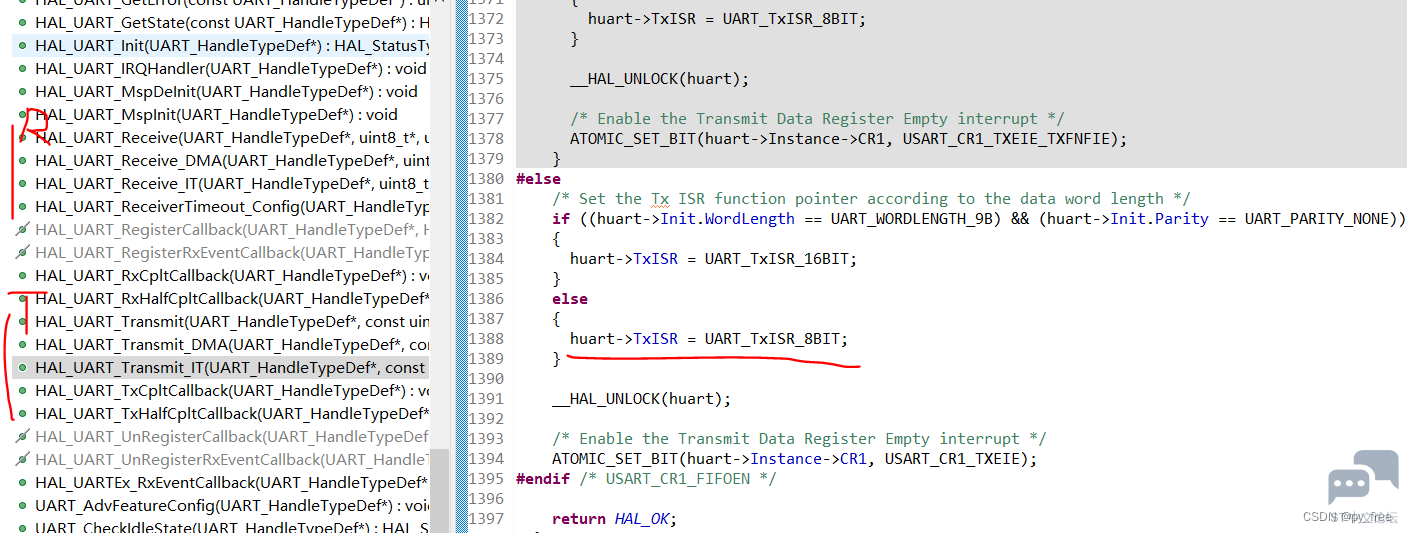

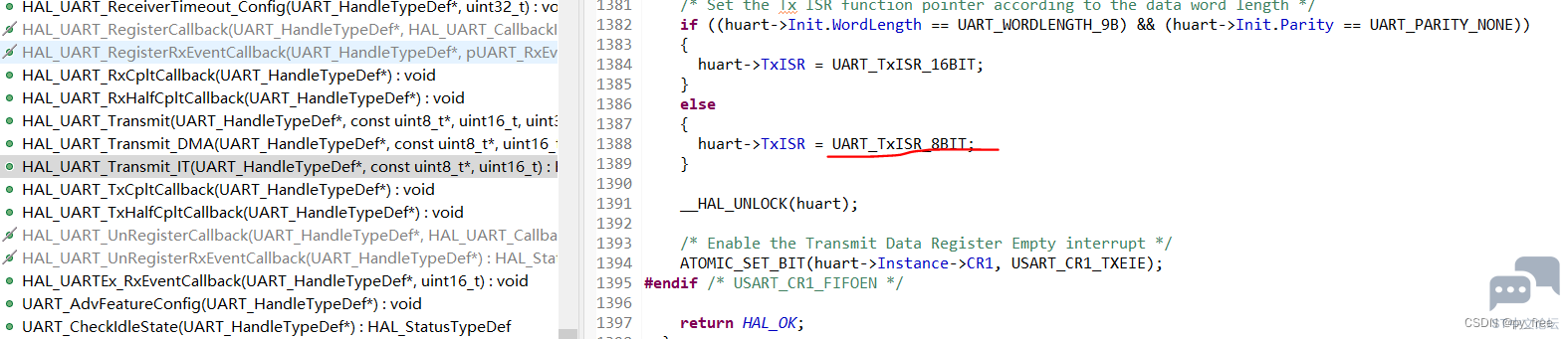

数据寄存器UART_DR,包含了发送和接收数据,通常由两个寄存器组成,一个用于发送的TDR,一个接收数据用的RDR,两个寄存器均具有读写功能,UART_DR寄存器与控制器寄存器(UART_CR)通信。在STM32-HAL库中关于UART通信实现驱动在stm32*_hal_uart.c文件中,UART数据从缓存区转换到DR寄存器是有UART的注册函数UART_TxISR_8BIT或UART_RxISR_8BIT实现的。

d1 @4 b) P0 A2 A% n

* Q e7 V: ~/ u9 R8 u9 j/ K1 f

* ?& W9 Q/ Y1 Z1 q$ k+ N, b

* ?& W9 Q/ Y1 Z1 q$ k+ N, b

9 \) g0 [! [! H0 y. V 而注册函数UART_TxISR_8BIT调用是由更上层的HAL发送函数HAL_UART_Transmit*来传递的,接收类似。

& [8 }" k, R( h; ]6 ^# `1 H# ^, r0 g) b

4 Z, j( g. B* C7 }

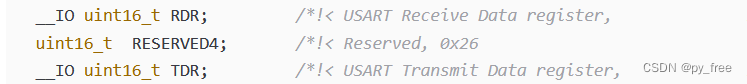

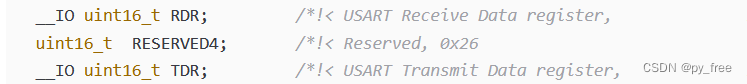

& E0 R% j! d' I 数据发送寄存器UART_TDR和数据接收寄存器UART_RDR在HLA库中是16bit宽度的存储区域。

% h* s1 f" o3 ?2 M- s$ b/ C5 w M

( f- y4 N: D5 V! R( f* S

% \$ X* D4 f0 V# C9 x9 f

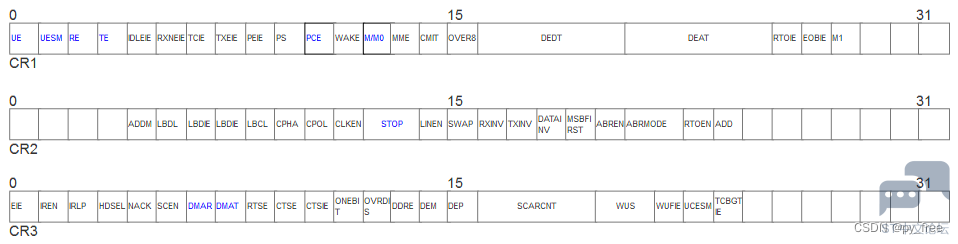

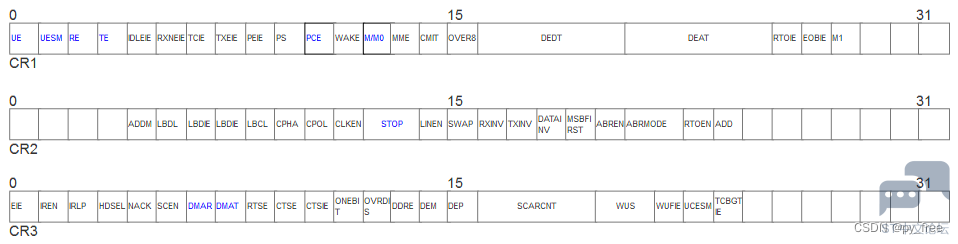

- n. h4 y' f N 2.2 控制寄存器UART_CR

0 `' f5 p* b3 v( @) T5 S 控制寄存器UART_CR,由三个32bit宽度的数据组成(CR1、CR2、CR3),共96bit数据,每个BIT都具有明确定义。UART_CR会一次从UART_TDR读取8数据位宽度的数据,即一个字节数据,然后按位转换成TTL电平发送。* u3 X$ e5 S, ^) Z$ E( L: {

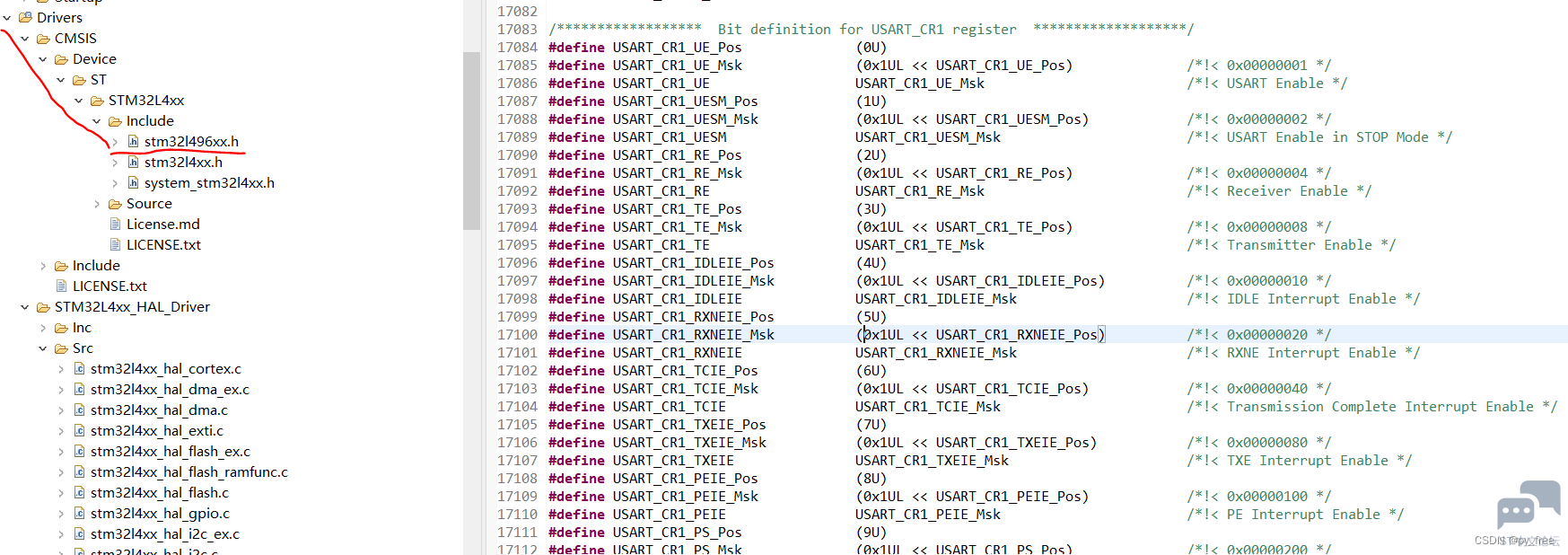

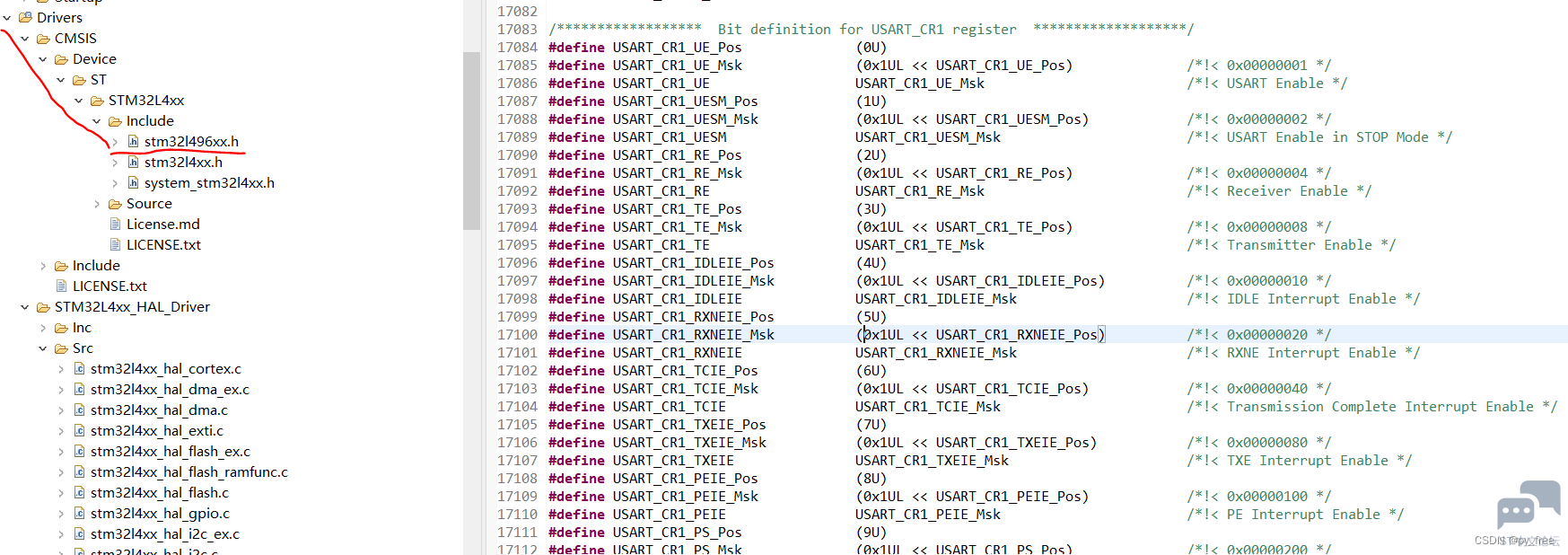

8 P6 d1 Z8 `( e9 X( F 控制寄存器CR1、CR2、CR3的定义在stm32-HAL驱动实现中,是根据芯片型号不同,各个字段定义有所区别,因此CR1、CR2、CR3的每个bit定义存放在CMSIS(微控制器软件接口标准)和芯片序列相关的头文件内,例如stm32l496xx.h。" ^( q1 o( L6 B

& N- K- \. Q$ @- u2 j4 |) X

8 L, n2 Z* S7 E! g

8 L, n2 Z* S7 E! g

+ X- L9 d9 y9 i& P 关于CR1、CR2、CR3的每个bit定义及相关数值含义可以在上述描述的头文件中查看,例如stm32l496xx.h的定义如下。

: D7 t- x4 G7 A$ [4 U- Q+ G- /****************** Bit definition for USART_CR1 register *******************/8 k0 u: k* x& k

- #define USART_CR1_UE_Pos (0U) g" ] M: Q. N5 x$ d. c6 N

- #define USART_CR1_UE_Msk (0x1UL << USART_CR1_UE_Pos) /*!< 0x00000001 */6 {+ o$ `# [ p+ U {' k$ V: y1 T

- #define USART_CR1_UE USART_CR1_UE_Msk /*!< USART Enable */

4 ^* y; Y) Z/ j5 k# s - #define USART_CR1_UESM_Pos (1U)& W8 ~% j' L; ^7 ~ ]( H: N

- #define USART_CR1_UESM_Msk (0x1UL << USART_CR1_UESM_Pos) /*!< 0x00000002 */

. ^+ U" C' A* x# f - #define USART_CR1_UESM USART_CR1_UESM_Msk /*!< USART Enable in STOP Mode */

2 q; u, l% \: c' w# h4 q4 O - #define USART_CR1_RE_Pos (2U)

! H3 T, `: H% g# y4 Z& v- c - #define USART_CR1_RE_Msk (0x1UL << USART_CR1_RE_Pos) /*!< 0x00000004 */

* c" E1 `2 n! H' R( j& J; T - #define USART_CR1_RE USART_CR1_RE_Msk /*!< Receiver Enable */

, ^5 ^) Y, Q: ]5 Q - #define USART_CR1_TE_Pos (3U)

7 n% W7 ?. d; q- v2 \ - #define USART_CR1_TE_Msk (0x1UL << USART_CR1_TE_Pos) /*!< 0x00000008 */

1 ?0 n( @% f7 _8 q7 E1 R - #define USART_CR1_TE USART_CR1_TE_Msk /*!< Transmitter Enable */, N7 f8 s) U. u, e- z1 P' V

- #define USART_CR1_IDLEIE_Pos (4U)

4 O: |& N( f X' z7 L - #define USART_CR1_IDLEIE_Msk (0x1UL << USART_CR1_IDLEIE_Pos) /*!< 0x00000010 */: a& o' ^4 [; H" {" G o6 I3 L

- #define USART_CR1_IDLEIE USART_CR1_IDLEIE_Msk /*!< IDLE Interrupt Enable *// y2 m, R. A! P& ~$ }

- #define USART_CR1_RXNEIE_Pos (5U)

$ T0 r7 x8 y0 G8 u9 R9 }& T$ Z0 x2 S - #define USART_CR1_RXNEIE_Msk (0x1UL << USART_CR1_RXNEIE_Pos) /*!< 0x00000020 */

0 G; N" |& P& m" b0 o$ Q - #define USART_CR1_RXNEIE USART_CR1_RXNEIE_Msk /*!< RXNE Interrupt Enable */

+ T7 ~ g9 u9 ~ - #define USART_CR1_TCIE_Pos (6U)

- r5 f- Z- p6 _! C. S# f - #define USART_CR1_TCIE_Msk (0x1UL << USART_CR1_TCIE_Pos) /*!< 0x00000040 */2 J0 }! ]+ D7 ^4 t

- #define USART_CR1_TCIE USART_CR1_TCIE_Msk /*!< Transmission Complete Interrupt Enable */0 M1 d6 D- ?2 W9 E

- #define USART_CR1_TXEIE_Pos (7U)+ A: J& M8 K& i# D1 h* \

- #define USART_CR1_TXEIE_Msk (0x1UL << USART_CR1_TXEIE_Pos) /*!< 0x00000080 */

/ Q9 O; `% ^3 Y0 w& ]$ I - #define USART_CR1_TXEIE USART_CR1_TXEIE_Msk /*!< TXE Interrupt Enable */0 L: D1 S: t2 s' [

- #define USART_CR1_PEIE_Pos (8U)1 w- Z( H' i$ m; V# d1 x

- #define USART_CR1_PEIE_Msk (0x1UL << USART_CR1_PEIE_Pos) /*!< 0x00000100 */+ ^( h4 ?4 [- Y8 f# v! _

- #define USART_CR1_PEIE USART_CR1_PEIE_Msk /*!< PE Interrupt Enable */9 S- O- C4 g* i' a1 h) ?, X

- #define USART_CR1_PS_Pos (9U)

* b6 x3 x, I* Y1 n$ `5 ` - #define USART_CR1_PS_Msk (0x1UL << USART_CR1_PS_Pos) /*!< 0x00000200 */

, l& y5 C% H @. J1 s6 p - #define USART_CR1_PS USART_CR1_PS_Msk /*!< Parity Selection */

8 r2 d) K0 \# Q- O l8 z1 t3 m - #define USART_CR1_PCE_Pos (10U). z% t* x( J1 B

- #define USART_CR1_PCE_Msk (0x1UL << USART_CR1_PCE_Pos) /*!< 0x00000400 */! a$ ]% B2 m3 L8 y- \) r1 b% n

- #define USART_CR1_PCE USART_CR1_PCE_Msk /*!< Parity Control Enable */

! X1 Q& h" y& j" K - #define USART_CR1_WAKE_Pos (11U)

0 D- P1 D2 K1 g/ p3 `* H5 j - #define USART_CR1_WAKE_Msk (0x1UL << USART_CR1_WAKE_Pos) /*!< 0x00000800 */2 x T" b$ }. K) U

- #define USART_CR1_WAKE USART_CR1_WAKE_Msk /*!< Receiver Wakeup method */

2 g# `# y& [; Y9 } - #define USART_CR1_M_Pos (12U)( p% I3 x! C, l5 b7 a; j

- #define USART_CR1_M_Msk (0x10001UL << USART_CR1_M_Pos) /*!< 0x10001000 */1 W; @1 K1 I* Q# S1 [

- #define USART_CR1_M USART_CR1_M_Msk /*!< Word length */

# j' a) [/ {/ ` V - #define USART_CR1_M0_Pos (12U)

$ S- I( d/ a0 Y' g - #define USART_CR1_M0_Msk (0x1UL << USART_CR1_M0_Pos) /*!< 0x00001000 */, F4 l, {0 j5 A

- #define USART_CR1_M0 USART_CR1_M0_Msk /*!< Word length - Bit 0 */7 T" e0 `1 T1 y8 G$ s7 [ ]& t3 m

- #define USART_CR1_MME_Pos (13U): W) q2 M+ V/ B* r' a

- #define USART_CR1_MME_Msk (0x1UL << USART_CR1_MME_Pos) /*!< 0x00002000 */7 @4 O9 H9 [9 F+ K# j& W% f0 ], x* T- E8 o

- #define USART_CR1_MME USART_CR1_MME_Msk /*!< Mute Mode Enable */$ H$ p, F7 k8 k

- #define USART_CR1_CMIE_Pos (14U)% h) W% [% D/ Q e* S& a" J

- #define USART_CR1_CMIE_Msk (0x1UL << USART_CR1_CMIE_Pos) /*!< 0x00004000 */* [$ A% @7 M2 h* u2 U- t

- #define USART_CR1_CMIE USART_CR1_CMIE_Msk /*!< Character match interrupt enable */

, C O+ e, O/ [1 c* u y - #define USART_CR1_OVER8_Pos (15U)7 y/ b" }+ {* S! L! ^

- #define USART_CR1_OVER8_Msk (0x1UL << USART_CR1_OVER8_Pos) /*!< 0x00008000 */

9 H* a: J; q% @. N - #define USART_CR1_OVER8 USART_CR1_OVER8_Msk /*!< Oversampling by 8-bit or 16-bit mode */

* I6 P. |2 m8 d! \2 X$ S! v - #define USART_CR1_DEDT_Pos (16U)( R" w) N$ u$ A; s. A1 Z8 a Z

- #define USART_CR1_DEDT_Msk (0x1FUL << USART_CR1_DEDT_Pos) /*!< 0x001F0000 */

& O9 N, ~# q; e* g! d3 y- A( v - #define USART_CR1_DEDT USART_CR1_DEDT_Msk /*!< DEDT[4:0] bits (Driver Enable Deassertion Time) */

1 M" `2 `1 B. h- W5 m - #define USART_CR1_DEDT_0 (0x01UL << USART_CR1_DEDT_Pos) /*!< 0x00010000 */3 j1 ~5 M7 J+ F) q$ b& c+ Y4 n

- #define USART_CR1_DEDT_1 (0x02UL << USART_CR1_DEDT_Pos) /*!< 0x00020000 */

0 D4 z) U: m& x6 y1 F% O - #define USART_CR1_DEDT_2 (0x04UL << USART_CR1_DEDT_Pos) /*!< 0x00040000 */

. S* r' X0 w. W7 J/ A% Q& a - #define USART_CR1_DEDT_3 (0x08UL << USART_CR1_DEDT_Pos) /*!< 0x00080000 */

) ^7 `# T. e* q - #define USART_CR1_DEDT_4 (0x10UL << USART_CR1_DEDT_Pos) /*!< 0x00100000 */5 X/ N* P- F% ~. C7 i6 s

- #define USART_CR1_DEAT_Pos (21U)6 U3 B9 ` c& f

- #define USART_CR1_DEAT_Msk (0x1FUL << USART_CR1_DEAT_Pos) /*!< 0x03E00000 */

4 s+ c+ i# Z3 l - #define USART_CR1_DEAT USART_CR1_DEAT_Msk /*!< DEAT[4:0] bits (Driver Enable Assertion Time) */

1 P* e+ O7 i0 M - #define USART_CR1_DEAT_0 (0x01UL << USART_CR1_DEAT_Pos) /*!< 0x00200000 */4 B# H! E$ p0 U, S+ w/ z

- #define USART_CR1_DEAT_1 (0x02UL << USART_CR1_DEAT_Pos) /*!< 0x00400000 */

! M; ^! j, M; y: r, e# ` - #define USART_CR1_DEAT_2 (0x04UL << USART_CR1_DEAT_Pos) /*!< 0x00800000 *// v6 [' T; e1 @' j. [

- #define USART_CR1_DEAT_3 (0x08UL << USART_CR1_DEAT_Pos) /*!< 0x01000000 */5 b ` z! {( w7 r; A- c" t: w

- #define USART_CR1_DEAT_4 (0x10UL << USART_CR1_DEAT_Pos) /*!< 0x02000000 */+ x; h0 z, A. \, ?4 _& T

- #define USART_CR1_RTOIE_Pos (26U)" P2 E/ w* ?# B$ s/ v& Y. P

- #define USART_CR1_RTOIE_Msk (0x1UL << USART_CR1_RTOIE_Pos) /*!< 0x04000000 */" F, ^# d, {. M R) x# M2 M2 F

- #define USART_CR1_RTOIE USART_CR1_RTOIE_Msk /*!< Receive Time Out interrupt enable */6 J% Q+ S0 r4 I$ h

- #define USART_CR1_EOBIE_Pos (27U)

3 b0 C3 n+ }4 z! O8 y7 v+ s8 \ - #define USART_CR1_EOBIE_Msk (0x1UL << USART_CR1_EOBIE_Pos) /*!< 0x08000000 */

Q9 x- } o) l) D$ r - #define USART_CR1_EOBIE USART_CR1_EOBIE_Msk /*!< End of Block interrupt enable */# `* ?4 ]' {* v1 r

- #define USART_CR1_M1_Pos (28U)

( g! k* s9 q! }$ k, ? - #define USART_CR1_M1_Msk (0x1UL << USART_CR1_M1_Pos) /*!< 0x10000000 */

8 c' w! g4 c3 j - #define USART_CR1_M1 USART_CR1_M1_Msk /*!< Word length - Bit 1 */

; Z. v1 S' d1 |6 b3 P - ; d! l1 }$ a# V' K5 c1 O( [) r

- /****************** Bit definition for USART_CR2 register *******************/! Z4 v5 F& t+ k3 U( ^

- #define USART_CR2_ADDM7_Pos (4U); g% A! I2 e0 d. d

- #define USART_CR2_ADDM7_Msk (0x1UL << USART_CR2_ADDM7_Pos) /*!< 0x00000010 */

; W( o0 [! a! s; x$ y - #define USART_CR2_ADDM7 USART_CR2_ADDM7_Msk /*!< 7-bit or 4-bit Address Detection */- I* G; `) q# N- O, ^8 b6 S4 S0 d6 F

- #define USART_CR2_LBDL_Pos (5U)$ C; V8 E2 M9 I! p5 z3 E. C% G

- #define USART_CR2_LBDL_Msk (0x1UL << USART_CR2_LBDL_Pos) /*!< 0x00000020 */. ]! r) c% e! `$ P: {* r0 s

- #define USART_CR2_LBDL USART_CR2_LBDL_Msk /*!< LIN Break Detection Length */

) e6 w( W; e+ I, Y: b9 s7 n& k - #define USART_CR2_LBDIE_Pos (6U)

0 a- E7 W9 e" ~- ^# a - #define USART_CR2_LBDIE_Msk (0x1UL << USART_CR2_LBDIE_Pos) /*!< 0x00000040 */

0 ?2 s8 i9 N% u" n P" g& ~) i - #define USART_CR2_LBDIE USART_CR2_LBDIE_Msk /*!< LIN Break Detection Interrupt Enable */

N& h5 F& B8 E; m. z - #define USART_CR2_LBCL_Pos (8U)

, ~/ D" N) }% w - #define USART_CR2_LBCL_Msk (0x1UL << USART_CR2_LBCL_Pos) /*!< 0x00000100 */

4 [3 s" a4 {/ [' E# S( ? - #define USART_CR2_LBCL USART_CR2_LBCL_Msk /*!< Last Bit Clock pulse */% b) ? q( M# i1 g

- #define USART_CR2_CPHA_Pos (9U)/ B" ~* i: m* g

- #define USART_CR2_CPHA_Msk (0x1UL << USART_CR2_CPHA_Pos) /*!< 0x00000200 */

" Q* x& t: z; p - #define USART_CR2_CPHA USART_CR2_CPHA_Msk /*!< Clock Phase */

0 ]" g1 o+ P0 `$ v& c4 F" {/ G2 F - #define USART_CR2_CPOL_Pos (10U), [7 o$ P t o: c4 W; R" O% W

- #define USART_CR2_CPOL_Msk (0x1UL << USART_CR2_CPOL_Pos) /*!< 0x00000400 */: t( s+ {' J/ Y0 \! x# X

- #define USART_CR2_CPOL USART_CR2_CPOL_Msk /*!< Clock Polarity */

4 Y/ b9 ?7 ^! F - #define USART_CR2_CLKEN_Pos (11U)

) X! G- q8 v+ |; B" \0 t0 | - #define USART_CR2_CLKEN_Msk (0x1UL << USART_CR2_CLKEN_Pos) /*!< 0x00000800 */

, m4 n: l) I* L0 M" v; z) ` - #define USART_CR2_CLKEN USART_CR2_CLKEN_Msk /*!< Clock Enable */

; I1 L/ x4 `6 b' F) W6 x - #define USART_CR2_STOP_Pos (12U)

$ H( v4 T! a+ j - #define USART_CR2_STOP_Msk (0x3UL << USART_CR2_STOP_Pos) /*!< 0x00003000 */

! S6 r+ }6 F# F! _: L- S0 M# O: R% C - #define USART_CR2_STOP USART_CR2_STOP_Msk /*!< STOP[1:0] bits (STOP bits) */6 a# q F- T$ y+ i/ l* T7 t9 ^0 P1 Y4 F; m

- #define USART_CR2_STOP_0 (0x1UL << USART_CR2_STOP_Pos) /*!< 0x00001000 */

" p0 v0 p* }. c - #define USART_CR2_STOP_1 (0x2UL << USART_CR2_STOP_Pos) /*!< 0x00002000 */

. F8 W4 S# q1 _) w8 W - #define USART_CR2_LINEN_Pos (14U)8 y! W" k. ~) ^+ w: q

- #define USART_CR2_LINEN_Msk (0x1UL << USART_CR2_LINEN_Pos) /*!< 0x00004000 */0 |1 c$ `* T- E7 F: d, t7 P J: \# c

- #define USART_CR2_LINEN USART_CR2_LINEN_Msk /*!< LIN mode enable */9 u {* b5 u' s8 g, t, K0 ~

- #define USART_CR2_SWAP_Pos (15U)

/ D+ x' E( E4 `1 B. C - #define USART_CR2_SWAP_Msk (0x1UL << USART_CR2_SWAP_Pos) /*!< 0x00008000 */

1 T/ j: R" p, ` - #define USART_CR2_SWAP USART_CR2_SWAP_Msk /*!< SWAP TX/RX pins */

) k% h# P! e& E6 } - #define USART_CR2_RXINV_Pos (16U)

/ r% _1 N) B+ f) z - #define USART_CR2_RXINV_Msk (0x1UL << USART_CR2_RXINV_Pos) /*!< 0x00010000 */" y$ l* y, V+ l- b! G# e+ I, }. m

- #define USART_CR2_RXINV USART_CR2_RXINV_Msk /*!< RX pin active level inversion */, c7 {, |, b9 T

- #define USART_CR2_TXINV_Pos (17U)- `5 ]4 I- d( C* }

- #define USART_CR2_TXINV_Msk (0x1UL << USART_CR2_TXINV_Pos) /*!< 0x00020000 */

2 H# E a$ B. Q0 h: B. h; _ - #define USART_CR2_TXINV USART_CR2_TXINV_Msk /*!< TX pin active level inversion */

9 l8 p8 h$ z* G - #define USART_CR2_DATAINV_Pos (18U)! I& N0 \( r4 G7 R

- #define USART_CR2_DATAINV_Msk (0x1UL << USART_CR2_DATAINV_Pos) /*!< 0x00040000 */- o. [9 d" z) z5 P) h

- #define USART_CR2_DATAINV USART_CR2_DATAINV_Msk /*!< Binary data inversion */

) G A+ L- A8 s# r: X - #define USART_CR2_MSBFIRST_Pos (19U)% \6 ^+ ~: [2 x8 d" j# G, H

- #define USART_CR2_MSBFIRST_Msk (0x1UL << USART_CR2_MSBFIRST_Pos) /*!< 0x00080000 */0 M6 F+ e0 H7 _# Q8 k

- #define USART_CR2_MSBFIRST USART_CR2_MSBFIRST_Msk /*!< Most Significant Bit First */' q7 d4 Y% Q2 B

- #define USART_CR2_ABREN_Pos (20U)

; `2 C# \' ?* G$ c; Y) P6 _- _$ V - #define USART_CR2_ABREN_Msk (0x1UL << USART_CR2_ABREN_Pos) /*!< 0x00100000 */

6 D0 Z; H/ H) P5 n5 g0 z* ` - #define USART_CR2_ABREN USART_CR2_ABREN_Msk /*!< Auto Baud-Rate Enable*/) h" G# E0 z8 z( K4 d

- #define USART_CR2_ABRMODE_Pos (21U)- N: D+ O3 q5 s6 M: D

- #define USART_CR2_ABRMODE_Msk (0x3UL << USART_CR2_ABRMODE_Pos) /*!< 0x00600000 */

" h& D& C: }; v( V. I5 W U7 K0 [ - #define USART_CR2_ABRMODE USART_CR2_ABRMODE_Msk /*!< ABRMOD[1:0] bits (Auto Baud-Rate Mode) */. J! q2 I0 P4 b i9 o. _

- #define USART_CR2_ABRMODE_0 (0x1UL << USART_CR2_ABRMODE_Pos) /*!< 0x00200000 */

# V. X' n1 C4 x) v" \: t* q - #define USART_CR2_ABRMODE_1 (0x2UL << USART_CR2_ABRMODE_Pos) /*!< 0x00400000 */- D# U- Z1 ]" W9 x0 f* T. c0 n

- #define USART_CR2_RTOEN_Pos (23U)

8 ~4 O; P' [+ s' E& i - #define USART_CR2_RTOEN_Msk (0x1UL << USART_CR2_RTOEN_Pos) /*!< 0x00800000 */

, \7 E5 t6 p" }& z - #define USART_CR2_RTOEN USART_CR2_RTOEN_Msk /*!< Receiver Time-Out enable */9 H6 C" i. f a, I) z6 `- [

- #define USART_CR2_ADD_Pos (24U)/ i2 i* G. s' w, D* F( v

- #define USART_CR2_ADD_Msk (0xFFUL << USART_CR2_ADD_Pos) /*!< 0xFF000000 */

0 G- W& ]$ D' W. L: j - #define USART_CR2_ADD USART_CR2_ADD_Msk /*!< Address of the USART node */$ l0 x+ _ ^9 z* ?) Q

- 5 E( B' Q8 Z% j/ Q" V: ?7 P, { ^

- /****************** Bit definition for USART_CR3 register *******************/

8 Z. H& e/ C+ U6 U6 F - #define USART_CR3_EIE_Pos (0U)

8 `, A( A9 c8 [' Y7 T - #define USART_CR3_EIE_Msk (0x1UL << USART_CR3_EIE_Pos) /*!< 0x00000001 */ h; u u6 a- |: i" [

- #define USART_CR3_EIE USART_CR3_EIE_Msk /*!< Error Interrupt Enable */

5 U; Q! |9 h( q7 Q - #define USART_CR3_IREN_Pos (1U)

. \3 u! h- B9 O! T - #define USART_CR3_IREN_Msk (0x1UL << USART_CR3_IREN_Pos) /*!< 0x00000002 */+ F- m N; K6 s" U+ R% x

- #define USART_CR3_IREN USART_CR3_IREN_Msk /*!< IrDA mode Enable */

; s+ U/ N. n) Z - #define USART_CR3_IRLP_Pos (2U). h6 g1 G# }: i' W2 [

- #define USART_CR3_IRLP_Msk (0x1UL << USART_CR3_IRLP_Pos) /*!< 0x00000004 */: N* W( r1 M1 P; g

- #define USART_CR3_IRLP USART_CR3_IRLP_Msk /*!< IrDA Low-Power */

5 u0 G* o7 i9 U3 c5 d1 G9 h - #define USART_CR3_HDSEL_Pos (3U)8 l! m* Y6 K$ A7 ~# M

- #define USART_CR3_HDSEL_Msk (0x1UL << USART_CR3_HDSEL_Pos) /*!< 0x00000008 */' D' W( O$ r' ~! }9 L3 M7 Z

- #define USART_CR3_HDSEL USART_CR3_HDSEL_Msk /*!< Half-Duplex Selection */

# ~- f# D: {1 B! _ - #define USART_CR3_NACK_Pos (4U)

" y, ~& _0 ?/ Q2 O' z - #define USART_CR3_NACK_Msk (0x1UL << USART_CR3_NACK_Pos) /*!< 0x00000010 */: V$ F+ b! D" T

- #define USART_CR3_NACK USART_CR3_NACK_Msk /*!< SmartCard NACK enable */0 D/ P/ k* s! c1 c

- #define USART_CR3_SCEN_Pos (5U), ?, |$ O6 q5 B# X4 @; N7 d5 i

- #define USART_CR3_SCEN_Msk (0x1UL << USART_CR3_SCEN_Pos) /*!< 0x00000020 */1 _0 q+ ~# h8 ^2 i; x( v0 U

- #define USART_CR3_SCEN USART_CR3_SCEN_Msk /*!< SmartCard mode enable */

+ }$ T0 q% e" S4 h7 h! H! v- ~ - #define USART_CR3_DMAR_Pos (6U)

" q7 u, q. p8 h R - #define USART_CR3_DMAR_Msk (0x1UL << USART_CR3_DMAR_Pos) /*!< 0x00000040 */2 c* u- k& G. C) a# x& q: S( J

- #define USART_CR3_DMAR USART_CR3_DMAR_Msk /*!< DMA Enable Receiver */

% b+ J, T, b" T6 _/ K! w3 N% a$ c( V - #define USART_CR3_DMAT_Pos (7U)9 [3 H5 s) P' }5 Q& G: F

- #define USART_CR3_DMAT_Msk (0x1UL << USART_CR3_DMAT_Pos) /*!< 0x00000080 */9 `- Y0 K) ^3 G" i

- #define USART_CR3_DMAT USART_CR3_DMAT_Msk /*!< DMA Enable Transmitter */

+ w7 T$ `. w5 I% N7 F - #define USART_CR3_RTSE_Pos (8U)

+ |. l8 v+ O ]- {: E4 T6 z( n9 m - #define USART_CR3_RTSE_Msk (0x1UL << USART_CR3_RTSE_Pos) /*!< 0x00000100 */( A* L) Z" g% A7 G- \- o. Q

- #define USART_CR3_RTSE USART_CR3_RTSE_Msk /*!< RTS Enable */( d* M* ?, [- S- l. i

- #define USART_CR3_CTSE_Pos (9U)# W- q+ v' S' I" ]/ P: e

- #define USART_CR3_CTSE_Msk (0x1UL << USART_CR3_CTSE_Pos) /*!< 0x00000200 */! O: V/ C& A" f' b

- #define USART_CR3_CTSE USART_CR3_CTSE_Msk /*!< CTS Enable */3 y. q s6 }5 H

- #define USART_CR3_CTSIE_Pos (10U) s l: ^6 b8 }% z4 c* P

- #define USART_CR3_CTSIE_Msk (0x1UL << USART_CR3_CTSIE_Pos) /*!< 0x00000400 */. k& f! u3 P& `8 J

- #define USART_CR3_CTSIE USART_CR3_CTSIE_Msk /*!< CTS Interrupt Enable */ e, J) Q. j+ L) I+ g

- #define USART_CR3_ONEBIT_Pos (11U)( U9 O5 i# A6 {" w

- #define USART_CR3_ONEBIT_Msk (0x1UL << USART_CR3_ONEBIT_Pos) /*!< 0x00000800 */5 J( X" J" M B+ P& C5 O9 |

- #define USART_CR3_ONEBIT USART_CR3_ONEBIT_Msk /*!< One sample bit method enable */( H' O0 K" Y0 c' A9 Z( j

- #define USART_CR3_OVRDIS_Pos (12U), B/ x. A+ x. a W9 l9 }

- #define USART_CR3_OVRDIS_Msk (0x1UL << USART_CR3_OVRDIS_Pos) /*!< 0x00001000 */) M. G$ Q+ t8 k

- #define USART_CR3_OVRDIS USART_CR3_OVRDIS_Msk /*!< Overrun Disable */. ^/ Y& I) s( R+ k

- #define USART_CR3_DDRE_Pos (13U)0 B& `1 M& g# J4 G& l( `" E

- #define USART_CR3_DDRE_Msk (0x1UL << USART_CR3_DDRE_Pos) /*!< 0x00002000 */

% x' t3 f! ?+ e - #define USART_CR3_DDRE USART_CR3_DDRE_Msk /*!< DMA Disable on Reception Error */

8 r. H' x7 }; A5 q( q l - #define USART_CR3_DEM_Pos (14U)

' k7 O N0 s) _, d8 J$ H2 G - #define USART_CR3_DEM_Msk (0x1UL << USART_CR3_DEM_Pos) /*!< 0x00004000 */

- Z7 L& y6 `, o u6 r& c - #define USART_CR3_DEM USART_CR3_DEM_Msk /*!< Driver Enable Mode */+ M# y' N7 X+ o* K- b* F0 F

- #define USART_CR3_DEP_Pos (15U)! N [# U/ a6 R% w; y! Q

- #define USART_CR3_DEP_Msk (0x1UL << USART_CR3_DEP_Pos) /*!< 0x00008000 */

3 K/ S" {1 }6 A3 C - #define USART_CR3_DEP USART_CR3_DEP_Msk /*!< Driver Enable Polarity Selection */

" z2 v- [% K2 R1 _! ~: y - #define USART_CR3_SCARCNT_Pos (17U): B/ `6 @0 i7 z0 z) j1 V

- #define USART_CR3_SCARCNT_Msk (0x7UL << USART_CR3_SCARCNT_Pos) /*!< 0x000E0000 */' c2 [& t5 u0 q

- #define USART_CR3_SCARCNT USART_CR3_SCARCNT_Msk /*!< SCARCNT[2:0] bits (SmartCard Auto-Retry Count) */

/ K6 L: a( q! T; w3 {0 ] - #define USART_CR3_SCARCNT_0 (0x1UL << USART_CR3_SCARCNT_Pos) /*!< 0x00020000 */

1 l3 W) N+ W+ p" h - #define USART_CR3_SCARCNT_1 (0x2UL << USART_CR3_SCARCNT_Pos) /*!< 0x00040000 */

/ W/ h( S) a9 M$ o$ J+ L$ Q - #define USART_CR3_SCARCNT_2 (0x4UL << USART_CR3_SCARCNT_Pos) /*!< 0x00080000 */

$ u( ^# K# ^! l% O* ?7 P* y" d - #define USART_CR3_WUS_Pos (20U); H4 q, D) Z+ Z

- #define USART_CR3_WUS_Msk (0x3UL << USART_CR3_WUS_Pos) /*!< 0x00300000 */

% d) G3 M {. b - #define USART_CR3_WUS USART_CR3_WUS_Msk /*!< WUS[1:0] bits (Wake UP Interrupt Flag Selection) */

& P4 {" J: \% ]5 ] - #define USART_CR3_WUS_0 (0x1UL << USART_CR3_WUS_Pos) /*!< 0x00100000 */

7 t6 b7 |; u( B+ y5 X1 O - #define USART_CR3_WUS_1 (0x2UL << USART_CR3_WUS_Pos) /*!< 0x00200000 */

/ C/ I; o5 ~& |3 a - #define USART_CR3_WUFIE_Pos (22U)3 r" x) n+ [6 h" q5 ~

- #define USART_CR3_WUFIE_Msk (0x1UL << USART_CR3_WUFIE_Pos) /*!< 0x00400000 */

' h' M C' K. M - #define USART_CR3_WUFIE USART_CR3_WUFIE_Msk /*!< Wake Up Interrupt Enable */7 i! E% {4 e& v# N0 j

- #define USART_CR3_UCESM_Pos (23U)" U! a+ F6 Z* g5 H4 s" k7 z

- #define USART_CR3_UCESM_Msk (0x1UL << USART_CR3_UCESM_Pos) /*!< 0x02000000 */

, N) P, d) Z! q2 Z - #define USART_CR3_UCESM USART_CR3_UCESM_Msk /*!< USART Clock enable in Stop mode */

1 _, K3 L% l& p. j) f - #define USART_CR3_TCBGTIE_Pos (24U)

6 u! g( ?6 p; @' e9 j$ m q% U C - #define USART_CR3_TCBGTIE_Msk (0x1UL << USART_CR3_TCBGTIE_Pos) /*!< 0x01000000 */6 s8 o5 J7 U" l) b+ K2 l2 g

- #define USART_CR3_TCBGTIE USART_CR3_TCBGTIE_Msk /*!< Transmission Complete Before Guard Time Interrupt Enable */

0 l Q* v F; e4 Z3 E4 d 这里只说CR1、CR2、CR3主要的标识位。- J, _: U7 z& M

; i. P$ `9 m q; v% i! ?9 f

4 ~; }8 g; @6 `

4 ~; }8 g; @6 `

# o' [6 l* T4 I: @ 【1】在CR1中:

! w5 s X+ z, J1 _$ x# b+ c% p$ d, q! `# m( F; z

1)UE位(0位)定义UART使能;

+ ?; ~/ @5 P6 o& Q, C1 O% I1 k! Z3 o/ D0 U

2)UESM位(1位)定义使能是否开启STOP模式;- {) N3 i+ p; B6 L9 i+ i

' N% h, R; l1 L; Y" B. j, m2 C6 ]+ t N

3)RE位(2位)定义数据接收使能;

' r( |6 X; c: B& M7 J% p) A

2 L- A& |! V) o1 ?) |+ V 4)TE位(3位)定义数据发送使能;& R4 |5 y ~1 E1 _: S9 t: c4 ^" S

) r- A h4 C0 }8 x+ a# ^$ Y L$ I9 H, |

5)M位(10位)定义数据字长度,0是一个起始位、8个数据位、n个停止位,1则表示一个起始位、9个数据位、n个停止位;* g! C# a0 I! I0 \

0 y3 H k8 @; b _

6)PCE位(12位)定义是否开启硬件检验控制使能奇偶校验,0是禁止校验控制,1是开启校验控制。

( @* \% n6 E( P, q- s! ?7 M

/ ~4 F& e. F& s9 |6 u, y& ~ 【2】在CR2中,STOP位(12、13位)标注停止位,就是前面所述的:

; C" j9 W) e1 D

2 ]2 L5 w' R4 e# `3 T5 p) a 00-1个停止位:停止位位数的默认值。

$ }) l5 h% D, S. Y

, g6 Y' i# `/ a+ A 01-0.5个停止位:在智能卡模式下接收数据时使用。

9 a8 c& Q3 L, K( c7 }

3 [" F" h7 O; Q( R+ | 10-2个停止位:可用于常规USART模式、单线模式以及调制解调器模式。, N" P+ u! ^1 C1 o# K

5 R/ z$ `/ V! X/ C. O& [ 11-1.5个停止位:在智能卡模式下发送和接收数据时使用。4 n3 L a* V$ c3 F+ \6 L

! G: ~( j! ]- ]( n9 ] 【3】在CR3中,DMAR位(6bit)使能DMA接收,而DMAT位(7位)使能DMA发送。

) ?) U3 ~ C/ z$ D( Y0 q

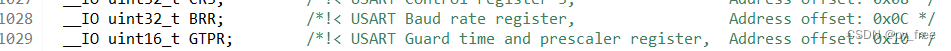

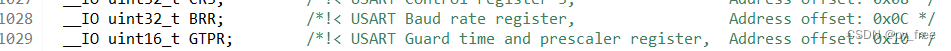

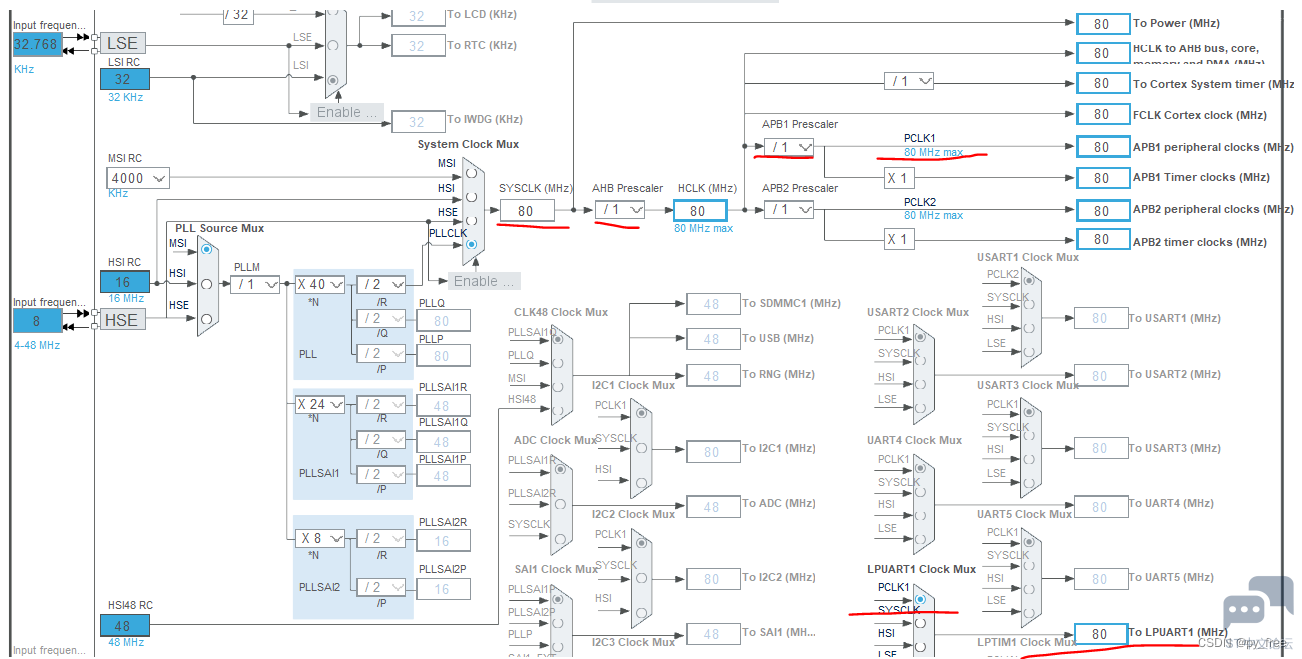

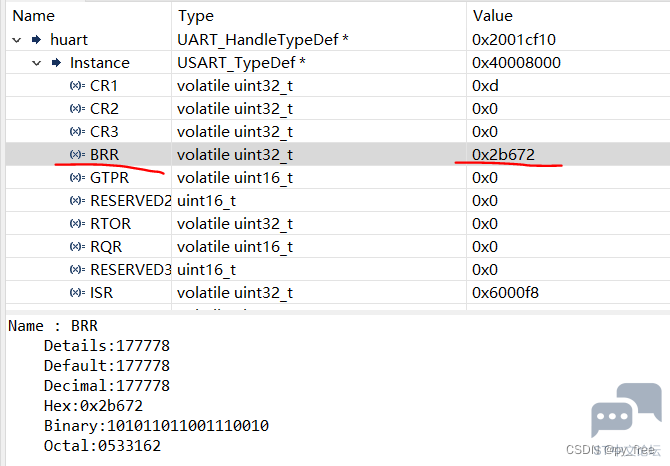

" t" [" k+ _5 ^1 k, | 2.3 波特率寄存器BRR& s, A, _" T8 {' ^1 K) R l

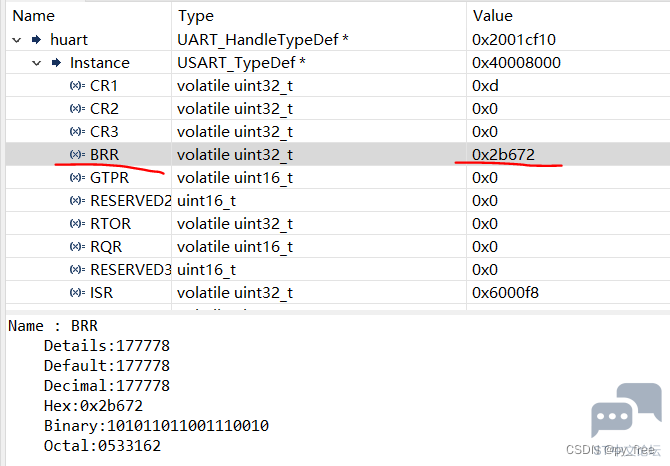

波特率寄存器BRR若是一个16位的存储空间用于存放分频除法因子UARTDIV,低4位存储小数部分,高12位存储整数部分。假设UART的时钟经过多次分频,总分频数是div,最终输出频率是fpclk,则波特率br=fpclk/(div*UARTDIV)。这个UARTDIV在cubeMX是不用做配置的,而是在配置了波特率、时钟分频及时钟频率后,生成输出代码时,在UART初始化时,自动根据波特率和时钟参数计算出UARTDIV写入到BRR寄存器。

( m7 w; }: r4 P) Y' Z. M. d+ n0 O( q+ I; Q' r7 |

如果BRR寄存器是32bit的存储空间,一般就是低8位存储小数部分,高24位存储整数部分。现版本的HLA库里面,目前采用的就是32bit的存储空间,即uint32_t UART_BRR。

3 \- m. M, [0 D% s8 E! S7 c% e& A- S4 p

" v7 G3 V/ |; `6 |5 v* f4 v7 Y/ s, w: e0 W( Q4 j

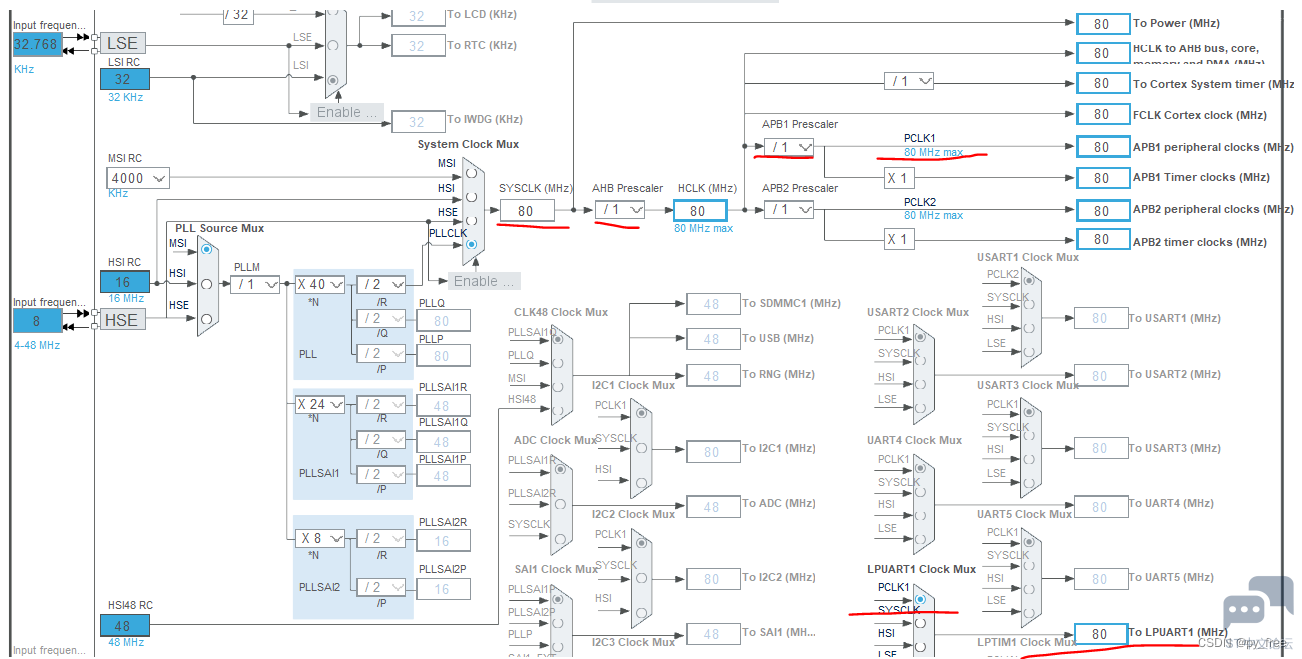

现例如fpclk=80MHz,波特率br=115200,分频div=1(PCLK1到最终频率输出涉过程涉及的分频器),如下图所示' b |* J# f6 a& K2 e: j/ O

* x& I; V; d2 ^5 z' i+ w) E

7 s% W3 q8 p9 ? a$ ^

7 s% W3 q8 p9 ? a$ ^

( s( u3 o& }4 w( b+ N: r f

则UARTDIV = 80000000÷(115200*1)=694.44。整数部分直接写入高位部分,694=0X2B6,而小数部分是8个数据位存储的,相当于从整数借1(8bit,最大值是二进制11111111=0XFF)划分为256份,那么小数部分乘256再转16进制就是要填写的小数部分。0.444*256=113.64≈114=0X72。最终合并整数部分和小数部分,向BRR写入数据是0X2B672。

$ g' d) S( J6 w+ V9 R9 D1 e; Q+ h- i8 Z% D! T8 S

然后按上述配置,在测试调试中,查看串口BRR寄存器数值,也是0X2B672。/ {2 h& |4 V! B2 i7 c9 p/ k. O" v

2 y$ u0 j/ k# U# o+ Q- z

% K' {( z# P+ v6 Y( u* A Z

8 F: J3 r( R: {1 j6 X/ s; N, U. c 2.4 中断寄存器IR

+ n6 ^) }( N! }/ j. u' ]5 i# D" v' H 如果开启了中断功能,还会涉及到中断寄存器IR使用,在控制寄存器CR、状态寄存器SR都会与其产生交互。中断寄存器IR又包含中断状态寄存器ISR、中断清除寄存器ICR。收发控制器会依据控制寄存器(CR1、CR2、CR3)配置的信息,诸如发送完成中断TCIE、发送清零中断TXEIE等中断事件与中断寄存器打交道。

) y; K" k! g4 f$ s3 A) R! k" G6 W: b( m' z5 @

下面列出CR寄存器设计中断使能(Interrupt Enable)的配置:TXEIE(发送数据寄存器为空)、TCIE(发送完成)、IDLEIE(空闲线路)、RXNEIE(读取数据已准备或过载)、PEIE(奇偶校验错误)、CMIE(字符匹配)、RTOIE(超时)、EOBIE(块接收结束)、LBDIE(断路)、CTSIE(CTS标记)、WUFIE(唤醒)、EIE(各异常)等。3 G0 y n+ j' C |+ }/ r

5 ^1 {2 A2 N! k

2.5 其他寄存器

1 h0 N0 P6 r% `! C+ J UART串口通信还包含预分频寄存器、接收超时寄存器、请求寄存器等,在HLA库中体现为约定数据位宽度大小的存储区域。 G' T# b! r( P& C. [- ^

- /**; R* I% u# Q4 o' I |% e, H' Y

- * @brief Universal Synchronous Asynchronous Receiver Transmitter

I# R" j' H: F( E - */

( d8 u' g& M: c( ]! K$ d* k3 p( `& M -

9 B0 ` `: w6 }4 ]8 r! x - typedef struct% ?, J8 z) F0 B, \+ p4 `

- {

" {9 h* ?! m# L! I - __IO uint32_t CR1; /*!< USART Control register 1, Address offset: 0x00 */

, ^" i$ Q. n2 B - __IO uint32_t CR2; /*!< USART Control register 2, Address offset: 0x04 */! E3 j5 ?3 D+ N. @3 B! U; E! f3 X

- __IO uint32_t CR3; /*!< USART Control register 3, Address offset: 0x08 */. K5 w. E! ?6 \' z+ i

- __IO uint32_t BRR; /*!< USART Baud rate register, Address offset: 0x0C */* u4 I9 ~! t# e7 h0 {2 w

- __IO uint16_t GTPR; /*!< USART Guard time and prescaler register, Address offset: 0x10 */

5 ^% _9 h" S$ u# @% P - uint16_t RESERVED2; /*!< Reserved, 0x12 */ b( J- z: E! `! `. J7 F

- __IO uint32_t RTOR; /*!< USART Receiver Time Out register, Address offset: 0x14 *// p; f& K: U& _

- __IO uint16_t RQR; /*!< USART Request register, Address offset: 0x18 */) B. h" b/ X& H0 T, m: s

- uint16_t RESERVED3; /*!< Reserved, 0x1A */1 H/ ]3 p/ V- T" b

- __IO uint32_t ISR; /*!< USART Interrupt and status register, Address offset: 0x1C */9 y- v# ~( u) A7 K! x4 f+ Q

- __IO uint32_t ICR; /*!< USART Interrupt flag Clear register, Address offset: 0x20 */

. ]" o: c0 z, S7 `* ?7 ?* d& j - __IO uint16_t RDR; /*!< USART Receive Data register, Address offset: 0x24 */

# I2 M& Q, l2 O# l - uint16_t RESERVED4; /*!< Reserved, 0x26 */% r8 P4 A0 S' j/ K# V# k8 ~9 H; _

- __IO uint16_t TDR; /*!< USART Transmit Data register, Address offset: 0x28 */

! o7 l2 }$ ], m0 | - uint16_t RESERVED5; /*!< Reserved, 0x2A */! d" t6 Q. E4 ~5 o9 F8 A

- } USART_TypeDef;

3 q1 Q# ~* j8 k* T三、UART配置及HAL实现

9 P$ `4 V) ]) Y8 ^* E; a" P g 3.1 UART配置梳理: M+ W6 T8 @" K B$ g$ k. |, x; J8 I

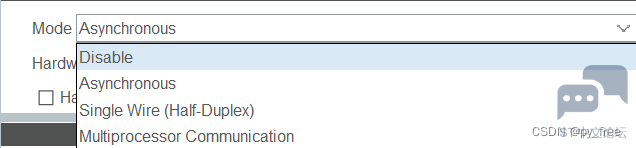

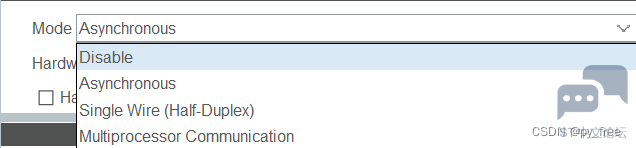

在cubeMX中配置UART主要就是在模式下拉框中开启相关模式,进行串行通信一般就是选择异步模式,其他模式针对特定场景使用。9 l" h5 O" j$ e( L1 F) A

`9 ~( x F7 _) t

/ b3 l: u( B. r0 g& I+ H5 k4 L& Z+ a6 {/ S1 |) p/ w8 A

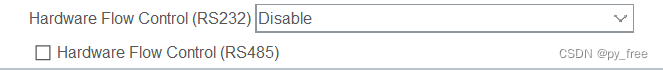

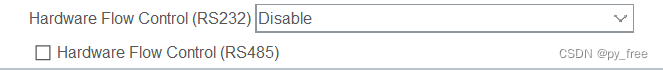

可以根据需要开启RS232流控制支出或RS485流控制支持,主要就是针对STM32板与RS232或RS485做连接并配合外设设备开启硬件流控时使用。: a- Q2 w2 K! G, g6 H

$ t% m2 W! Q! Y: N8 ~& X# s# o) [4 o

; V2 N/ d) W/ h2 M1 ?, L! \" P; l+ i9 k y' h" a

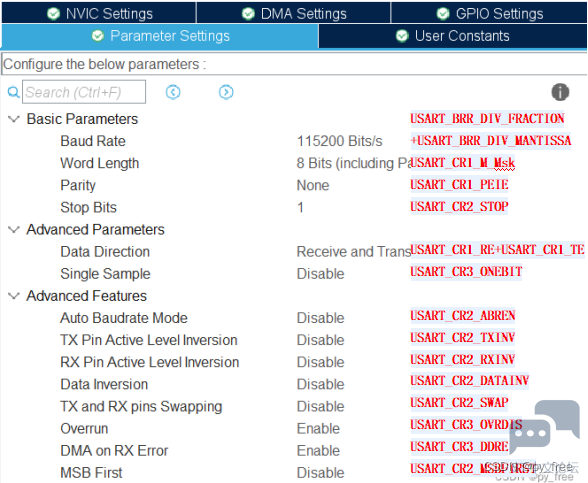

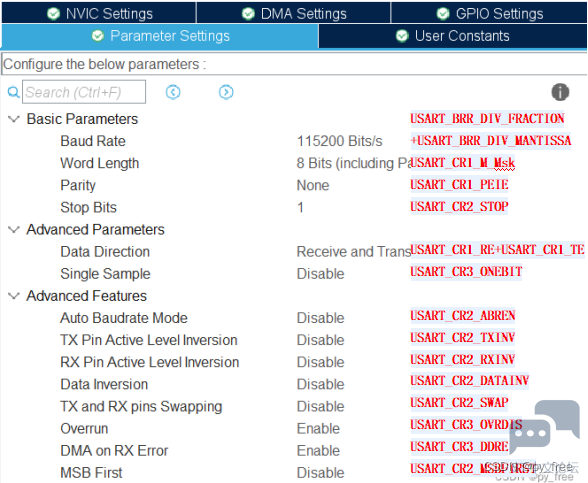

针对UART的参数设置,主要就是设置串行通信的波特率、数据长度、校验位、停止位。如前面叙述的波特率和时钟频率计算出除法因子存储在BRR寄存器内。校验位、停止位的配置最终体现在控制寄存器CR中,数据长度同样也最终体现到控制寄存器CR中USART_CR1_M/M0。

3 @) B( G; _7 A6 `+ \9 B& d' U6 f, j) J4 ]# m

" L% U d: @$ Y" J* p; g4 ^. Z) g1 |* O7 j! {) v# {

& |8 m, R8 [6 s" w' W- G: Q 3.2 UART初始化梳理% ]) X3 j* o& J8 c6 O! |

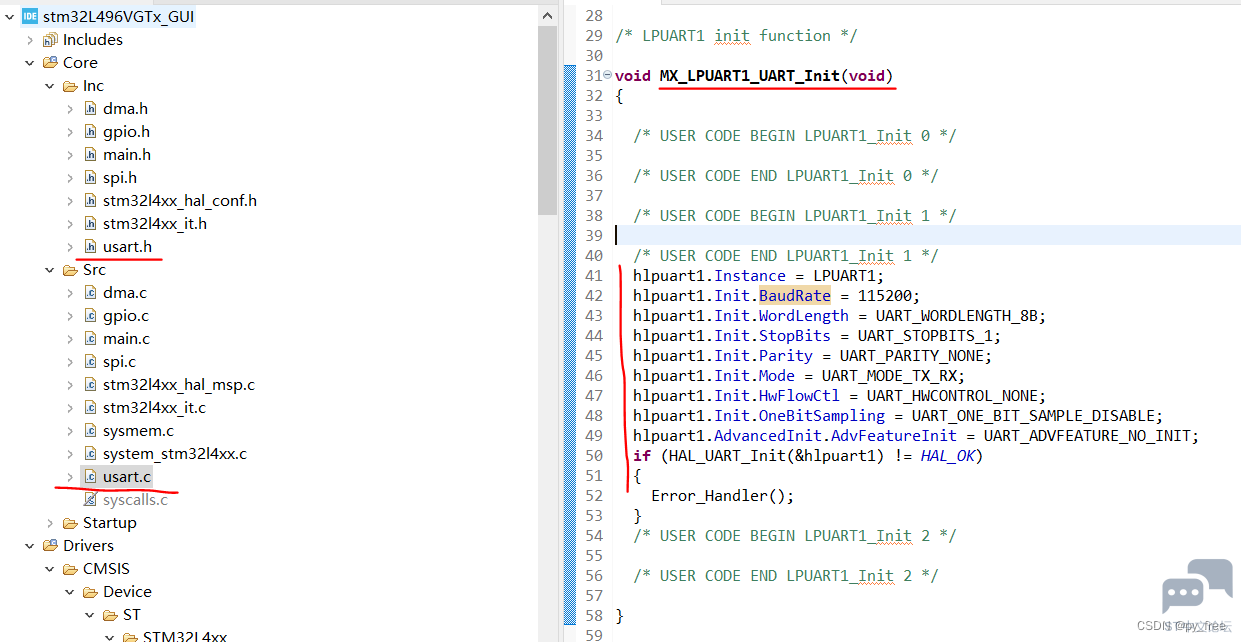

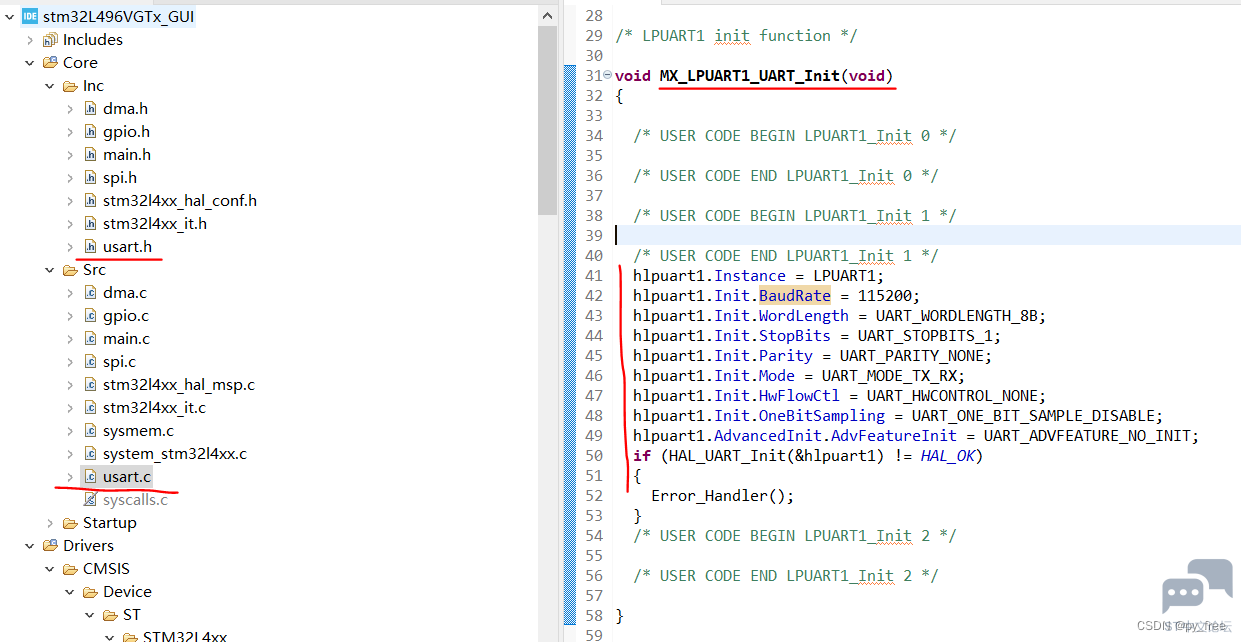

cubeMX生成输出代码时,如果配置了给外设生成独立的.h/.c源文件时,串口外设的源码头文件及源文件分别在Core的Inc和Src目录下,输出代码usart.c会为每个独立的串口外设生成初始化函数,将在cubeMX配置的串口参数写入到串口参数变量中,并调用HLA串口初始化函数HAL_UART_Init。如果不配置给外设生成独立的.h/.c源文件时,HAL_UART_Init一般生成在main.c源文件中。

% t! W6 V6 U! c1 C( e

1 ?# h# b! h, ] 注:HLA有4个UART相关初始化函数,HAL_UART_Init(), HAL_HalfDuplex_Init(), HAL_LIN_Init()and HAL_MultiProcessor_Init()。分别对应UART asynchronous、UART Half duplex、UART LIN mode、 UART multiprocessor 模式,就是前面模式下拉框配置的模式。+ b _& ~4 H) M' c4 j

/ s4 O/ a" ` q+ D& `3 D( s% V5 z

# n# [# t. B7 T- s# x

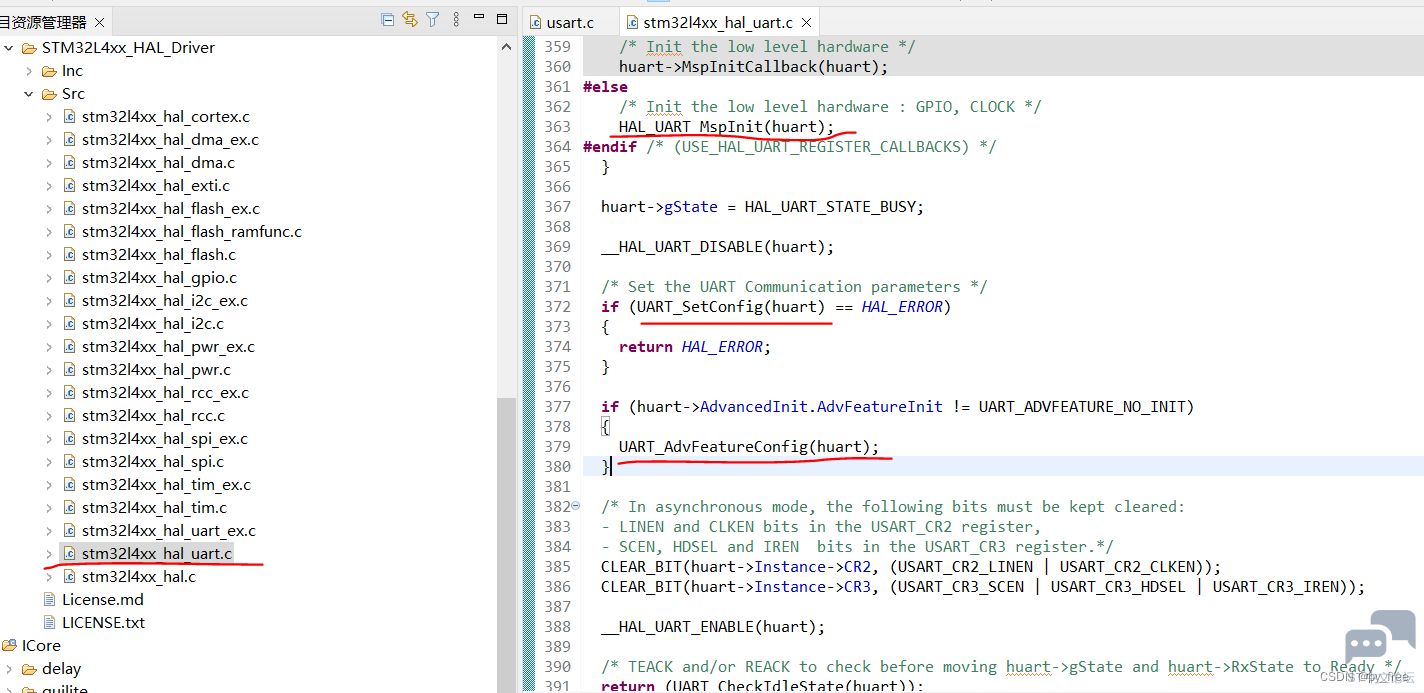

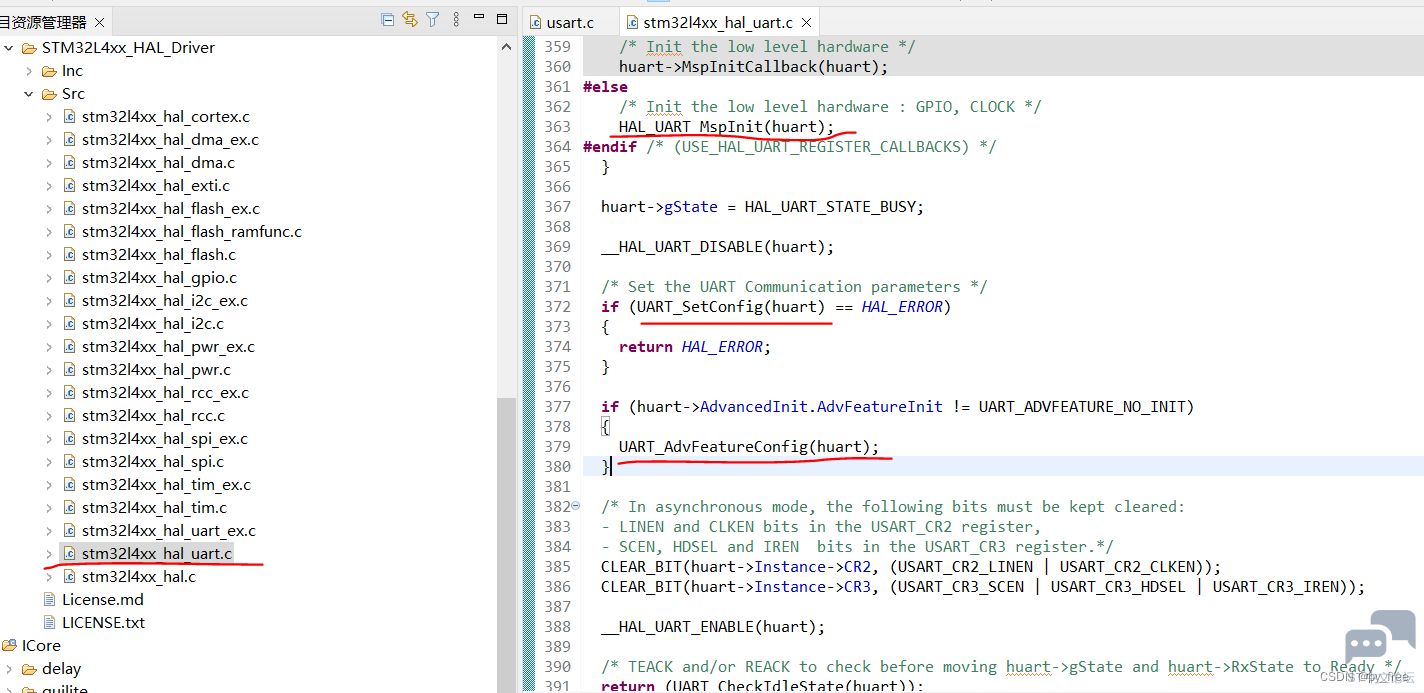

- M4 {! O L. i' ?+ C% v4 i8 j 在HAL_UART_Init函数中主要实现三个主要功能,底层硬件初始化,配置一般参数、配置高级参数。底层硬件初始化就是调用HAL_UART_MspInit实现引脚配置、时钟设置、中断等相关功能,HAL_UART_MspInit在HLA库中默认是弱函数,CubeMX会根据界面配置生成真正HAL_UART_MspInit函数覆盖原来的函数,同样放置在usart.c源码文件中。( q S$ I) h, `- H9 h2 O

" b! J, g6 g' \( I$ s3 I: ~$ D

( ^* D3 Q; G( m

( ^* D3 Q; G( m

: W8 a3 W6 O" o

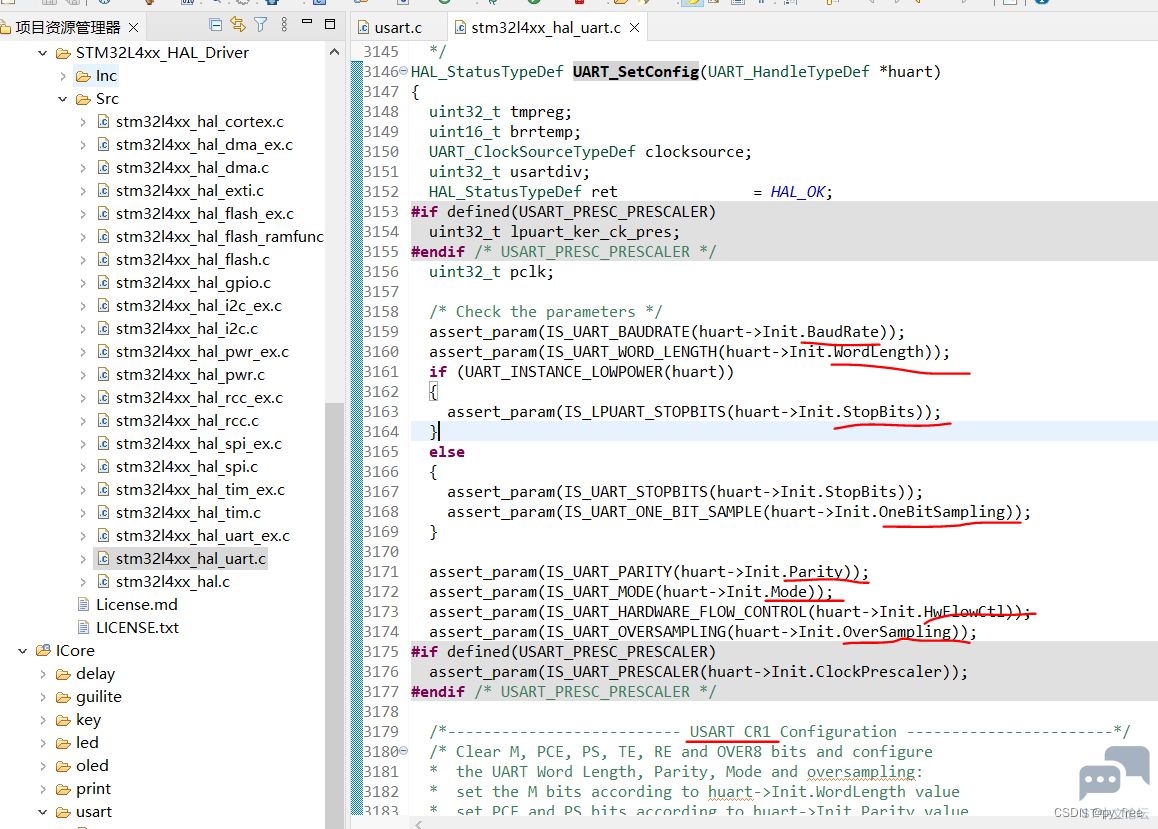

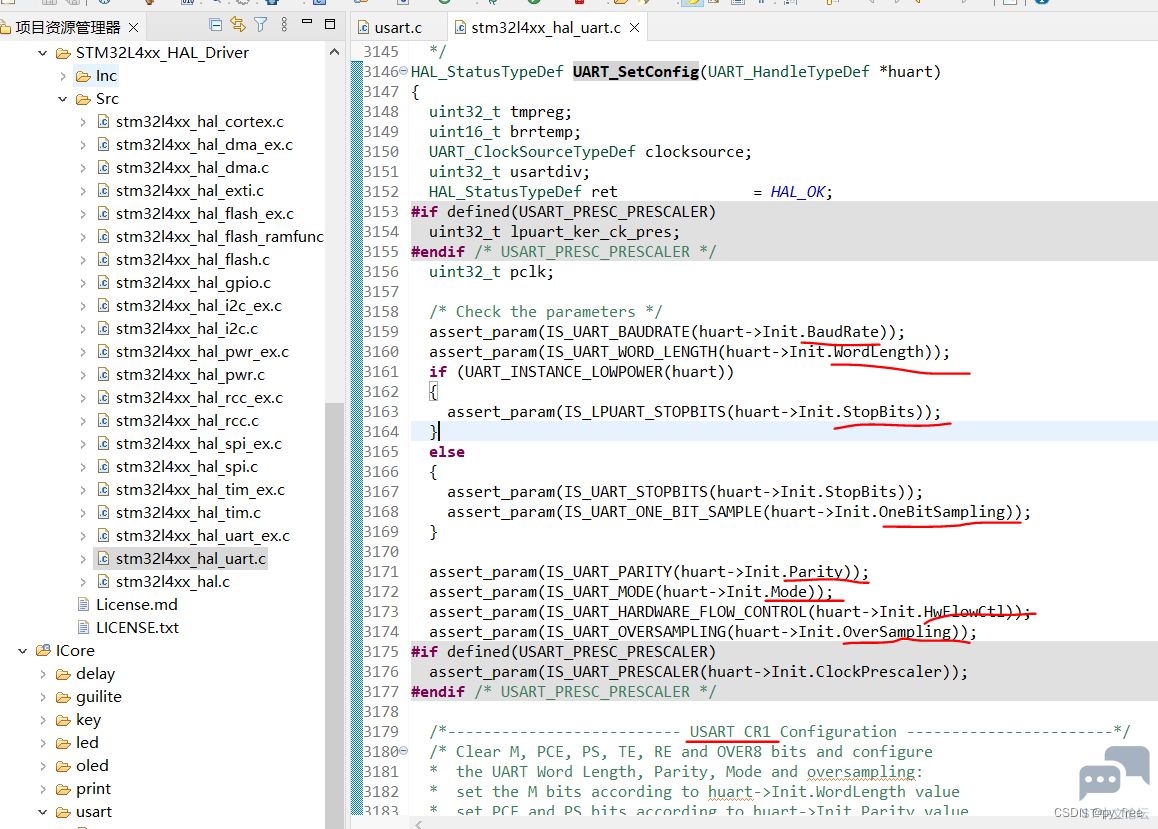

配置一般参数UART_SetConfig、配置高级参数UART_AdvFeatureConfig则会将前面已经设置到串口参数里的变量进一步写入到各个寄存器中,并进行合理校验。其实HLA串口通信最终还是通过操作寄存器实现的,只是HLA库帮助开发者屏蔽调对串口相关寄存器的操作,只要调用上层HLA-API就可以。UART_SetConfig实现了对波特率、校验位、停止位以及其他参数等设置,该函数很大,更多细节请查看HLA源码阅读。

/ ]4 h% V/ V. q; ?# \3 f. T6 ?- R0 K0 J4 E# y7 e' p

6 Q! e+ Z$ E1 i- L1 p m8 q

6 Q! e+ Z$ E1 i- L1 p m8 q

$ l# \: x X& U; t" M8 v0 J8 \ UART_AdvFeatureConfig实现了对串口高级特征设置,在CubeMX上配置的高级特征都能在该函数得到体现。

+ Z/ ?3 Y8 X" L3 M- q' t

+ i. H7 E1 e: x; ~9 I2 y9 J: z

3 v( \& `0 O p' d1 ^7 H" u

3 v( \& `0 O p' d1 ^7 H" u

1 v& Q7 E' Z, [ D 3.3 UART收发数据源码梳理& G5 d. N; b% ~& A$ ] v) U0 y

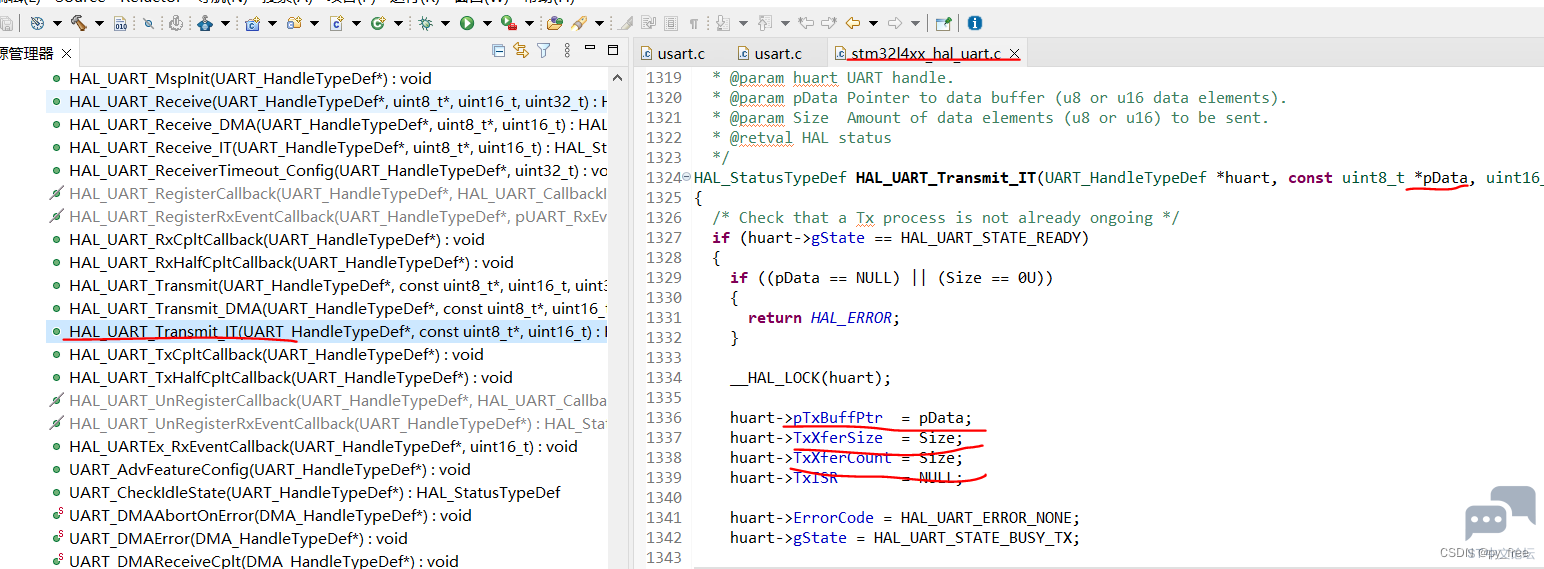

UART的HLA库的发送数据和接收数据的API分别是HAL_UART_Transmit*和HAL_UART_Receive*,以HAL_UART_Transmit_IT为例,先将需要发送的数据写入到串口的缓存中,就是相当于前面所述的从MCU或系统总线到发送数据存BUFF区域。: k* D! j' o; |+ r7 x1 S

1 _( J* u' p* |

- J0 n0 k/ i F, q+ b* c+ n

" Z3 X3 i- [+ g# @1 B+ D 然后通过判定数据长度参数来调用不同注册函数,将上面存储在串口缓存区域的数据转移到发送数据寄存器TDR中。* o5 U6 H0 J& `

0 ?& y1 c; X, J0 @- O

9 v/ r& c6 ]! \# x% P& ~) P/ B: ?5 c( O* L" v7 [# q6 n, U( M3 m

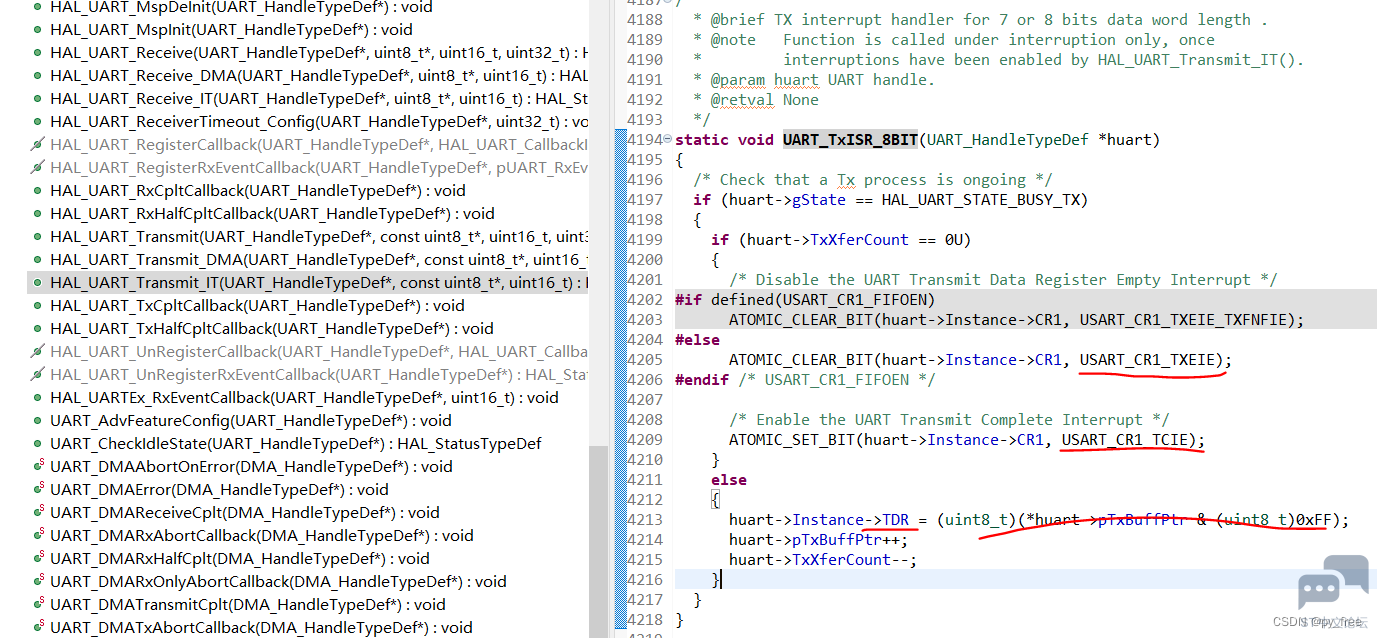

数据从串口缓存区域到发送寄存器TDR,并会在数据转移完成后关闭TXEIE使能(发送数据寄存器为空数据位)和开启TCIE使能(发送完成中断数据位):

, I+ v; i4 ?: d) C" ?! m( {: r+ I8 u5 B! k3 l# t* }5 X5 ~

/ O8 L( I+ f) V: t& P8 E' p6 Q: _

2 M/ `% @) @7 F% L+ V; Q9 P* } 硬件层面上,串口的收发控制器会根据寄存器各个数据位数值变更作出数据发送、数据接收以及控制寄存器CR上各个数据位设值动作,实现从软数据到硬电平的转换及发送。; _0 y- ~% d: R& L2 R9 o

( m/ [# }$ F0 X5 M5 ^

而在数据接收方面,类似发送机制,首选调用HAL_UART_Receive*函数开启,类似注册及等待回调。程序主要是判定到CR寄存器上接收数据相关的数据位变更,从而调用接收数据的回调函数开启接收,实现由接收数据寄存器RDR到串口缓冲区域,再进而触发用户实现串口回调函数调用及存储数据到用户定义缓存的过程。) g2 `& g8 P; L* I

————————————————' n% |- ~. s4 l

版权声明:py_free-物联智能 P; b) O6 b! P* v$ L- ~2 N# ^

如有侵权请联系删除3 r& n, _6 `/ R/ R8 _% t2 S1 J+ c, x

# f( y1 L0 p7 G! B, r* ^" y3 r$ |8 n6 d: j

5 S* ?" D' I7 v+ _

|

微信公众号

微信公众号

手机版

手机版