一、硬件平台

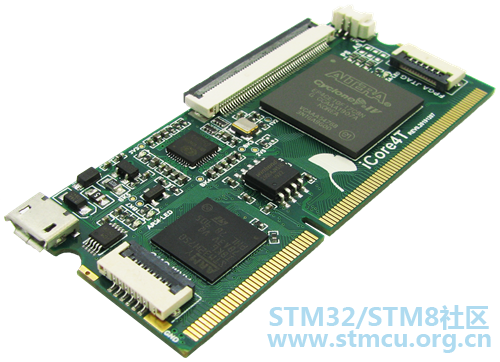

二、实验简介 本实验基于ARM+FPGA超mini款iCore4T双核心板,一步一步带你利用STM32CubeMx工具完成对通用定时器TIM3的基本配置,实现500ms的定时功能。 通过编写通用定时器中断回调函数的内容以实现对板载LED的定时控制 三、资料下载(实验源码+详细文档操作说明) 1、源代码  5_timer.zip

(912.46 KB, 下载次数: 10)

5_timer.zip

(912.46 KB, 下载次数: 10)

|

STM32H7 SPI Underrun 特性实战指南:配置、行为与传输可靠性优化

【STM32H750-DK 车辆仪表】6.模拟温度和胎压监测

【STM32H750-DK 车辆仪表】5.油表

【STM32H750-DK 车辆仪表】4.仪表时钟

【STM32H750-DK 车辆仪表】3.车速控制UI

【STM32H750-DK 车辆仪表】2.与板卡交互

【STM32H750-DK 车辆仪表】1.灯光控制UI

无刷直流电机控制应用+基于STM8S系列单片机---电子书

STM32应用过程中与电源相关的案例分享

MCSDK FOC应用详解

微信公众号

微信公众号

手机版

手机版

还有,建议取消 FPGA 上的 Flash 颗粒,改成通过 SPI 或 FMC 来连接 FPGA 和 STM32,同时相应配置 FPGA 的启动模式为 SPI 从设备或并行接口。这样的话在实际应用中,FPGA 完全依赖 STM32 启动,两者的软件可以同时更新;同时 FPGA 启动接口兼做与 STM32 之间的高速通信接口,节省 FPGA 管脚。至于说 SPI 闪存颗粒,可以完全取消,也可以改接 STM32 的 QSPI 接口。另外,FPGA 有源晶振也可以取消,改成由 STM32 通过 MCO 向 FPGA 输出时钟。其三,FPGA 的 nPROG 和 STM32 的 nRESET 可以接在一起,使得两者可以一起复位。这样做的话,FPGA 独立支持电路几乎完全取消,彻底作为 STM32 的外设来使用。

我有设计过一款 AGM FPGA + STM32L4 的开发板,就是这样的设计结构:FPGA 配置成 SPI 启动,接在 STM32 的 SPI 管脚上;STM32 同时负责通过 MCO 给 FPGA 提供时钟;两者的复位信号也是接在一起;另外在 STM32 挂了一片 QSPI 闪存来存放 FPGA 配置数据。

FLASH颗粒在iCore4T中已经选配了,默认不焊接,只留出了位置对一些只开发FPGA的用户提供方便。目前STM32MP1+FPGA已经在原理图阶段了,ARM+FPGA计划QSPI连接。另外其他的两点可以考虑哦

QSPI 的话要注意兼容性问题,而且由于 STM32 QSPI 的特性 FPGA 端开发可能会有困难。我觉得 FMC 会更合适一点。

QSPI跑个几十MB的速度已经完全够用了,比起来FMC节省了不少IO资源

FMC 在 FPGA 一侧要方便的多: