.png) STMCU小助手

发布时间:2022-2-23 19:01

STMCU小助手

发布时间:2022-2-23 19:01

|

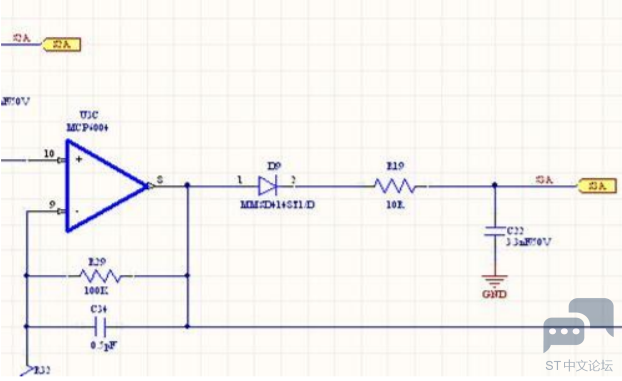

前言 本篇讨论了一个由 ADC 连续模式下采样浮空引脚出现的问题,分析了其原因。 问题: 某用户使用 F0 产品进行设计。在使用 ADC 采样时,发现当工作于连续模式时,即使外部信号为零时,依然采到一个数值,近似 1/2VDD(此处 Vref+和 VDD 接在一起)。0 P7 a' i: m# p6 _- D+ T 相关部分原理图如下。

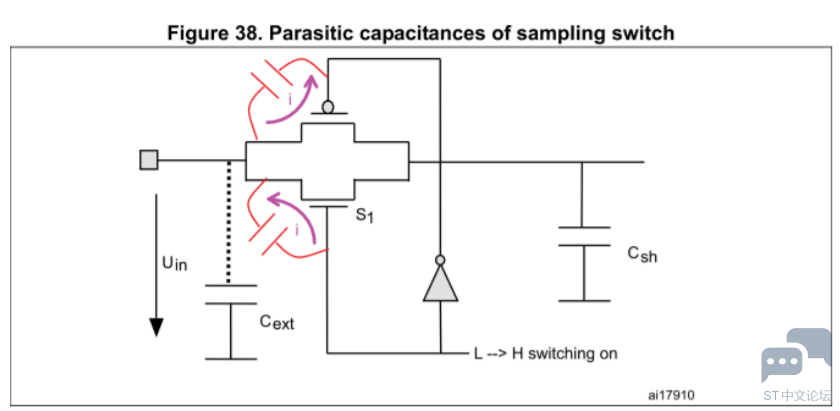

+ c( f) I( [. Q$ C) m$ j1 F 分析: 分析上图,可知当跟随器输出为高时,D9 导通,IO 上处于固定的电平;当跟随器输出为 0 时,由于D9 的存在 IO 口实际处于 Floating 状态。此时,采样此通道上电压似乎应当是一个不确定的值才对。 在应用笔记 AN2834 中,有一个关于 ADC 的图:% O2 k1 t! p1 H0 S 6 Q3 ^9 D% }4 j( D! y' B# G

当处于连续模式时,开关 S1 会始终打开,它的两个内部寄生电容(图中红色部分)会被充电。这两个内部寄生电容的电荷继而会被转移到采样电容 Csh 上,从而使得采样数值并非为 0。此时采样得到的数值是没有意义的,因为并不能反应该引脚上真正的电压,而这个看似存在的电压也没有驱动能力。进一步分析,原理图中的 D9 可以去除。这样,当原先 D9 截止时,将使得该引脚处于浮空状态;而去除后,该引脚将会被拉到低,从而采样得到一个稳定的有意义的值。 |

【2025·STM32峰会】GUI解决方案实训分享2-编译运行TouchGFX咖啡机例程(含桌面仿真)

实战经验 | Keil工程使用NEAI库的异常问题

STM32 ISP IQTune:真正零门槛的免费ISP调整软件

【经验分享】STM32 新建基于STM32F40x 固件库的MDK5 工程

意法半导体MCU双供应链策略,打消中国客户后顾之忧

【经验分享】基于STM32使用HAL库实现USB组合设备CDC+MSC

2024意法半导体工业峰会:赋能智能电源和智能工业,构筑可持续未来

ST推出灵活、面向未来的智能电表通信解决方案,助力能源转型

意法半导体 x Qu-Bit Electronix:推动新一轮的数字声音合成革命

从STM32 MPU产品看嵌入式系统中微处理器的新变化

微信公众号

微信公众号

手机版

手机版