.png) STMCU小助手

发布时间:2023-11-26 15:54

STMCU小助手

发布时间:2023-11-26 15:54

|

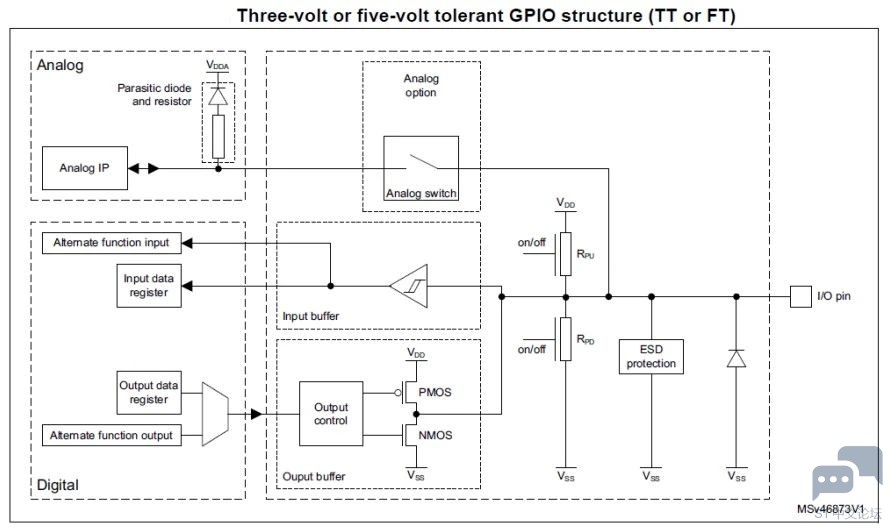

01概述7 @# B, q0 Y# r) X4 V7 } W 在 STM32 系列 MCU 中, 除了一些特殊管脚外,绝大多数管脚都可以分类为 FT (兼容5V 信号)或 TT(兼容 3V3 信号)类型的 IO,由于 MCU 内部设计的不同, TT IO 相比 5V IO 有更多的限制,下面我们将予以说明。 : l$ _& `1 f2 P8 o 02 TT 和 FT IO 的结构和参数区别* I1 H0 z" K# M8 b% u1 Z 下面我们解释 TT 和 FT IO 的不同内部结构以及因此导致的对输入电压和电流的不同限制要求。 - X4 |, \; b# `4 v$ {: I! m1 Z0 s 2.1. TT 和 FT IO 的结构区别( R4 h4 j2 F A# H4 X" @8 m0 K; J 下面的图 1 描述了 TT 和 FT IO 的通用结构:7 R4 S. }# V% ^' V& X* p 5 E$ u# e; a2 }! ?1 K L, D

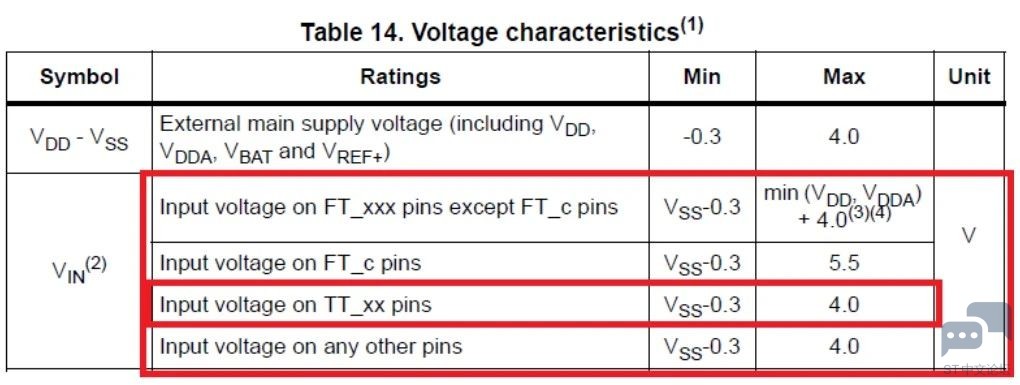

图1.TT/FT IO 的内部结构 TT 和 FT IO 的内部结构在 IO 端口的保护电路 (IO 到 VSS 二极管以及 ESD 保护单元),输出 BUFFER,数字控制单元以及模拟单元都是相同的。 区别在于, 对于 FT IO 来说,从 IO 输入到模拟单元之间存在一个模拟开关,只有在软件控制相关寄存器后这个开关才会闭合. 而对 TT IO 来说, 这一模拟开关是不存在的,IO 管脚与模拟单元直接相连。 3 `7 J6 `% d+ S2 ^* x, n 2.2. 结构不同导致对电平和电流的不同要求 从图 1 结构图中可以看到, 在 IO 内部的模拟单元中存在一个输入信号到 VDDA 寄生二极管和相串联的电阻,该二极管是寄生的,因此其电流能力是无法保证的,不但不能用做模拟输入信号的钳位二极管,而且还要避免任何从输入信号到 VDDA 的注入电流的产生, 否则可能导致内部相关电路的损坏。 * a3 c4 S0 ]8 ?7 s/ n" W9 ` 因此对于 FT IO 的数字输入信号来说, 由于模拟开关被断开, 输入的信号即使高于VDDA 也不会导致模拟单元中寄生二极管电流的产生,在 VDD+4V 的范围内, IO 是安全的。 1 `4 |2 q/ U& E" U+ [ 如果 FT IO 被配置为模拟输入,模拟开关闭合, 那么它就不再是兼容 5V 的 IO 了,输入信号的幅度必须小于 VDDA+0.3V。 ; t6 I* u/ x" w' \6 b 对于 TT IO 来说,由于不存在到模拟单元的模拟开关,模拟单元的寄生二极管和 IO 口是直接相连的,因此,在任何时候都必须保证加到 TT IO 端口的信号电平小于VDDA+0.3V。 % r1 a# H* N& ]8 H- r, U 另外需要补充的是,如果 IO 输入信号可能存在负电平,尽管 TT 和 FT 类型的 IO 都在端口处设计有到 VSS 的二极管,这一二极管提供了一定的钳位保护能力,但是其通过电流能力限制在 5mA 以下。因此,外部钳位二极管通常仍然是必须的,如果不能通过外部钳位二极管将输出负电平信号限制在大于 -0.3V, 那么就需要串联限流电阻将流经二极管的负注入电流限制在 5mA 以下。 - T& g1 P5 P5 u* S) Q 2.3. STM32 datasheet 中相关参数说明) f7 H% D H$ o9 q8 V+ N 在 STM32 的 datasheet 中对 IO 端口的电压和注入电流的要求有限制, 以STM32G474 为例, 在 Absolute maximum ratings 章节中, IO 对输入信号电压的要求如下:! T+ E; t5 _2 V, w

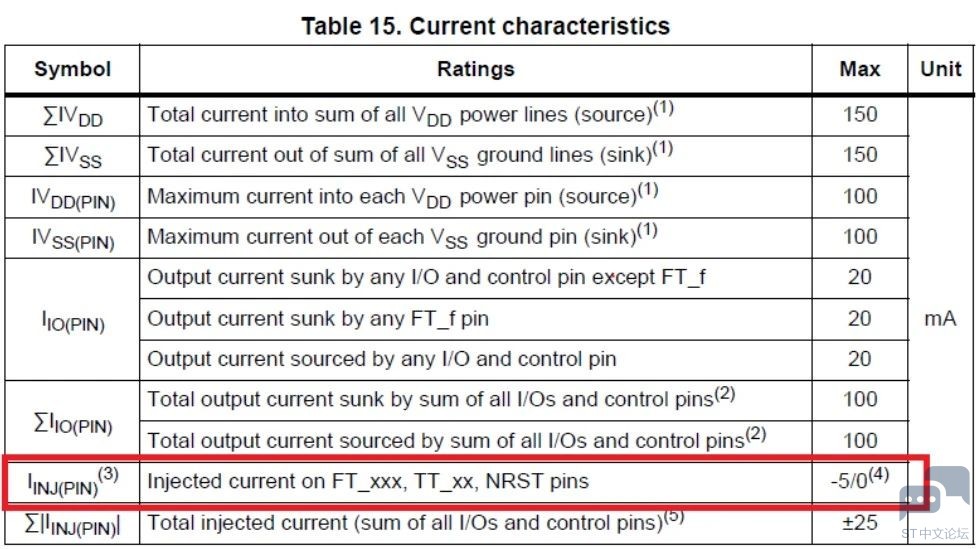

图2.IO 对输入信号电压的要求 2 w7 S% J- f$ `/ [' A z6 p$ S7 w4 b0 j6 ]; {3 Q' [9 P: t% t 很多人注意到了电压要求,认为只要加在 FT IO 的信号电平不超过 VDD+4V, 加在TT IO 的电平不超过 4V 都是安全的, 但是忽视了 IO 对工作电流和注入电流也有要求, 电流方面的要求也必须得到满足, 具体如下:) \& |7 Y3 G5 \0 e$ e* q7 O

图3. IO 对电流方面的要求 ; h( ?# f! x4 u& E$ Q可以看到, IO 对注入电流同样有着限制,在-5mA 到 0 之间,超出这一范围仍然可能造成 IO 的损坏。 ! e) c9 p) i$ @1 A$ |! ? 对于 STM32 的使用来说, 电平和电流方面的限制必须都得到满足。2 [, {' w( K: A7 g t8 F: _# \- w+ B4 J 03 TT IO 的注意事项 使用者对加在 IO 的电平幅度限制一般都能遵守,但是对于 IO 电流特别是注入电流的严格限制往往被一些使用者忽视,然而实际上, IO 对注入电流的限制往往对加在 IO 管脚的信号电平提出了更高的要求。% P% u! s9 Q( D- t* y& d: N5 } * O: e) u+ O* n2 v9 }# `! n 对于 FT 类型 IO 来说, 只要信号电压在使用的合理范围内,正的注入电流是不可能产生的。 - ]" U6 E' Q$ t3 k& ]/ E # i7 W& y: Z! a 对于 TT 类型 IO 来说, 超过 VDDA+0.3V 的信号电压都有可能产生 大于 0mA 的正向注入电流,这个电流流过芯片内部参数没有保证的模拟单元寄生二极管,从而可能导致电路损伤。 * R0 K) {" |/ O) V3 ^ 9 U- t- L; a* i: {; L 因此对 TT IO 的电平 小于 VDDA+0.3V 的限制在任何场景下都必须满足。 ' Q: `4 l' J( @( f ; M7 {- i2 a4 m 一个常被忽视的场景是系统上电时, 在 STM32 的供电系统还没有建立时, STM32 的IO 信号已经加在了 IO 管脚,例如某些电源或电机应用中对母线电压的检测,通常用分压电阻将母线电压分在 1V~2V 之间后连接到 STM32 的某一 ADC 采样输入 IO,通常这一分压电压到达 IO 比 VDD 建立更早。如果这一 IO 是 FT 类型的, 那么 IO 的信号电平始终能满足 小于 VDD+4V 的要求, 不管 VDD=0V 或 3V3。但是假如这一信号所接的是 TT 类型的 IO, 那么在 VDD=0 或低电平时, 母线电压分压后的电平将超过 VDDA+0.3V 的限制,带来芯片损坏的可能。 / {9 S/ ~( J$ q0 V: b 为了避免 TT IO 损坏,在系统上电,下电或工作的整个过程中, 必须始终满足 TT IO 端口电平 小于 VDDA+0.3V 的要求. 当 TT IO 的信号电平可能超过 VDDA+0.3V 时, 钳位保护电路是必须的。 2 k- [+ A E( Z) L5 S: z1 k4 D) n 在上述母线电压检测的案例中, 如果这一检测管脚不得不使用 TT IO, 那么一个从信号到 VDDA (或同电位的其它电源)的钳位二极管将可以防止 VDD=0 等场景下信号电平超范围的可能。 04小结0 A6 L) U/ E# @& n! ]8 F" X 在 IO 管脚的使用中, 电平限制和电流包括注入电流的限制必须同时得到满足。 " V0 T2 i7 k' L! k' B TT IO 由于内部结构的原因,更容易产生正的注入电流而给 IO 带来损坏。注入电流的限制给 IO 端口的信号电平带来了更严格的要求。 5 S x4 L# j' }" S2 N+ H 在使用中, 必须考虑信号电平的时序,确保在任何场景下 TT IO 的信号电平满足小于VDDA+0.3V 的要求, 必要时可以通过钳位电路来达到这一目的。3 h+ C- D6 }# u$ `' Y 转载自: STM32单片机 如有侵权请联系删除6 s1 |: L6 d& Z & Y# p6 a7 \0 e! a; E2 B) m 2 p& y; ?0 {, m4 H! r! Z" @ |

基于STM32的BootLoader经验分享

基于STM32如何选择 S2-LP 的外部晶体经验分享

基于是STM32的BLE 设备地址经验分享

基于ToF传感器的3D手势识别

NUCLEO-U545RE-Q评测(2)运行环境建立

基于STM32使用Framebuffer_Analyzer工具调试图像显示

ST安全连接,护航工业物联网一路前行

基于STM32的TouchGFX 4.22解锁新功能经验分享

基于STM32的MPU子区经验分享

使用Framebuffer_Analyzer工具调试图像显示