|

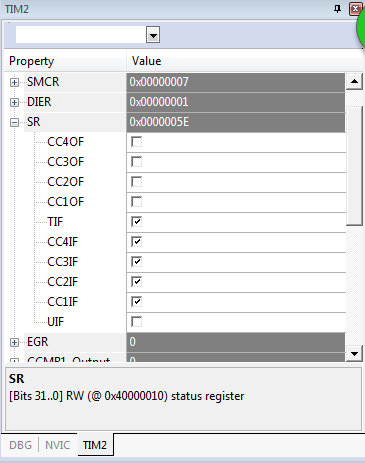

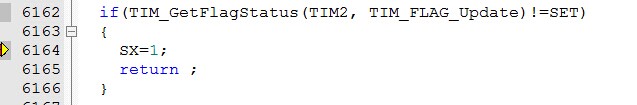

本帖最后由 james-351009 于 2014-12-13 16:33 编辑 最近在使用STM32F407的定时器,遇到一个诡异的问题。 我用TIM2做PWM波形输出,用了一个OC脚。中断的配置是只有更新事件产生中断。 在每个更新事件产生时,UIF位由硬件置位,系统进入中断例程。那么问题来了,在UIF没有置位的时候 也能进中断例程吗?这个现象是偶尔产生,而且这个中断是紧跟在正常更新中断例程之后产生的! 在中断使能寄存器里,我只使能了UIE位!而这个莫名其秒的中断,是怎么回事呢?! 下面是在进入那个中断时的寄存器截图:

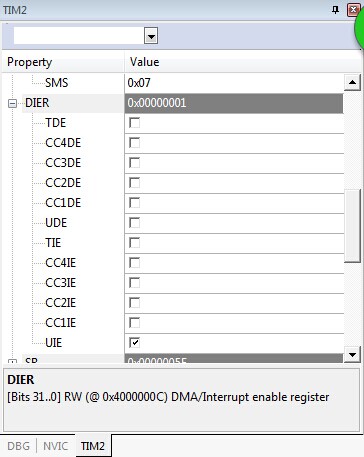

只使能了 UIE

这是我加的监测程序,在中断例程的最前面,也没有检测UIF置位! 上面是中断时的寄存器截图 请各位大神以及STM32官方能给个说法!谢谢了! |

请问我的CubeMX为什么初始界面没有ai选项,进去之后也没有addnetwork?

ST Motor Control Workbench卡在如图界面,生成不了代码

SDIO 标致位 没有变

程序卡死在USB_EPStartXfer这里

SDIO 初始化 死在 __HAL_RCC_SDIO_CLK_ENABLE语句上

我现在使用STM32F446ZET6芯片,外挂了16m的片外SDRAM。想把程序在SDRAM中运行,一直尝试没有成功,希望得到帮助,是否有相关的例子或参考的文档

MotorControl Workbench 6.4.1 生成 FOC 项目代码后运行死机。

STM32F405rgt6 I2S DMA输入会造成卡死,这个芯片有BUG

USBX在F407上创建CDC不能正常使用

STM32F427ZGTx内部RTC秒及亚秒同步问题

微信公众号

微信公众号

手机版

手机版

previously set by software. However trigger mode can set the CEN bit automatically by

hardware.

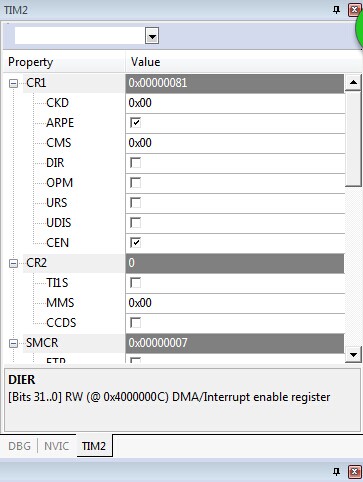

SMS:External Clock Mode 1 - Rising edges of the selected trigger (TRGI) clock the counter.

注意SMS设置为External Clock Mode 1以后,在开始的时候会产生一个触发事件,就是TRGI。

在注意TIF产生的来源:This flag is set by hardware on trigger event (active edge detected on TRGI input when the slave mode controller is enabled in all modes but gated mode. It is set when the counter starts or stops when gated mode is selected. It is cleared by software.

你把SMS的值修改以后,这个中断应该就不会产生了。楼主可以考虑修改为000,然后测试一下。

感谢大神显身。

TIM2中断例程相当于一个计数功能,在使用前配置好,开启中断,再使能TIM2。在计数没有达到预期之前,是不会使能和关闭中断的。上述现象是发生在这个过程中的,并未操作任何TIM2的寄存器。不知道我说明白没有

希望有更多大神关注啊!能提供线索者有奖

补充一下,这个中断的优先级是最高的,另外我也使用TIM3,TIM4无此现象,而TIM2唯一特殊的是32BIT的.

没有设置GATED模式。相同配置下TIM3,TIM4没有此问题出现。

上图中的TIF是触发了,但我没有使能相应的中断位,DIER中可以看到。

谢谢你的回复 ,配置在上面的图中都能看到的,你所关心的SMCR的值也有。

回头试试,但可能性不大,谢谢你的回复