|

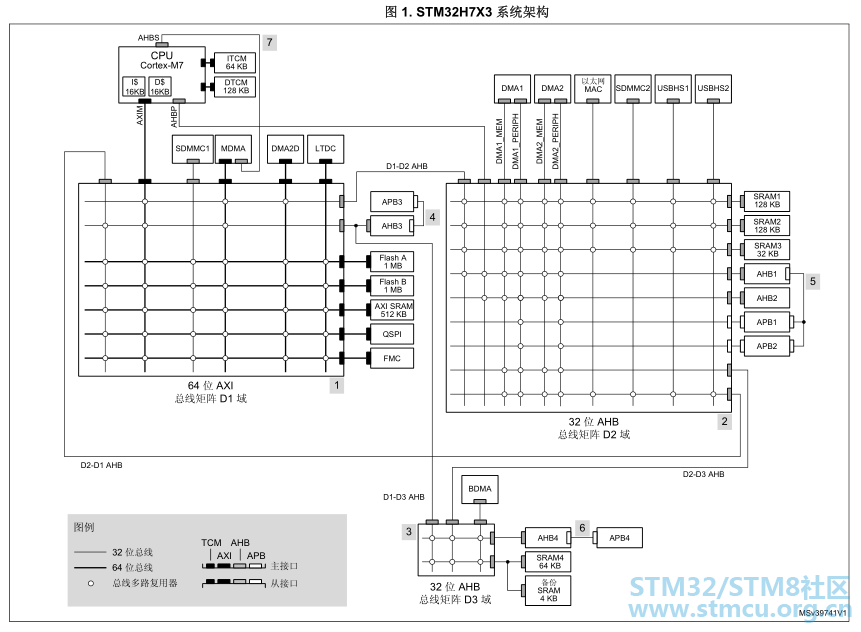

1 文档约定 2 存储器和总线架构 2.1 系统架构 通过一个 AXI 总线矩阵、两个 AHB 总线矩阵和总线桥,可以将总线主设备与总线从设备实 现互连,如 表 1 和 图 1 所示。

2.1.1 总线矩阵 D1 域中的 AXI 总线矩阵 D1 域中的多 AXI 总线矩阵为从多个主设备到多个从设备的并发访问提供保证和仲裁。这样可实现高速外设的高效同步运行。 仲裁采用带 QoS 功能的轮循调度算法。 DTCM 和 ITCM(数据和指令紧密耦合 RAM)通过专用 TCM 总线直接连接到 Cortex-M7 内核。MDMA 控制器可通过 AHBS(特定的 CPU 从设备 AHB)访问 DTCM 和 ITCM。ITCM由 Cortex-M7 以 CPU 时钟速度(零等待周期)访问。 有关 AXI 互连的更多信息,请参见 第 5 节: AXI 互连 。 D2 域和 D3 域中的 AHB 总线矩阵 D2 域和 D3 域中的 AHB 总线矩阵为从多个主设备到多个从设备的并发访问提供保证和仲 裁。这样可实现高速外设的高效同步运行。 仲裁采用循环调度算法。 2.1.2 总线- 总线桥 系统中具有大量的总线-总线桥,用于在不同总线类型的外设之间实现通信。 D1 和 D3 域中的 AHB/APB 总线桥可将 APB3 和 APB4 上的外设分别连接到 AHB3 和AHB4。D2 域中的 AHB/APB 总线桥可将 APB1 和 APB2 上的外设连接到 AHB1。这些AHB/APB 总线桥提供完全同步接口,允许 APB 外设依靠与其所连接的 AHB 无关的时钟来运行。 AHB/APB 总线桥还可将 APB1 和 APB2 外设分别连接到 DMA1 和 DMA2 外设总线,而无需通过 AHB1。 AHB/APB 总线桥可将 8 位/16 位 APB 数据转换为 32 位 AHB 数据,具体通过将 8 位/16 位APB 数据复制到 32 位字的三个高位字节/高位半字来实现。 AXI 总线矩阵在其从总线接口上集成 AHB/AXI 总线桥功能。 图 1 中标记为 32 位的主设备接口上的 AXI/AHB 总线桥在矩阵外部。 Cortex-M7 CPU 从其 AHBS 从设备 AHB 提供 AHB/TCM 总线(ITCM 和 DTCM 总线)转换,以允许 MDMA 控制器访问 ITCM 和 DTCM。 2.1.3 域间总线 D2-D1 AHB 该 32 位总线将 D2 域连接到 D1 域中的 AXI 总线矩阵。它使得 D2 域中的总线主设备能够访 问 D1 域中的资源(总线从设备),以及通过 D1-D3 AHB 间接访问 D3 域中的资源(总线从 设备)。 D1-D2 AHB 该 32 位总线将 D1 域连接到 D2 域 AHB 总线矩阵。它使得 D1 域中的总线主设备能够访问 D2 域中的资源(总线从设备)。 存储器和总线架构 RM0433 98/3019 文档 ID 029587 Rev 1 [English Rev 3] D1-D3 AHB 该 32 位总线将 D1 域连接到 D3 域 AHB 总线矩阵。它使得 D1 域中的总线主设备能够访问 D3 域中的资源(总线从设备)。 D2-D3 AHB 该 32 位总线将 D2 域连接到 D3 域 AHB 总线矩阵。它使得 D2 域中的总线主设备能够访问 D3 域中的资源(总线从设备)。 2.1.4 CPU 总线 Cortex ® -M7 AXIM 总线 Cortex ® -M7 CPU 使用 64 位 AXIM 总线访问所有存储器和外设(ITCM、DTCM、AHB2 外设除外),同时由于寻址不兼容性,AHB1、APB1 和 APB2 外设也排除在外。 该 AXIM 总线将 CPU 连接到 D1 域中的 AXI 总线矩阵。 Cortex ® -M7 ITCM 总线 Cortex ® -M7 CPU 使用 64 位 ITCM 总线从 ITCM 中获取指令和访问数据。 Cortex ® -M7 DTCM 总线 Cortex ® -M7 CPU 使用 64 位 DTCM 总线访问 DTCM 中的数据,而且也可以从其中获取指令。 Cortex ® -M7 AHBS 总线 Cortex ® -M7 CPU 使用 32 位 AHBS 从总线以允许 MDMA 控制器访问 ITCM 和 DTCM。 Cortex ® -M7 AHBP 总线 Cortex ® -M7 CPU 使用 32 位 AHBP 总线通过 D2 域中的 AHB 总线矩阵访问 AHB1、AHB2、 APB1 和 APB2 外设。 ......................... 阅读更多内容,请下载文档 |

| 谢谢破总分享知识 |

| 谢谢楼主的分享 |

STM32H750 外扩 QSPI FLASH 跑 2 小时就死机?LAT1151 官方根治方案

STM32H723 多通道序列 ADC 启动不了?寄存器操作必须等 ADRDY 就绪

经验分享 | STM32H7 LPTIM+DMAMUX+BDMA应用演示

经验分享 | STM32H7系列ADC DMA传输异常案例分享

经验分享 | STM32H7 MDMA 与通用DMA的联动传输示例

STM32H750 基于 Keil 制作 QSPI 外部 Flash 下载算法 全流程实操指南

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

微信公众号

微信公众号

手机版

手机版