|

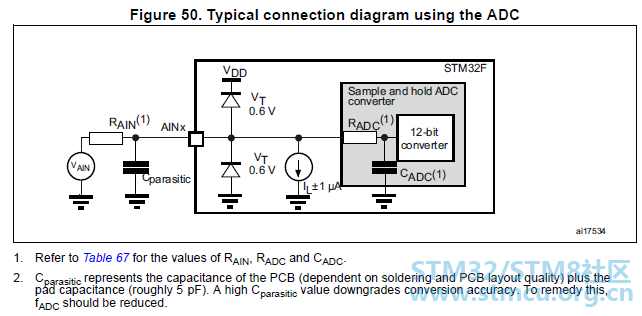

我准备用STM32F407 3ADC交替采样达到7.2MSPS的采样率,但是在计算输入阻抗的时候碰到个问题不解 按照手册ADC大概是这样的等效电路

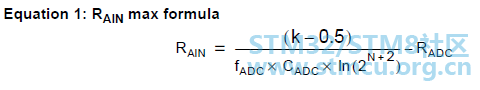

然后根据手册里面的公式

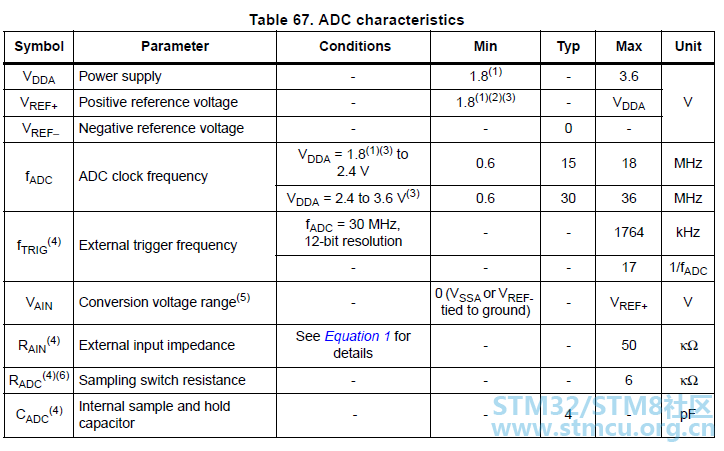

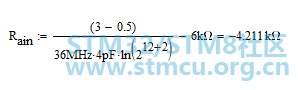

可以计算Rain的最大值,这里因为设置为3ADC 交替实现7.2MSPS的采样率,所以K=3 CYCLE, fadc=36MHz,N=12,其他参数查上面的数据表可知。

算出来Rain都是负值了,很疑惑怎么能是负值呢?那是不是意味着F407不能通过3ADC 交替实现7.2MSPS的采样率,或者说精度有影响,要保证精度的话采样周期或者adc时钟要下降? 或者也有可能他给出的Radc是1.8v下的最大值,但是因为没有给出3.3v下的值所以无从知晓最小值。 请教请教,帮忙看看哪里考虑的不对,谢了 |

| 等回复 |

| 等回复+1 |

观测器

stm32f405rgt6为什么无法串口连接STM32CubeProgrammer?

STM32F429 二级启动程序 (sboot) 开发难点:LD 文件 / 堆栈 / NVIC 及 startup.s 修改疑问

debug选项卡中的trace enable选项是灰色的无法勾选

STM32F407ZGT6的SD卡通过DMA控制时,无法从外部SRAM取数据

请问原子哥,STM32F407例程力,FFT测试章节里,计算时间统计正确吗?

STM32F407读写U盘出现程序卡死问题

我最近在用stm32f407做CAN通讯的回环+静默,但是现在显示可以成功发送数据,FIFO接收不到数据,这是什么原因啊

vscode如何使用CUBECTL

串口空闲+DMA接收GPS信号,空闲中断触发时间不对。

微信公众号

微信公众号

手机版

手机版