|

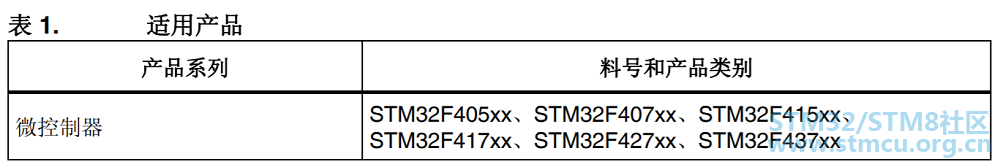

STM32F40xxx、STM32F41xxx、STM32F42xxx、STM32F43xxx基于 ARM 内核的 32 位高级 MCU 前言 本参考手册面向应用开发人员,提供有关使用 STM32F405xx/07xx、STM32F415xx/17xx、STM32F42xxx 和 STM32F43xxx 微控制器存储器与外设的完整信息。 STM32F405xx/07xx、STM32F415xx/17xx、STM32F42xxx 和 STM32F43xxx 构成一个微控制器系列,各产品具有不同的存储器大小、封装和外设。 有关订购信息以及器件的机械与电气特性,请参见数据手册。 有关 ARM Cortex™-M4F 内核的信息,请参见《Cortex™-M4F 技术参考手册》。 相关文档 意法半导体网站 (http://www.st.com) 提供以下文档: ■ STM32F40x 和 STM32F41x 数据手册 ■ STM32F42x 和 STM32F43x 产品简介 ■ 有关带 FPU 的 ARM Cortex™-M4 内核的信息,请参见《STM32F3xx/F4xxx Cortex™-M4 编程手册》(PM0214)。

1 文档约定 在本文档中,将具有 FPU 的 Cortex-M4 内核称为 Cortex-M4F。 1.1 寄存器相关缩写词列表 寄存器说明中使用以下缩写词: 读/写 (rw) 软件可以读写这些位。 只读 (r) 软件只能读取这些位。 只写 (w) 软件只能写入该位。读取该位时将返回复位值。 读取/清零 (rc_w1) 软件可以读取该位,也可以通过写入 1 将该位清零。写入“0”对该位的值无影响。 读取/清零 (rc_w0) 软件可以读取该位,也可以通过写入 0 将该位清零。写入“1”对该位的值无影响。 读取/读取清零(rc_r) 软件可以读取该位。读取该位时,将自动清零。写入“0”对该位的值无影响。 读取/置位 (rs) 软件可以读取该位,也可将其置 1。写入“0”对该位的值无影响。 只读写触发 (rt_w) 软件可以读取该位。写入“0”或“1”时,将触发事件,但不会影响该位的值。 切换 (t) 软件只能通过写入“1”来切换该位。写入“0”无影响。 保留 (Res.) 保留位,必须保持复位值。 1.2 词汇表 本节简要介绍本文档中所用首字母缩略词和缩写词的定义: ● 在本文档中,将具有 FPU 的 Cortex-M4 内核称为 Cortex-M4F ● CPU 内核集成了两个调试端口: — JTAG 调试端口 (JTAG-DP) 提供基于联合测试工作组 (JTAG) 协议的 5 引脚标准接口。 — SWD 调试端口 (SWD-DP) 提供基于串行线调试 (SWD) 协议的 2 引脚(时钟和数据)接口。 有关 JTAG 和 SWD 协议的信息,请参见《Cortex-M4F 技术参考手册》。 ● 字:32 位数据/指令。 ● 半字:16 位数据/指令。 ● 字节:8 位数据。 ● 双字:64 位数据。 ● IAP(在应用中编程):IAP 是指可以在用户程序运行期间对微控制器的 Flash 进行重新编程。 ● ICP(在线编程):ICP 是指可以在器件安装于用户应用电路板上时使用 JTAG 协议、SWD 协议或自举程序对微控制器的 Flash 进行编程。 ● I-Code:此总线用于将 CPU 内核的指令总线连接到 Flash 指令接口。通过此总线可执行预取操作。 ● D-Code:此总线用于将 CPU 的 D-Code 总线(数据加载和调试访问)连接到 Flash 数据接口。 ● 选项字节:存储于 Flash 中的产品配置位。 ● OBL:选项字节加载器。 ● AHB:高级高性能总线。 ● CPU:指 Cortex-M4F 内核。 1.3 外设可用性 STM32F405xx/07xx 和 STM32F415xx/17xx 系列中各型号产品的外设可用性及数量信息,请参见 STM32F405xx/07xx 和 STM32F415xx/17xx 数据手册。 STM32F42xxx 和 STM32F43xxx 系列中各型号产品的外设可用性及数量信息,请参见STM32F42xxx 和 STM32F43xxx 数据手册。 |

| 点赞 |

F429I-DISC1体验报告(4) 温度可视化动态图表的实现丨国庆开发板测评活动

STM32串口自动识别波特率的原理

STM32应用过程中与电源相关的案例分享

【经验分享】STM32F4 CAN2只能发送无法接收问题解决

F429I-DISC1体验报告(3) 画板线条绘制和调色功能的实现丨国庆开发板测评活动

F429I-DISC1体验报告(2) 按钮和弹窗GUI的简单交互设计丨国庆开发板测评活动

STM32固件库分享,超全系列整理

STM32系列芯片之间相互移植注意事项

使用 U 盘更新 STM32F4DISCOVERY 板固件

STM32如何成为现代科技的隐形引擎

微信公众号

微信公众号

手机版

手机版