.png) STMCU小助手

发布时间:2021-10-19 10:31

STMCU小助手

发布时间:2021-10-19 10:31

|

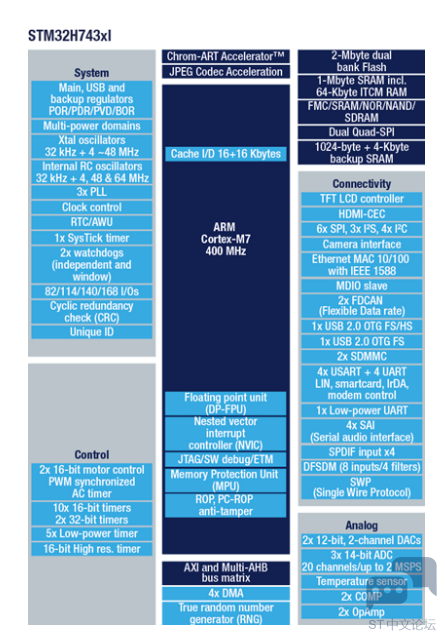

第3章 STM32H7整体把控 初学STM32H7一定要优先整体把控芯片的框架,不要急于了解单个外设的功能。( }$ z7 W! @0 d* R, H7 X- X5 w+ q) ^/ | 3.1 初学者重要提示7 ]% N& A( d' v) o 学习一款新的芯片,优先掌握系统框架是比较重要的,建议逐渐养成这种学习习惯,然后各个击破即可。 本章节提供了多张STM32H7的框图,这些框图都非常具有代表性。很多时候记忆知识点比较费脑子,记录这些框图是一种非常好的方式。( S# D/ D) N2 l2 I; n 对于本章节提供的部分知识点,无法理解透彻,暂时没有关系。随着后面的深入学习,基本都可以掌握。9 t |, J* w% Z+ E 重要的MPU和Cache知识分别放在了第23章和第24章。; L& O; c% p" i E6 F$ x* d 3.2 STM32H7硬件框图7 m P5 n$ t& Z 学习一款新的芯片,需要优先了解一下它的整体功能设计。需要的资料主要是来自官网和数据手册,比如我们V7开发板使用的STM32H743XIH6,直接在官方地址:链接(这是超链接)就可以看到对此芯片所做的介绍,页面中有一个如下的框图,对于了解STM32H7整体设计非常方便。

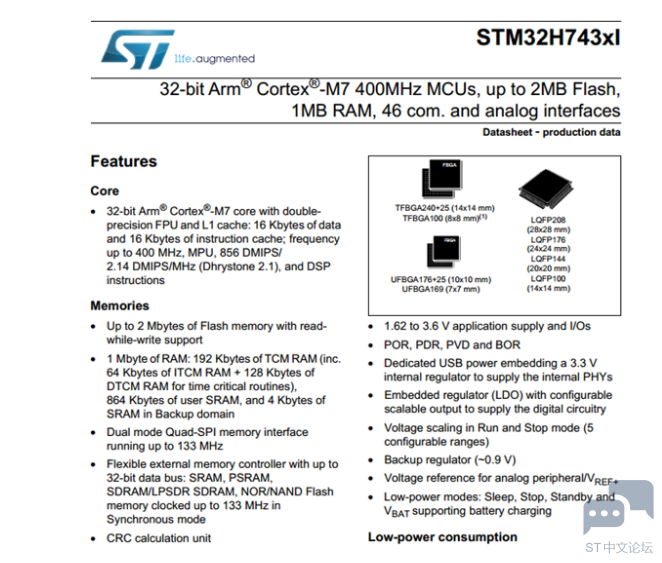

; r& J7 I! ~! X, d0 k( b3 p 3.3 STM32H7各个型号的区别% H! u$ F9 w( K5 V) j9 i- Z7 l 涉及到芯片选型的时候,需要大家了解各个型号的区别。对此ST有一个专门的文件STM32H7x3 MCUs High-performance line,在链接(这是一个超链接)里面可以找到。此文件里面有简单的对比,只是内容比较简单,仅两页,不过也言简意赅。最主要的是下面的这个截图:( ]" \2 C; F, |, g: x

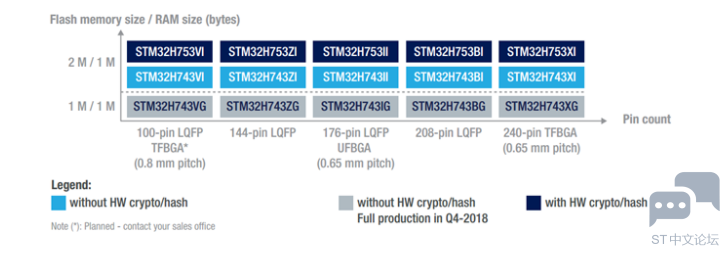

) O0 U( E# g& ~' `7 g 需要了解更详细的对比信息,可以看数据手册。任意下载一个型号的数据手册,在数据手册的的Table 2里面有详细的对比,如下图所示(部分截图):

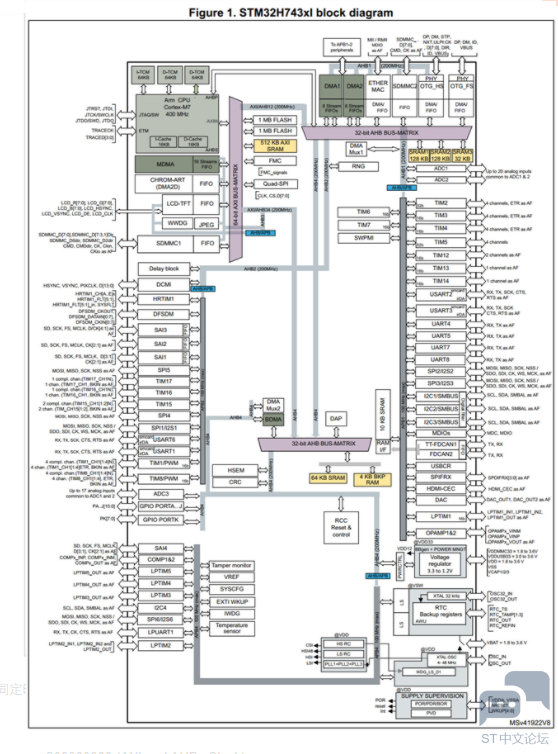

( j/ b4 ^1 w7 }0 V5 K 5 t A# \; @8 y" |1 h+ _ 3.4 STM32H7总线框图和时钟" r' F, i: p) [0 R& D STM32H7的数据手册里面提供了一张非常棒的框图,大家可以方便地查看每个总线的时钟速度和这个总线所挂的外设。这个在大家配置外设时钟分频的时候还是非常有用的,因为外设的时钟分频就是建立在所挂的总线速度(大家直接在数据手册里面检索Figure 1就可以找到)。* t4 U/ H& \! e* T) m

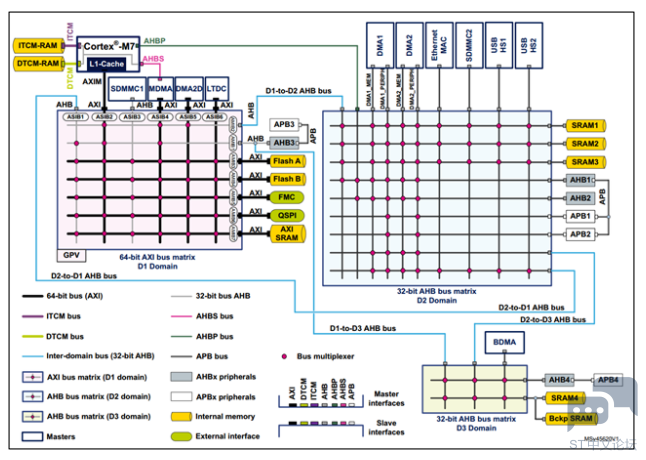

SYSCLK(Hz) = 400000000 (CPU Clock)2 x+ A# Z1 G' u HCLK(Hz) = 200000000 (AXI and AHBs Clock) AHB Prescaler = 29 g6 `2 ?! i& \ D1 APB3 Prescaler = 2 (APB3 Clock 100MHz)! U% m. O# P/ y3 P D2 APB1 Prescaler = 2 (APB1 Clock 100MHz) D2 APB2 Prescaler = 2 (APB2 Clock 100MHz) D3 APB4 Prescaler = 2 (APB4 Clock 100MHz) 因为APB1 prescaler != 1, 所以 APB1上的TIMxCLK = APB1 x 2 = 200MHz;* o7 H- u3 A. }! N2 H/ Z9 K G, R* f# A5 I# `% a7 I 因为APB2 prescaler != 1, 所以 APB2上的TIMxCLK = APB2 x 2 = 200MHz;% Z: m/ B$ Y5 E3 S7 X v/ L3 [ APB4上面的TIMxCLK没有分频,所以就是100MHz; APB1 定时器有 TIM2, TIM3 ,TIM4, TIM5, TIM6, TIM7, TIM12, TIM13, TIM14,LPTIM1 APB2 定时器有 TIM1, TIM8 , TIM15, TIM16,TIM17' U0 s3 H! q7 \ u APB4 定时器有 LPTIM2,LPTIM3,LPTIM4,LPTIM5# j, s0 \) F5 ^. {7 o - r8 }: y4 L7 R" T8 l1 H/ B / a1 \ M) S" H 3.5 STM32H7的A**线% t3 z" _9 y3 M' G/ u4 {, W A**线在STM32H7中有着举足轻重的作用。高并发性全靠这个总线了,先来看下A**线的框架: - }- Z$ r ~ d. O7 a- ?. y, A % @9 j) E# \% w 3.5.1 总线系统框架2 n8 r1 D) Y3 _0 w* D 下面这个截图比较有代表性,可以帮助大家理解STM32H7总线系统。

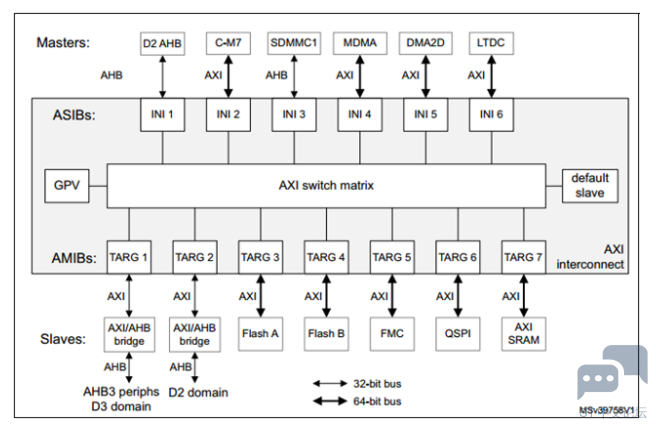

) }' j4 a) r4 o- i5 x% A, C i # N$ y _* ]+ B! m D1 Domain: O2 L: Y) s- | C7 d6 ~9 F: u ' h; N1 ]2 u' u3 z$ k D1域中的各个外设是挂在64位A**线组成6*7的矩阵上。3 p+ Y$ |1 i- A# o! s7 l0 { j9 u: j* y: q: M 6个从接口端ASIB1到ASIB6 J0 c0 Q3 {) _, S) f; @' a 外接的主控是LTDC,DMA2D,MDMA,SDMMC1,AXIM和D2-to-D1 AHB 总线。+ Q9 f) N; ]: y% C/ A1 y) h6 Y; W" t ; |' D4 r5 z. x9 y 7 y' ]( y, f- T 7个主接口端AMIB1到AMIB7# }* m- A* d2 v5 r$ d5 b 外接的从设备是AHB3总线,Flash A,Flash B,FMC总线,QSPI和AXI SRAM。另外AHB3也是由A**线分支出来的,然后再由AHB3分支出APB3总线。 7 A6 [! R' E8 h" w( L. S: v1 L2 t9 b D2 Domain p. E* g! }. q5 K% X$ Z' l& ` 7 R7 E- T! y8 `" o0 } D2域的各个外设是挂在32位AHB总线组成10*9的矩阵上。 [( u! ?! l. [- \) m* E # b) z& u; A0 k. v, J 10个从接口 外接的主控是D1-to-D2 AHB 总线,AHBP总线,DMA1,DMA2,Ethernet MAC,SDMMC2,USB HS1和USB HS2。 0 |0 K1 C2 `% Q( f7 `3 m 9个主接口 外接的从设备是SRAM1,SRMA2,SRAM3,AHB1,AHB2,APB2,APB3,D2-to-D1 AHB总线和D2-to-D3 AHB总线。$ F1 T5 A' W# I% B" h* c- f2 l - S* `2 l! x2 h# m" b D3 Domain D3域的各个外设是挂在32位AHB总线组成3*2的矩阵上。/ k# o0 u. M& B, F4 O% ? & E1 W" }5 t3 d; U* a2 L ( M, H& R6 G8 \) V 3个从接口 外接的主控D1-to-D3 AHB总线,D2-to-D3 AHB总线和BDMA。9 b% A: p' e2 O2 g a 2个主接口 外接的从设备是AHB4,SRAM4和Bckp SRAM。另外AHB4也是这个总线矩阵分支出来的,然后再由AHB4分支出APB4总线。% a9 O1 D! b0 v; b' E3 i% `( c 这三个域之间也是有互联的,可以是: ; ]5 Y2 S% q, q D1域到D2域的D1-to-D2 AHB bus 允许D1域中的主接口外设访问D2域里面的从接口外设。比如D1域里面的DMA2D访问D2域里面的SRAM1。1 l4 ^, r! T7 q( Q- F4 |& v & _4 F) c }. r4 M1 Y D2域到D1域的D2-to-D1 AHB bus 允许D2域中的主接口外设访问D1域里面的从接口外设。比如D2域里面的DMA2访问D1域里面的AXI SRAM。$ V8 K$ q3 D+ B d0 t+ s ) c1 B* |* f- x, L5 y7 k# X# e % B0 p) y1 A! u8 S. H6 Q& b D1域到D3域的D1-to-D3 AHB bus/ \- Q6 k- H; s( C- V+ D 允许D1域中的主接口外设访问D3域里面的从接口外设。比如D1域里面的DMA2D访问D3域里面的SRAM4。% t& ?! \) Z, n1 _8 o D2域到D3域的D2-to-D3 AHB bus。 允许D1域中的主接口外设访问D2域里面的从接口外设。比如D2域里面的DMA2访问D3域里面的SRAM4。; ~+ r# d4 p3 X $ n) ?$ B8 j% F" |3 ~2 \1 x: U! l 有了这些知识后,下面我们重点了解A**线矩阵。 * {' n; F" C8 }# O 3.5.2 A**线特色 AXI支持高频率、高性能的系统设计: 6 X( p7 E4 v# f6 A 支持高带宽,低延迟设计。 提供高频操作,无需复杂的总线桥。 满足各种组件的接口需求。/ C8 N# j7 G4 V7 O2 h8 _ 适用于具有高初始访问延迟的内存控制器。 为互连架构的实现提供了灵活性。 与现有的AHB和APB接口向后兼容。2 t6 S9 A4 N+ y% {1 O3 z# G2 ` & f$ z0 n1 V0 @- e2 ^8 T6 R A**线的关键特性: ~) u: F8 f" o. d# ~ 独立的地址、控制和数据线。& Z& Y4 v+ b7 l% a! q9 h 支持非字节对齐方式传输。2 T" r/ D2 ^2 `3 v9 I% B, Y! {' q 基于起始地址的突发传输。" i) w2 |0 a$ Y9 H8 t 分开的读和写数据通道,且提供DMA传输。& B! `# `) n4 `' Y7 d1 k* u 支持发起多个地址。* v- m5 c' S3 s2 ~ 支持无序传输。 允许添加寄存器,以提供时序收敛。 ) o. q8 _9 C9 Q* y. B7 y5 k' R 5 B1 P* n4 J3 t A**线3 f9 d' |0 J E' I/ a 关于A**线,ARM有一篇古文观止级文档《AXI4_specification》,已经将其放在了论坛:http://www.armbbs.cn/forum.php?mod=viewthread&tid=87340 。 8 h5 r# b" n1 E# c9 l# t" C; m + ~8 [& |8 ^% y4 g/ S 3.5.3 A**线简介" {) ?' T; r( s3 n f 通过下面的框图,我们再进一步的认识一下A**线。2 O. @) ^6 ^$ N+ K3 O) \" C1 v

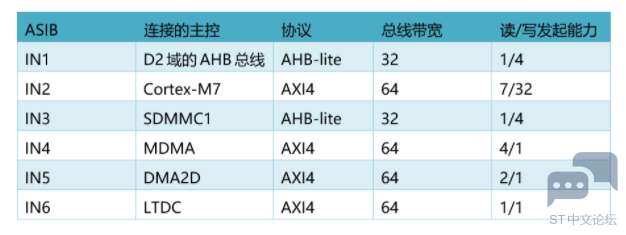

) \# L8 V/ N4 `4 x& I2 p 针对从接口ASIBs,描述如下:

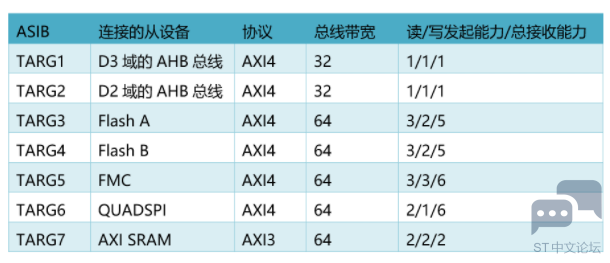

/ R+ H. b, E" @) _ 6 \: z$ `* [# R' M* g+ X 针对主控接口AMIBs,描述如下:

( q0 U7 g+ x+ k, T( J& s 3.5.4 A**线优先级编程 由于存在多个ASIB从接口访问AMIB主控的问题,这就涉及到谁先谁后等问题。所以A**线矩阵就做了一个基于优先级的仲裁方案。每个ASIB接口支持读通道和写通道分别设置,优先级从0到15。数值越大,优先级越高,默认情况都是优先级0。如果有两个传输同时到达AMIB主控接口,那么优先级高的ASIB接口传输优先处理;如果优先级相同的话,根据LUR方案选择(least recently-used最近最少使用情况)。% M& {8 q `. d' [3 O / p( M1 ~1 C; G( o7 n. S 大家在实际应用中,可以根据实际情况进行设置,一般情况下使用默认值即可。* k, [5 M5 h* P + H N: r! G4 x. R. [5 }2 V + e# J1 ]7 V/ v8 i. [% w 3.6 STM32H7的总线互联 STM32H7的总线矩阵四通八达,但不是任意Bus Master总线主控端和Bus Slave设备端都可以相互通信的:, ^; K9 R5 y& e& m# V( v

$ S1 d7 L, K# J0 `& ^" V % x0 x2 [, X9 [- g! G 访问通路(每个小方块里面的字符) R6 [" F/ x7 i . U1 x$ E Y d& p 1 B! R+ `: H# s: c9 _% c 任何有数字的表示有访问通路。 , ~8 y3 G% F( o4 }' | 短横杠“-”表示不可访问。& p+ l8 R$ J9 ^8 E, g C7 p, N. K2 o 有灰色阴影的表示有实用价值的访问通路。 : [5 g5 _1 @5 `/ s& {4 Y, e6 B . a" Z0 H5 M& N( j: y0 ?2 S 表格中具体数值所代表的含义 + Z. ^: L @& q8 _$ i4 M+ o D=direct 2 w+ P+ M! w* N, ] 1=via AXI bus matrix 2=via AHB bus matrix in D2 3=via AHB bus matrix in D3! j: I( p6 X/ G i' c 4=via AHB/APB bridge in D1 5=via AHB/APB bridge in D2' n# r( n% I( R/ n0 i # J% e' ?+ T5 K- |! v; g 6=via AHB/APB bridge in D3 7=via AHBS bus of Cortex-M7 8 ?, q4 r! ~" r. ^ " {" m; ^/ d q& l+ c+ t* V$ ~ 多个数值组合 = 互连路径以数字的顺序经过多个矩阵或/和桥。 ) N* j5 d. y" g2 a# s* z& k1 B 总线访问类型5 K! ~* Q; _1 M% c! B7 H0 j . H% T+ g8 j* T2 D, o 8 i+ s2 A4 E) z/ N; ]( r# N 普通字体表示32位总线。 斜体表示32位总线主机端/ 64位总线从机端。4 P' u8 j0 f1 p3 s; M4 E/ r ; d- ~( l& G9 V# E$ ] 4 _9 T. E/ r5 b+ s) A( ~" ^7 @& p5 b 粗体表示64位总线。 5 a% Q: O$ f7 e2 Y' ] 当前要对这个图有个了解,后面章节讲解各个外设的时候要用到,比如DTCM和ITCM不支持DMA1,DMA2和BDMA,仅支持MDMA。 * }, m: Q) V3 K7 `) y $ _6 d! E2 P3 L: q/ p$ \3 i 3.7 STM32H7的FLASH 首次学习STM32H7,要掌握以下几点认识即可: 1、双BANK,每个BANK的带宽都是64bits,如下图所示:* [ L5 n2 O8 \: \

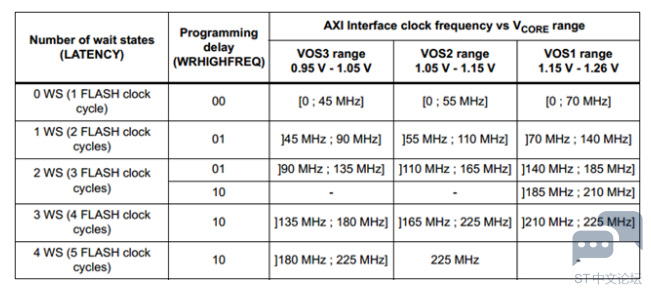

H7中已经没有F1和F4系列中的ART Chrome加速,通过H7中的Cache加速即可。具体延迟数值和主频关系如下:- _! Y- e6 u! r' L9 e u+ P# ^

+ g* ]! i/ Q# P6 C; |' O' A 3、Flash编程操作(写)最好以256bits为单位进行,应用中也可以小于256bits,但是容易造成ECC校验出问题,所以不推荐。Flash读操作支持64bits,32bits,16bits和8bits。+ m0 O; e& L1 _7 [ z 8 @/ u& a+ e; V- [; j; K. Y 4、Flash支持ECC校验,每256bits配10bit的ECC位,可以检测到1个bit并纠正或者检测2个bit。随着芯片的制造工艺水平越高,带电粒子能产生的位翻转就越多,此时的ECC是必须要有的,一般可以纠正1-2个bit。安全等级高的Flash类存储器和RAM类都是必须要带ECC的。 ECC相关知识。% B3 U4 r0 n# y g: F& H 3.8 STM32H7的RAM (注,学习本小节,优先回顾本章节3.5.1小节的框图,另外H7的RAM区也是支持硬件ECC的)" a: E9 J. g1 n# R4 e STM32H7的RAM区分为好几个部分,下面分别进行说明:0 [- a" G+ z/ C' W $ \, b! Z" e4 H6 ~# E3 ~1 W0 ? TCM区5 E. [, R4 o- o0 L1 h/ w 9 \4 c* o* h$ o0 i9 W: e TCM : Tightly-Coupled Memory 紧密耦合内存 。ITCM用于运行指令,也就是程序代码,DTCM用于数据存取,特点是跟内核速度一样,而片上RAM的速度基本都达不到这个速度,所以有降频处理。 * `/ W; r) }; ?1 o+ h, T8 _ 速度:400MHz。6 Y& P" \' m( O/ A2 ~. G$ z: _ , u( \8 A" `9 Z/ T DTCM地址:0x2000 0000,大小128KB。 5 L7 Z# H0 _* R" A4 H 0 ^( b2 U- e5 y# r3 | ITCM地址:0x0000 0000,大小64KB。 . ~8 D5 t1 L5 y: {; f: c; k6 } AXI SRAM区 3 \, w' h" m6 w' i 位于D1域,数据带宽是64bit,挂在A**线上。除了D3域中的BDMB主控不能访问,其它都可以访问此RAM区。 ) z( a# O9 W3 F; r! g5 i; ]3 [ 9 ]6 x5 J$ Z M) j! J# ~ 速度:200MHz。 地址:0x2400 0000,大小512KB。 用途:用途不限,可以用于用户应用数据存储或者LCD显存。 " y3 X' D7 p: p9 g3 l9 f+ }; j SRAM1,SRAM2和SRAM3区: \! q; Z$ }% A# u8 F0 @ 位于D2域,数据带宽是32bit,挂在AHB总线上。除了D3域中的BDMB主控不能访问这三块SRAM,其它都可以访问这几个RAM区。 . B2 O3 k6 `" a; o8 o1 Y 速度:200MHz。) [4 L8 S# l* }% Z! @ ( J4 S- T6 D- ]: _' [ % r$ z9 t9 T" e9 F! c SRAM1:地址0x3000 0000,大小128KB,用途不限,可用于D2域中的DMA缓冲,也可以当D1域断电后用于运行程序代码。: T. t1 P Z9 B3 ~2 N* E. _- G' [ SRAM2:地址0x3002 0000,大小128KB,用途不限,可用于D2域中的DMA缓冲,也可以用于用户数据存取。 & F0 [# y( H: d, Z8 c. ^ SRAM3:地址0x3004 0000,大小32KB,用途不限,主要用于以太网和USB的缓冲。 SRAM4区+ h9 o" t2 C$ A+ Q% D" B; | 4 o& A) e/ {' B: X7 P( g / [; B" r1 C: T, K/ _5 t7 \ 位于D3域,数据带宽是32bit,挂在AHB总线上,大部分主控都能访这块SRAM区。& f/ a) B7 I) i7 d' Z2 Z , o: b6 R& ~% V! I0 B+ D: b % \) U. G0 {) ]: a5 Y( H 速度:200MHz。 ( ?1 M6 ^$ E1 Q0 r0 Z5 | 地址:0x3800 0000,大小64KB。 . H. m9 W, B- _3 M 用途:用途不限,可以用于D3域中的DMA缓冲,也可以当D1和D2域进入DStandby待机方式后,继续保存用户数据。 9 J4 z0 C1 @5 k# Y' ?# o1 g Backup SRAM区 $ d* q. p% S/ C, U+ \# b4 ]2 _0 u 备份RAM区,位于D3域,数据带宽是32bit,挂在AHB总线上,大部分主控都能访问这块SRAM区。7 ~/ f; }* b' W6 S; m o& j4 b5 f1 K; }+ h: o- w 6 T+ @; Y. j4 w. Z5 Z 速度:200MHz。 4 z4 q+ f# o) |, c. } 地址:0x3880 0000,大小4KB。 $ d) _ ^. z; ?- p+ ~1 I 用途:用途不限,主要用于系统进入低功耗模式后,继续保存数据(Vbat引脚外接电池)。 / Q8 v6 j& L/ N9 `2 {/ W 3.9 总结 本章节就为大家讲解这么多,让大家对STM32H7有个整体的认识,后面章节将逐个进行学习。 * x) i9 f d8 M6 }& I& r 0 u# I1 Y) ?# S- F9 k " |9 g F% G9 w+ l( t. {$ @ |

【经验分享】STM32_H7_ADC

STM32H7R/S高性能MCU:安全性,大存储和优异图显赋能更多应用创新

Stm32H7XX GCC下分散加载实现

【银杏科技ARM+FPGA双核心应用】STM32H7系列10——ADC

DIY-STM32H750核心板

[nucleo-H7A3ZI-Q]1-点亮一个皮皮灯

DIY-STM32H743核心板

【银杏科技ARM+FPGA双核心应用】STM32H7系列57——MDK_FLM

1月10日有奖直播 | 基于STM32 的CODESYS智能自动化解决方案

STM32的CAN FD位定时设置注意事项