|

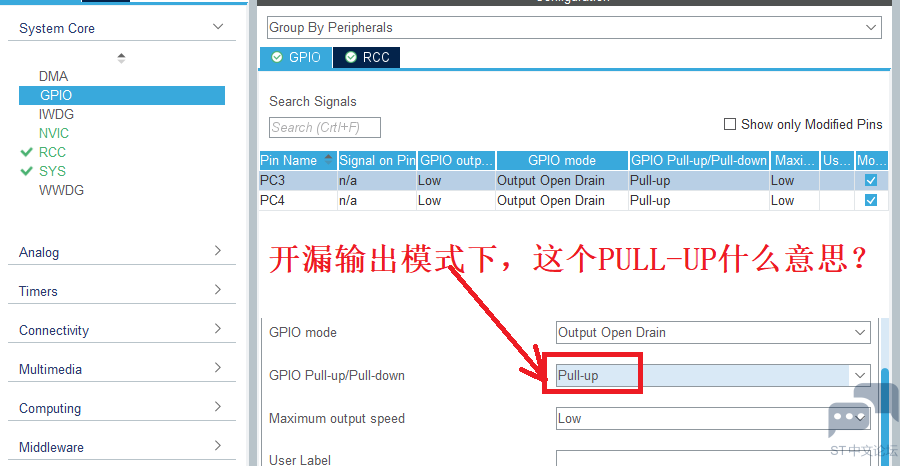

请教:对于STM32F103VCT,GPIO设置为Open Drain 带上拉电阻Pull-up,我的理解是GPIO经内部上拉电阻接到了VDD,GPIO可以输出高电平VDD的。但是,我用万用表测试引脚电平,高电平只输出1.4V左右,低电平输出0v。在PUSH-PULL模式下,万用表可以检测到引脚输出3.3V的高电平。Open Drain模式下,GPIO不能输出VDD=3.3V,原因是什么?我对Pull-up的理解是否正确? 恳请明白人给予解答,十分感谢! |

Stm32zest 零速全力矩控制算法在哪里可以看到,关键词是啥,有意了解购买

CubelIDE,HAL_FLASH_Program仿真时出错。

STM32F103 GPIO速度。

stm32f4的串口4不能接收?

STM32F407的定时器9和10怎么设置为主从关系

stm32f103 revision code X为什么读内部ID号时,时钟50M,会出错

关于STM32G替代STM32F问题

利用STM32F103的ADC采集模拟电压信号

STM32G031G8U6 flash读写问题

STM32F407ZGT6的低温性能如何

微信公众号

微信公众号

手机版

手机版

开漏就没有上下拉了吧

谢谢你的回答!在CubeMX中,开漏输出还有一个选项Output pull-up,即是否有上拉。

Pull-up是上拉输入的。可以看下文档的GPIO结构部分。

谢谢你的回答。在STM32CubeMX中设置GPIO时,开漏输出模式下还有一个PULL-UP,这个pull-up什么意思?

用示波器试试。

猜测原因之一也许与万用表的输入阻抗有关