.png) STMCU小助手

发布时间:2021-12-10 10:03

STMCU小助手

发布时间:2021-12-10 10:03

|

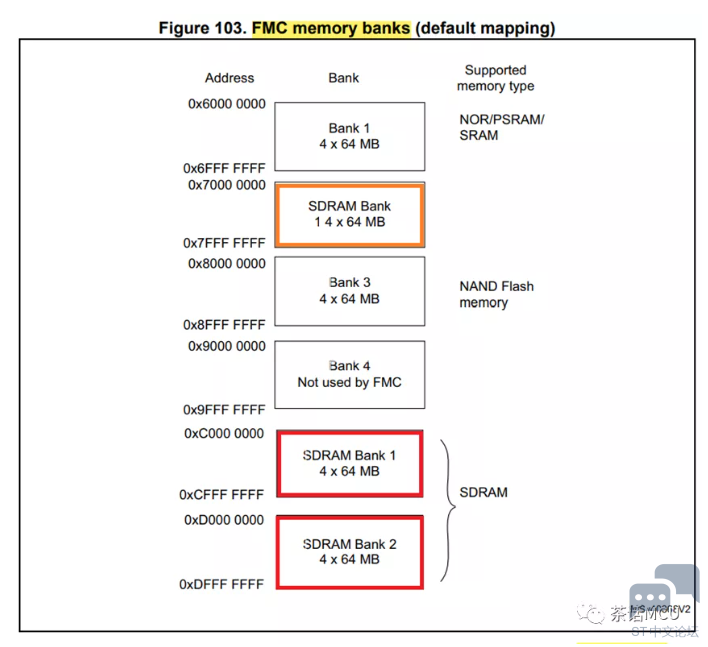

有人问及STMH7芯片参考手册中,关于FMC存储地址分配框图中关于SDRAM的地址问题,这里简单聊下。先看看下面FMC内存分区图:

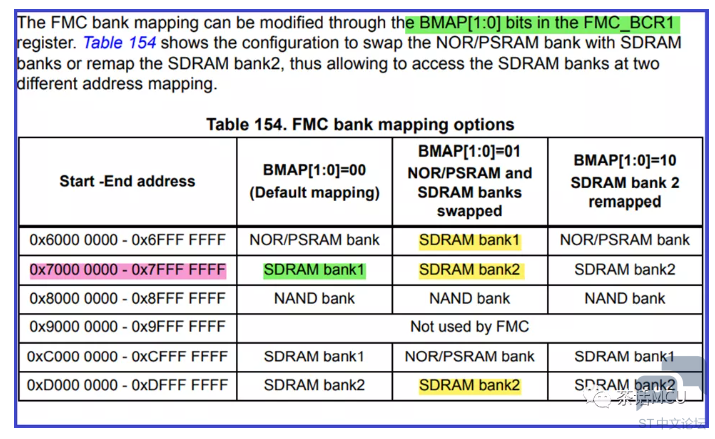

我们可以看到除了2个分别标志为SDRAM BANK1和SDRAM BANK2的地址区外【位于图最下方】,还有个标志为SDRAM Bank的存储区【位于框图中间】。这个没有编号的SDRAM区跟下方的BANK1、BANK2有没有关系,或者说中间那个SDRAM区是否独立于下方的BANK1和BANK2? 其实,中间那个SDRAM区只是下方BANK1或BANK2的地址别名区,并非多了个独立的SDRAM BANK。我们可以通过寄存器配置,让中间的这块SDRAM区成为下面BANK1或BANK2的别名区,即同样内容可以在2个地址空间访问。 为什么要这样,看看下表可配置情形即可看出端倪。不同的配置可以参考下表,不难看出中间那块SDRAM别名区[0x70000000-0x7FFFFFFF]可以映射成SDRAM BANK1或SDRAM BANK2以配合不同的应用需求。

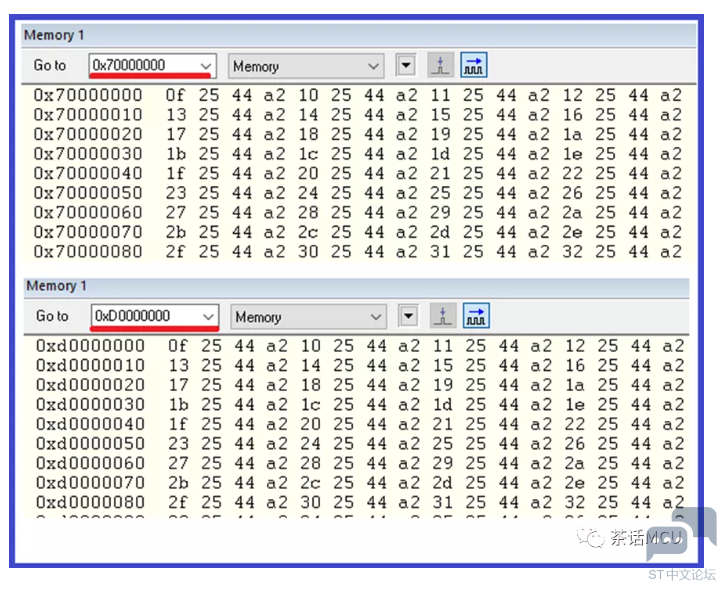

我们可以做个简单验证【基于STM32Cube库函数】: HAL_SetFMCMemorySwappingConfig(FMC_SWAPBMAP_SDRAM_SRAM); #define FMC_SWAPBMAP_DISABLE (0x00000000U) #define FMC_SWAPBMAP_SDRAM_SRAM FMC_BCR1_BMAP_0 #define FMC_SWAPBMAP_SDRAMB2 FMC_BCR1_BMAP_1 基于上面配置代码,我们将SDRAM BANK2也映射到了中间的SDRAM BANK区。实际操作时我们会发现访问BANK2和中间那块别名区的内容是一样的。

好,这个问题就简单分享到这里,权作提醒。 |

STM32H750 外扩 QSPI FLASH 跑 2 小时就死机?LAT1151 官方根治方案

STM32H723 多通道序列 ADC 启动不了?寄存器操作必须等 ADRDY 就绪

经验分享 | STM32H7 LPTIM+DMAMUX+BDMA应用演示

经验分享 | STM32H7系列ADC DMA传输异常案例分享

经验分享 | STM32H7 MDMA 与通用DMA的联动传输示例

STM32H750 基于 Keil 制作 QSPI 外部 Flash 下载算法 全流程实操指南

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

微信公众号

微信公众号

手机版

手机版