.png) STMCU小助手

发布时间:2022-2-27 15:39

STMCU小助手

发布时间:2022-2-27 15:39

|

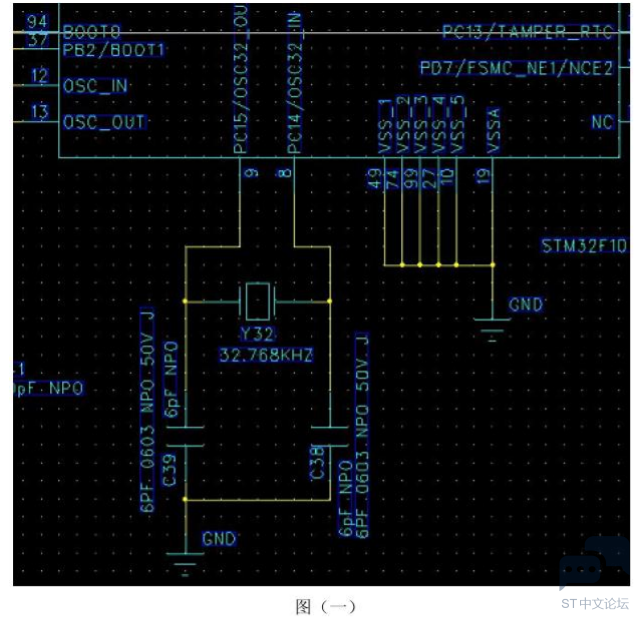

问题:- c- O* W* K4 [9 m' e8 i c3 S 该问题由某客户提出,发生在 STM32F103VCT6 器件上。据其工程师讲述:其产品中设计中,用到了STM32 的内部 RTC 功能,而 RTC 的时钟由 LSE 提供。在产品的小批量试产中,发现有个别产品开不了机。进一步测量发现,LSE 没有起振。8 p* p9 F/ g |* a 调研: 对有问题的产品重复测试,现象如其所述。通过运行测试程序发现,在使能 LSE 后长时间检测不到起振标志。检查 VDD、VDDA、VBAT、Vref+、Vref-、VSS、VSSA、NRST、BOOT0、BOOT1 等管脚的外部电路设计,未见异常。检查 LSE 外部电路设计,如图(一)所示:9 G5 u, D0 }4 J3 r' S4 ]

: N, H& ]8 i0 W8 X8 i ![3@4X[CX[_A]PJWARA~9$~%Y.png 3@4X[CX[_A]PJWARA~9$~%Y.png](data/attachment/forum/202202/27/155026fgtenzckxy4niaai.png)

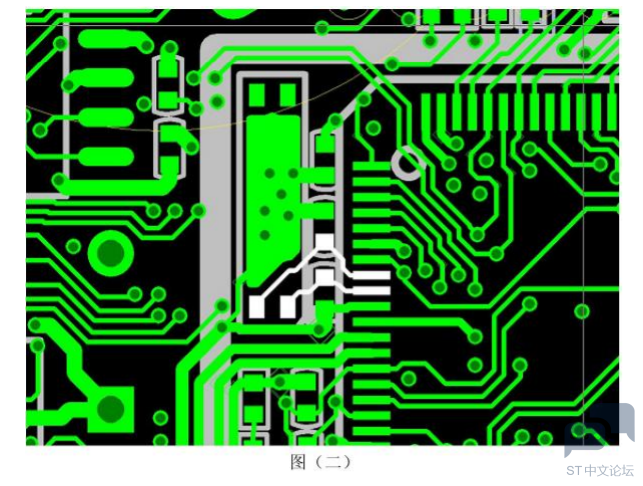

# w# \/ ^ C1 Z( U- V' s$ \: |1 ` 满足技术文档中要求的指标,该设计是没有问题的。检查其 PCB 设计,如图(二): ; i0 \, L Z8 h& I3 b& z- `. @

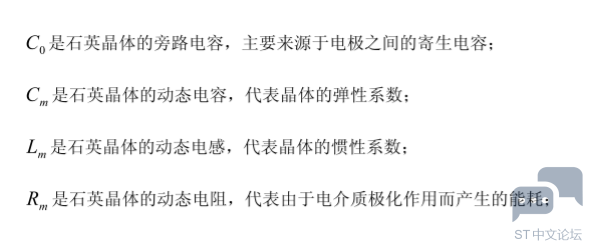

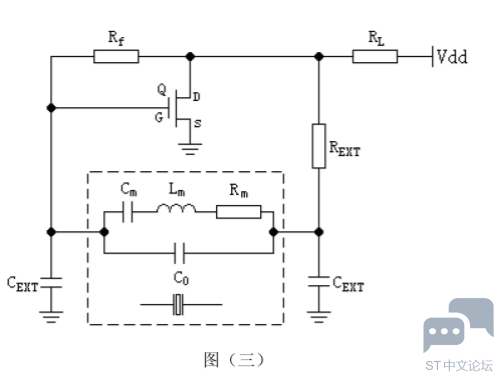

' h2 [% O. b3 @* c4 J. ?9 u4 D 相关的走线简短且有地包围,符合技术文档对 LSE 的布线的要求。检查测试的样品,发现其 PCB 外涂有电子绝缘胶,无法直接测量到 PCB 上的结点。清除 LSE 相关电路外的胶体,并使用乙醇清洗,然后用热风枪吹干。重新上电测试,发现 LSE 顺利起振。多次重复测试,结果相同。取另一个有问题的样品,清除相关区域的胶体后进行测试,仍 LSE 不能起振。再使用热风枪吹 30 秒以后测试,LSE 顺利起振。取多个有问题的样品,重复以上述处理及测试,结果完全一致。于是怀疑在涂胶前有水份凝结而造成漏电,从而导致 LSE 不起振。通过其工程师协调生产部门做一个实验批次,保证装配好的PCB 在烘干作业完成后立刻进行涂胶作业。实验结果显示,仍有部分样品存在 LSE 不起振问题。于是同该电子缘胶的生产商联系,其技术人员提供了一个重要的信息,即:该胶在固化过程中会有少量的乙醇分子游离出来,通过严格的工艺流程可以减少乙醇分子的数量。而之前生产的几个批次的样机,在胶体固化时间上不符合胶厂给出的工艺要求。按照胶厂给定的工艺参数,重新生产一个试验批次的样机。测试结果表明,LSE 不起振的样机比率明显减少,但不能杜绝。由于胶体固化问题已超出了专业范围,无法进一步研究,于是建议其工程师更改电路设计,使用有源时钟代替 LSE,或者同胶厂进一步研究如何提高胶体的固化效果。其工程师选择了前者。$ S* K1 g- L- \: ^$ G% F5 [& P . F& ^+ V) s6 U6 G4 o; n* p: D; e! S 结论:9 z. U! U3 S: R8 G5 o' _ 由于所使用的电子绝缘胶的固化工艺问题导致胶体中有乙醇分子游离出来,引起漏电,进而造成 LSE不起振。' ?( W1 M' h- X, q# y/ F+ F 处理: 改用有源时钟代替 LSE。' S, }4 g8 R4 s7 a4 } 建议:! m% b: m7 ]& K- F$ H7 `3 [ 集成在 STM32 上的晶体振荡器有两个,分别是 HSE 和 LSE。HSE 是高频振荡器,为 CPU 和大部分常规外设提供时钟源。LSE 是低频振荡器,专门为驱动 STM32 内部的 RTC 而设计的。两个振荡器都属于典型的皮尔斯振荡器,但由于某些关键参数的不同,使得它们对外的表现存在着很大的差别。在讨论具体问题之前,首先对皮尔斯振荡器的振荡条件在理论上作一个简单的分析。皮尔斯振荡器的结构如(三)所示,其中 MOS 晶体管 Q 和负载电阻 RL 构成一个反相器,而反馈电阻 Rf 使该反向器工作于线性放大区,起到一个反向放大器的作用。由石英晶体和两个 Cext容构成选频反馈网络。而 Rext 用于振荡功率调节。图(三)中的石英晶体用虚框内的 RLC 网络等效,其中:" B( `# M. G( {+ d1 p' m X 7 M8 | p# i* }5 R0 V

. c0 F2 ~7 j+ c

MOS 晶体 Q 的直流工作点可能由跨导曲线与负载曲线的交点求得,如图(四)所示。而跨导曲线在该点处的切线的斜率就是反向放大器的交流跨导 gm。所谓振荡器的振荡条件,也就是振荡器工作时 gm 所要满足的的条件。 : ~# X' |2 b% t5 M7 a2 O ![$SP@FJVH8`3P~96~4$LB)]2.png $SP@FJVH8`3P~96~4$LB)]2.png](data/attachment/forum/202202/27/155024il2adt25b655j2p3.png)

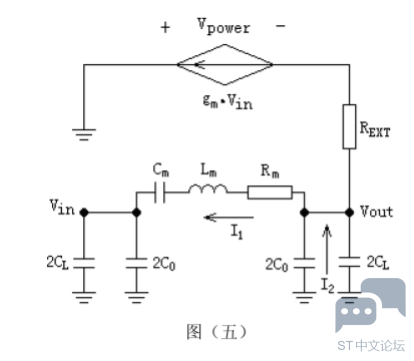

0 A3 t% w5 O, U" Q 通常,选频反馈网络中的两个电容 Cext 的容值相等,且等于石英晶体的负载电 CL 的 2 倍。而石英晶体C0 可以看成两个容值 2 倍于 C0 的电容的串联,且中点近似于虚地。于是,图(三)的电路在交流信号上可以等效于图(五)所示电路:0 e* b% l5 C) f; X0 @6 n, R; k9 m + K" D6 O. B3 ?6 F' C8 l8 b

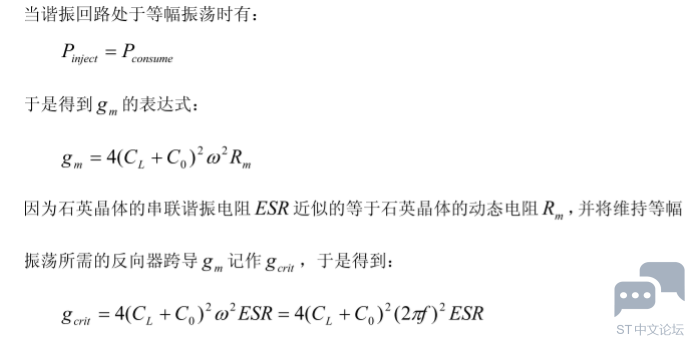

从能量角度看,若要使该电路稳定的振荡,即等幅振荡,需要电源向谐振回路注入能量的功率 Pinject等于谐振回路消耗能量的功率 Pconsume。下面就以此为出发点,计算出振荡器的振荡条件。为了计算方便,选取使电压信号 Vin的初相角为零的相角参考点。# Z! W. ]" S2 h0 d" J6 | 首先,对一些中间变量计算如下: 4 ~0 m4 Y9 ]. j( d, A9 E3 l& d

: T% I: _/ }( J4 O1 M 通常,为了振荡器能够顺利的起振,要求所选取的反向器跨导 gm 是 gcrit的 5 倍以上。这就是判定该石英晶体荡振器在设计参数上是否合理的依据。受电源电压的限制,Vpower 的幅值不会无限的增大,而是存在一个最大值,记该最大值为 Vmax power。于是,有如下不等式成立:

6 ]' d% n* J# `! `. b/ a 于是有: ![761U4S4BN`OL}}8{B]BX)LJ.png 761U4S4BN`OL}}8{B]BX)LJ.png](data/attachment/forum/202202/27/155024jfnfb7ajvxlelfl2.png)

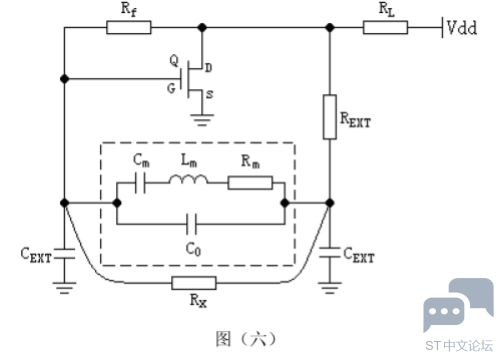

" r m* x7 c- U3 D* W: C$ X. w! I 由此可见,Vin 的大小受到 Rext 取值的限制,而 Vout 的虚部为常数,实部为−Vin,所以 Vout 的幅值也受到Rext取值的限制。因而,通过调整 Rext的取值,即可限定振荡器振荡的功率。: F+ r' ~/ m# n3 V+ p 当由于某种原因导制 PCB 上发生漏电时,在石英晶体的两个端子之间会有寄生通路存在,用 Rx 来表示,如图(六)所示:0 g" J4 o4 P4 g- D% D

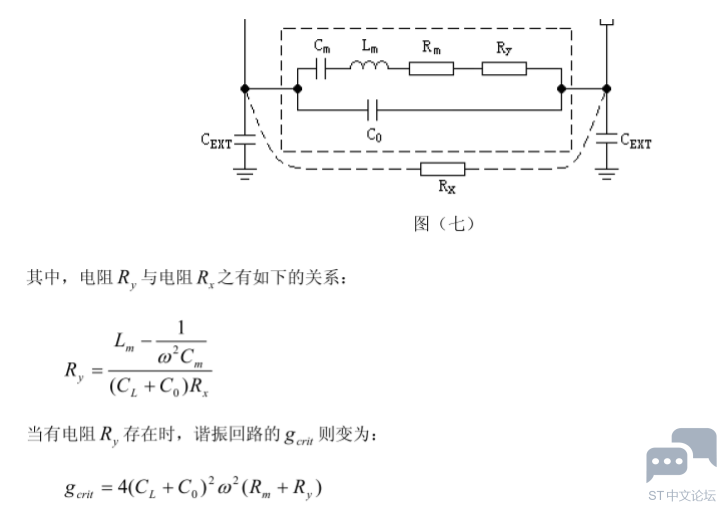

由于石英晶体和两个 Cext构成的是一个并联谐振回路,所以电阻 Rx可以折合成一个与 Rm串联的电阻 Ry,如图(七)所示:6 z! x4 ~$ W8 {

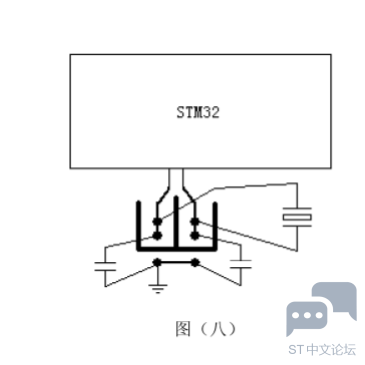

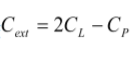

0 X$ v2 U% L L% [- G 可见,谐振回路的 gcrit 在有 Ry 存在时增大了。由于 Ry 与 Rx 存在反比关系,从而较小 Rx 会引入较大的Ry,进而使得谐振回路的 gcrit 获得更大的增加。当谐振回路的 gcrit 超过反向器的 gm 时,振荡器则不能维持原来的振荡,从而导致停振。 从以上分析可知,要避免振荡器停振主要从以下几方面入手: 1. 合理的选择石英晶体,以保证振荡器有足够高的增益裕量,使得 ; 2. 在选取反馈电容 Cext 的容值的时候,要考虑反向器引脚寄生电容 CP 的影响,应按来取值;& \0 J1 u# i Q" `' S5 p- ^ 3. 通过合理的布线来减小 PCB 上漏电流。组成振荡器的元件要集中在一起,尽量缩短走线长度而拉大线间的距离。图(八)所示的“山”形切槽对减小 PCB 上漏电漏会有一定的帮助;0 v4 P. g7 G1 @ 4. 采取覆盖措施,使振荡电路与外界环境隔离,以避免水份及杂质引起的漏电流。实践证明,硅象胶和防水胶是效果比好的材料;' o6 I. f: g3 X* u5 n * g0 s8 g0 |' |5 @) |9 a! z w( f

|

![[W6B%HLVZTY{0(U]2LKX7ZK.png [W6B%HLVZTY{0(U]2LKX7ZK.png](data/attachment/forum/202202/27/155024k29nb4uusz2n5u9z.png)

【2025·STM32峰会】GUI解决方案实训分享2-编译运行TouchGFX咖啡机例程(含桌面仿真)

实战经验 | Keil工程使用NEAI库的异常问题

STM32 ISP IQTune:真正零门槛的免费ISP调整软件

【经验分享】STM32 新建基于STM32F40x 固件库的MDK5 工程

意法半导体MCU双供应链策略,打消中国客户后顾之忧

【经验分享】基于STM32使用HAL库实现USB组合设备CDC+MSC

2024意法半导体工业峰会:赋能智能电源和智能工业,构筑可持续未来

ST推出灵活、面向未来的智能电表通信解决方案,助力能源转型

意法半导体 x Qu-Bit Electronix:推动新一轮的数字声音合成革命

从STM32 MPU产品看嵌入式系统中微处理器的新变化

微信公众号

微信公众号

手机版

手机版