|

请教一个问题,PLL_RDY与那个信号或者寄存器是关联的,PLL_RDY信号只与PLL_ON状态有关吗? |

在 STM32CubeIDE 中正确设置 STM32F103C8T6 的 Flash 容量

咨询下,新项目打算用STM32F103的USB与工控机或PAD进行通讯,问题如下

STM32F103 串口下载ST Flash Loader Demo

请问一下STM32F103C8T6的Hardwar NSS Output ENABLE后cs持续拉低是为什么

foc2.0函数SVPWM_3ShuntCalcDutyCycles看不明白

F103的IIC支持高速400K频率吗?

STM32F103RCT6断电以后,ADC会漏电

无源晶振开关电路设计

要在STM32F103C8T6上实现TIM+DMA+ADC采集电压,cubemx配置为什么,代码怎么写

PCF8563(RTC)读取时间有误

微信公众号

微信公众号

手机版

手机版

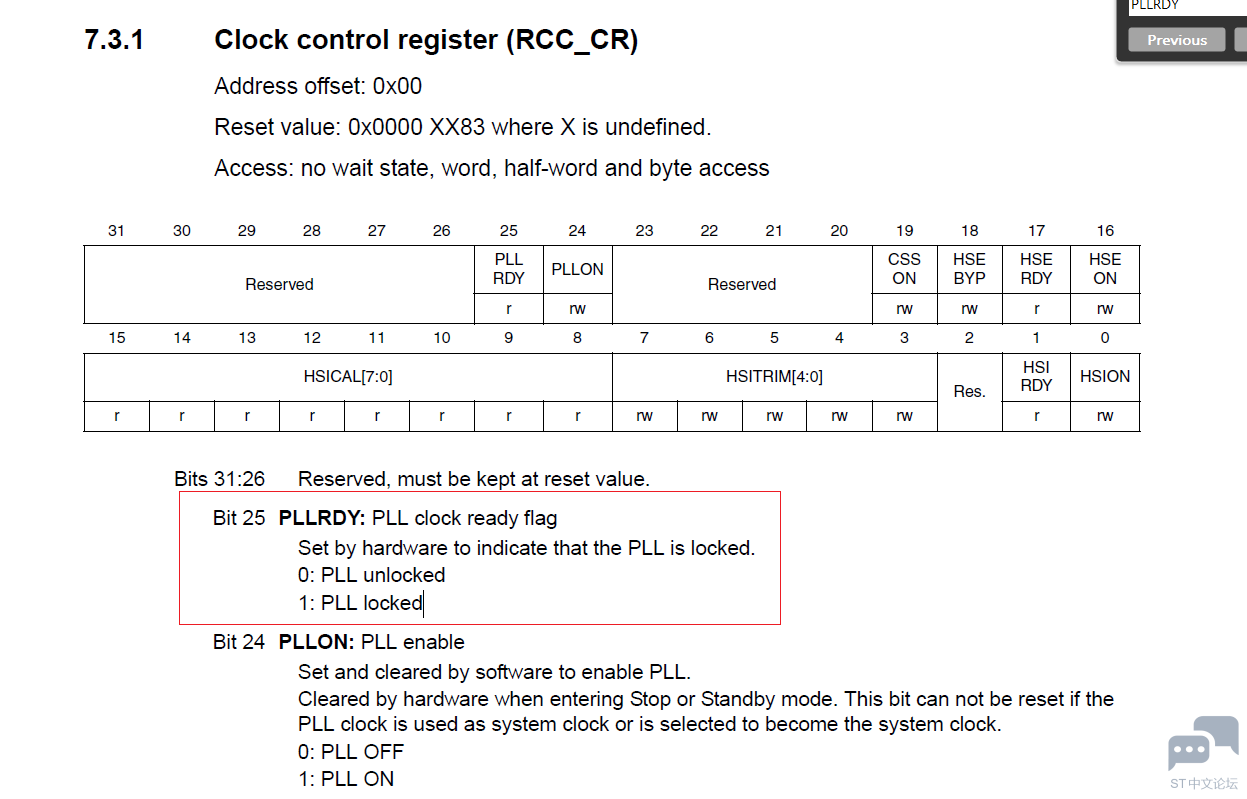

[md]这个地方我测试的结果是,PLL关闭后RDY位才会被硬件自动清零。如果说只是半途断掉其时钟源,该位似乎还是保持原来就绪状态。 当然,对于PLL的修改,我们一定是先关闭PLL然后修改才会生效。

谢谢回答, VDDA电源稳定,时钟源HSE或者HSI。我想了解一下PLL-RDY信号检测的逻辑,是PLL信号消失后RDY信号也会消失,还是说输入源的信号消失才会出现RDY信号检测不到,此时PLL_RDY被置低

产品手册上说这个标志是表明锁相环已经锁定的标志,由硬件置位。也就是说锁相环时钟已经就绪了,可以使用了。对应用层来说足够了。

至于如何检测和设定的,这个是电路(微电子)设计的内容,一般来说对用户不会详细描述的。