.png) STMCU小助手

发布时间:2022-7-6 14:00

STMCU小助手

发布时间:2022-7-6 14:00

|

一、GPIO介绍 GPIO:General Purpose Input Output通用用途输入输出 核心功能:输入、输出和高级外设的复用功能

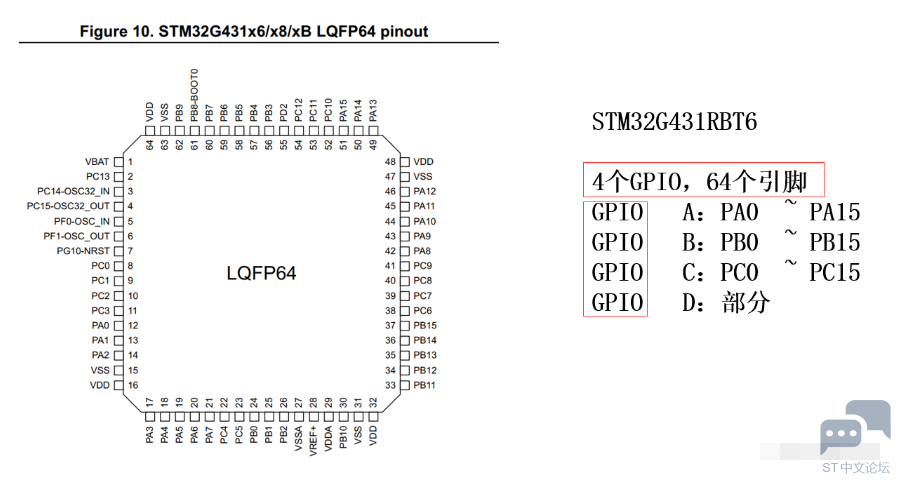

注:使用时一定要配置好各引脚是用作普通I/O(输出0和1)还是用作复用功能 STM32G431数据手册:查看STM32G4引脚复用功能 ![})PW4(YGEVR52A0R)YT%N]D.png })PW4(YGEVR52A0R)YT%N]D.png](data/attachment/forum/202207/06/141008ponfzq8xmllsmwqs.png)

查看对应引脚对应的复用功能:

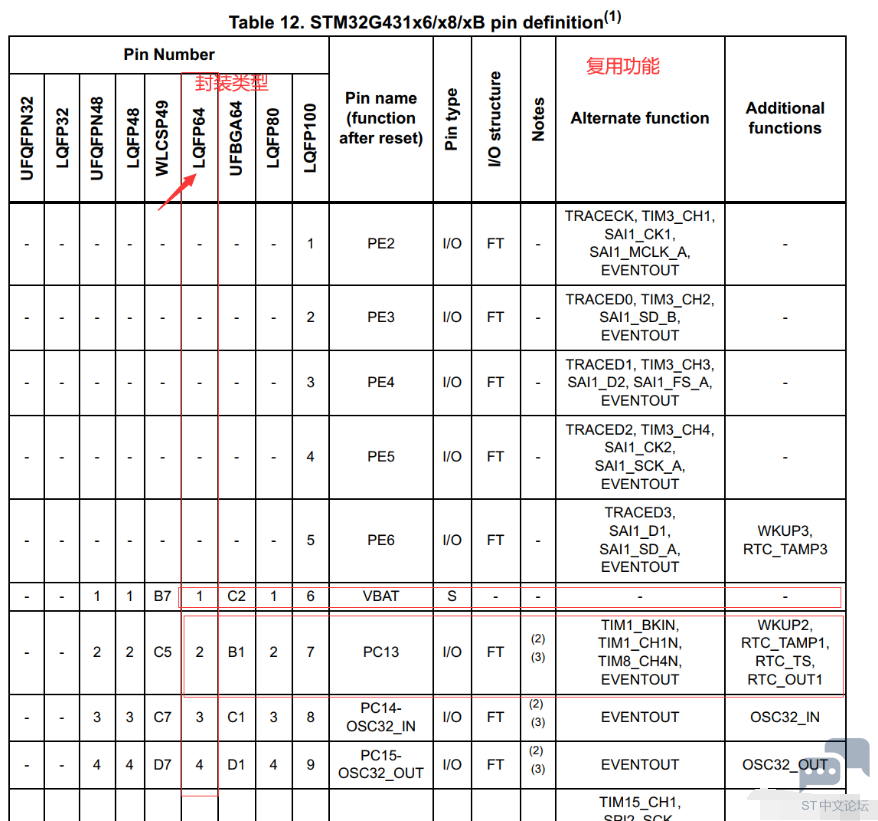

封装LQFP64 前5行 “ - ” 表示 “ 无 ” ,第1引脚从第6行开始 既然有多种复用功能选择,如何指定一种相应的复用功能? ==控制复用功能的选择某个引脚选择第二个功能: == ![FFY7}QFZVAXPZNVP7W9]2{H.png FFY7}QFZVAXPZNVP7W9]2{H.png](data/attachment/forum/202207/06/141008r2krkczojofntcfj.png)

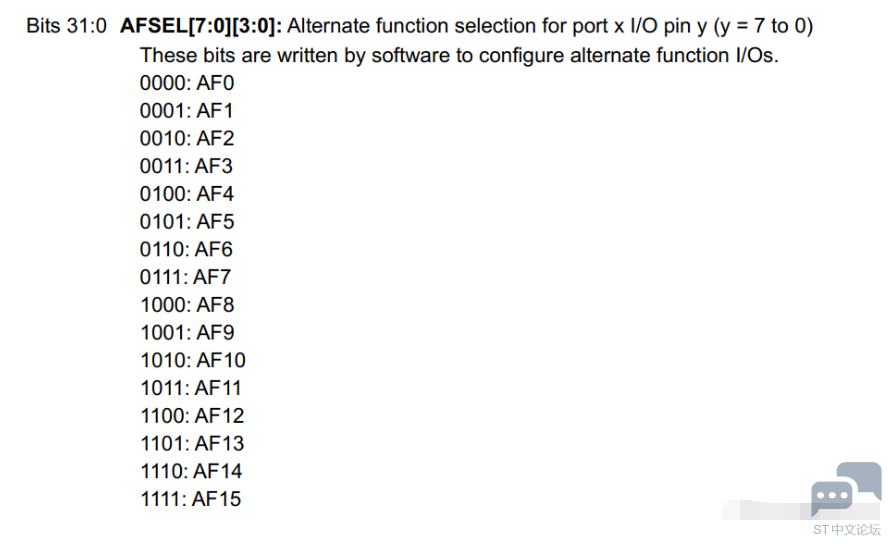

将某一个引脚设置为一种复用功能可根据上图来看,每一行对应着不同的复用功能,将对应引脚设置为AFX对应功能所在列(将PA9设置为串口功能,只要将PA9设置为AF7即可),这里就要用使用到复用功能寄存器 STM32G4系列控制器参考手册:

![[]]L38A65666RW4`TGT$`SO.png []]L38A65666RW4`TGT$`SO.png](data/attachment/forum/202207/06/141009q0qhqxbg2382x8qf.png)

这个是低位寄存器对应PA0-PA7, 还有一个高位寄存器对应PA8-PA15

所以,将PAx引脚设置为AFx引脚只需要像AFRL/AFRH寄存器写入相应的值 将PA9设置为串口功能,只需要将GPIO A_AFRH 写入0111( PA9 对应 GPIO A_AFRH 中的 AFSEL9[3:0] ) 二、GPIO的基本结构 1.IO口内部电路结构

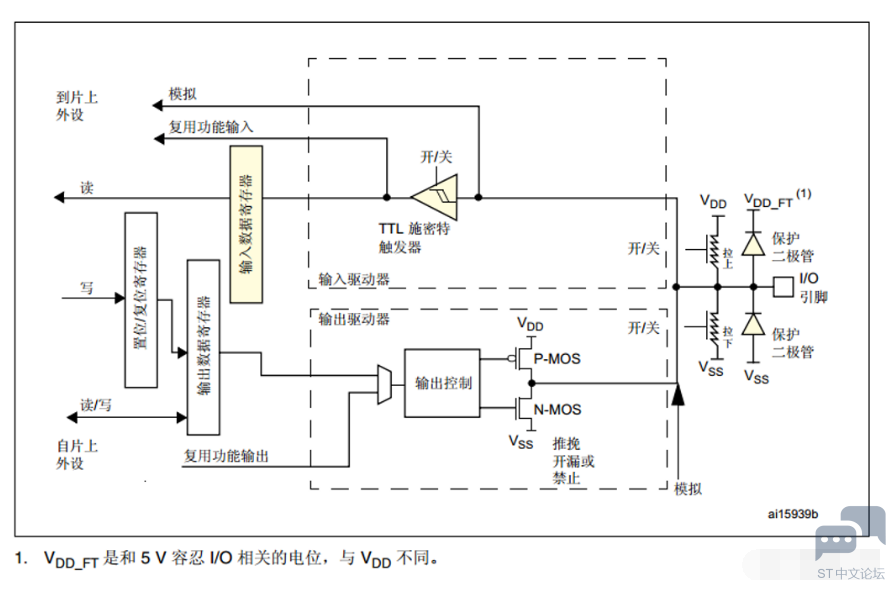

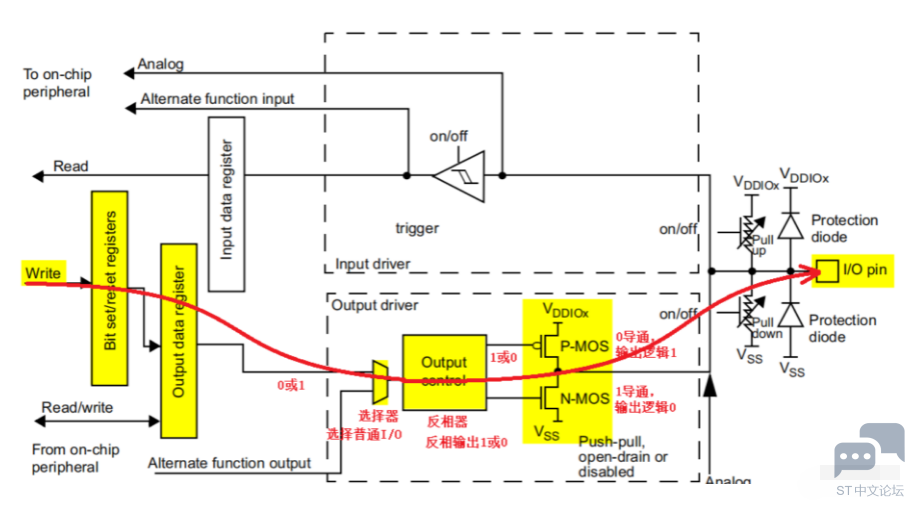

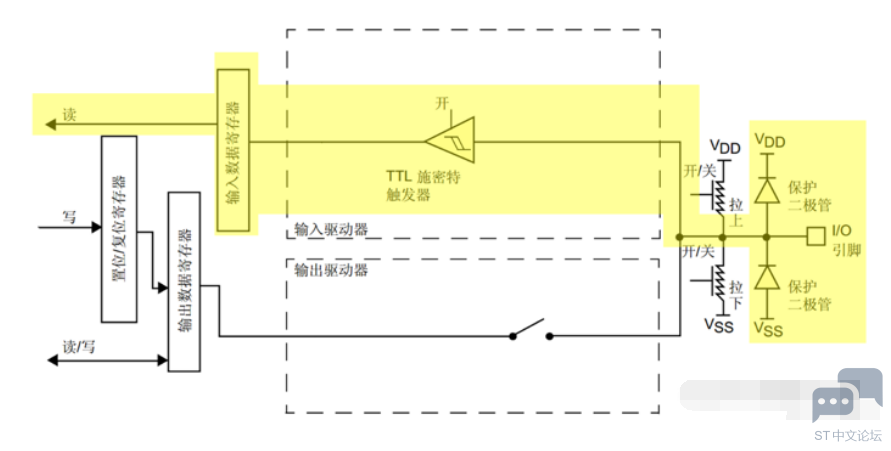

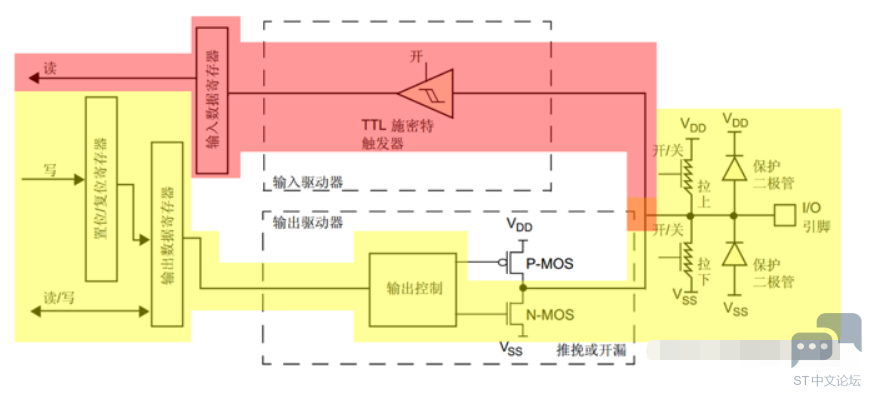

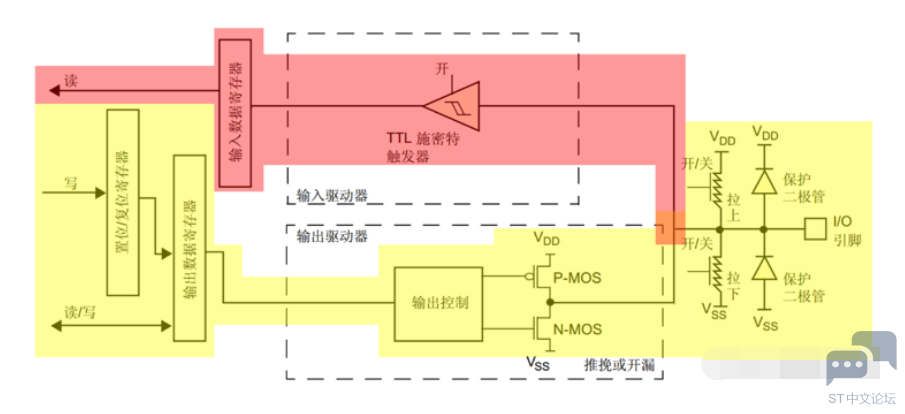

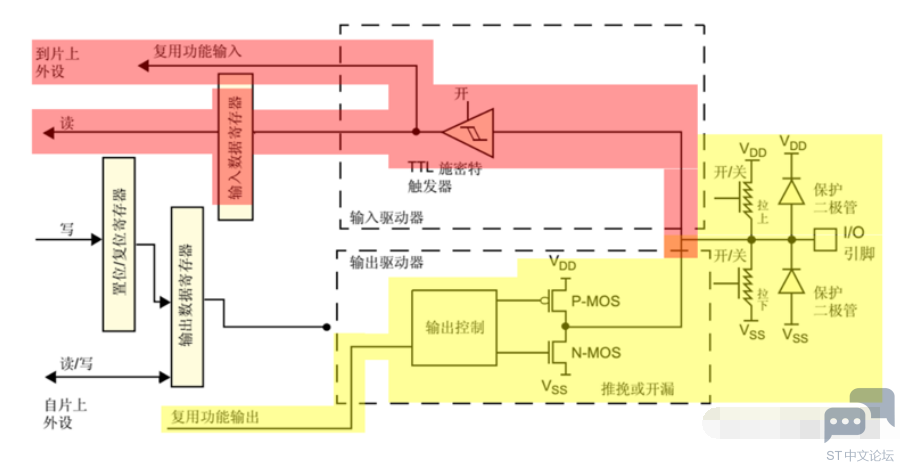

I/O口的基本结构可分为上下两部分,下半部分为输出驱动器 ,上半部分为输入驱动器 2.IO输入输出 1.普通IO输出

(1)通过置位/复位寄存器和 输出数据寄存器的共同作用输出0或1 (2)在选择器处选择普通I/O输出( 或复用功能输出) (3)通过反相器将前面输出的0或1转换为1或0 (4)通过P-MOS管和N-MOS管两个MOS管决定输出逻辑0还是逻辑1 P-MOS管 为低电平导通,导通后输出逻辑1 N-MOS管 为高电平导通,导通后输出逻辑0 2.复用功能功能输出

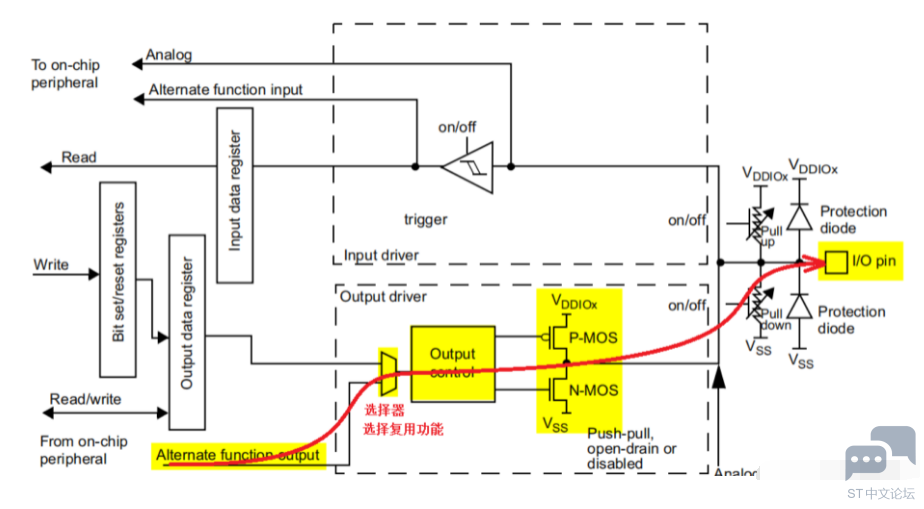

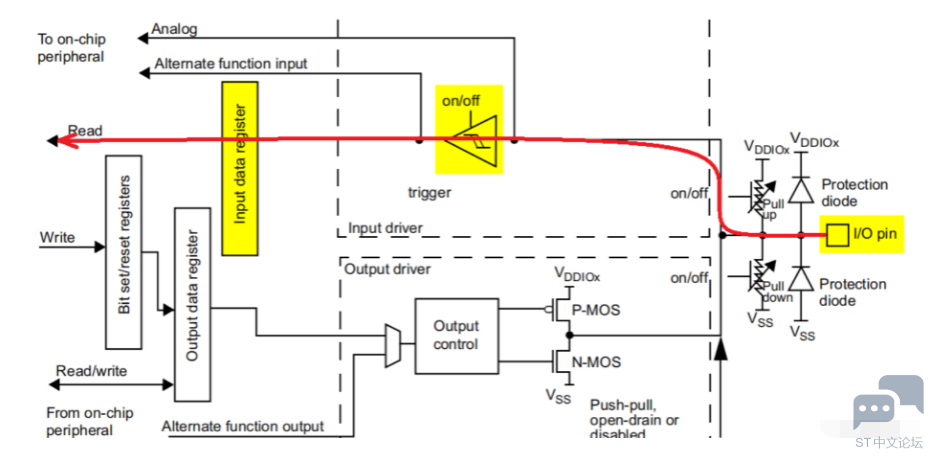

与普通IO输出相比,选择器选择复用功能输出 3.普通IO输入 输入为低电平0时,上下拉电阻处于关闭状态,施密特触发器为打开状态

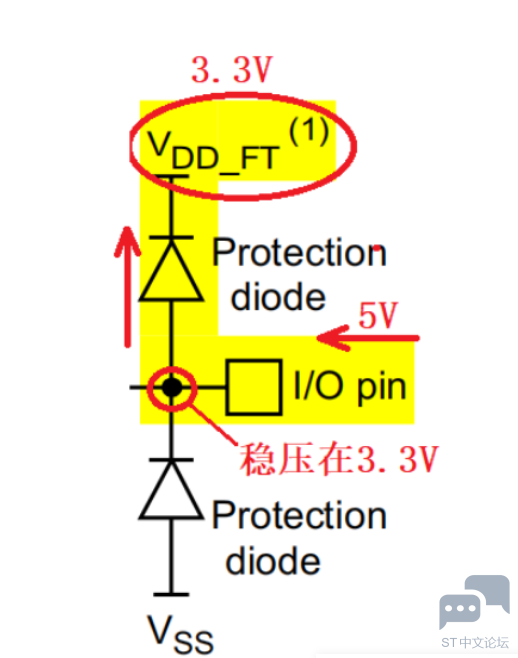

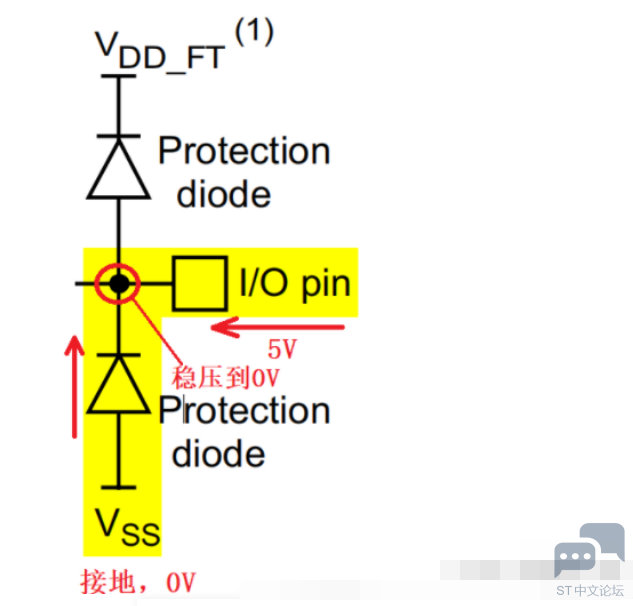

但是,若输入为高电平时要考虑输入电压的大小,如果电压过大必须进行稳压,否则会烧坏电路,这就是包含二极管的作用 (1)输入的高电平为3.3V:能够直接通过I/O引脚进入内部电路 (2)输入的高电平为5V: 要用到 5V容错I/O端口 其中 VDD_FT(3.3V) 当输入为+5V时,上面的二极管导通,连接 VDD_FT(3.3V),将输入的5V稳压到3.3V,从而保护了电路

(3)当输入为-5V时(和5V方向相反),下面二极管导通,连接VSS(0V),将输入的-5V稳压到0V,从而保护电路

上下拉电阻 当某个引脚处于悬空时,其输入电平不能确定,既不是高电平也不是低电平 上拉下拉电阻用于处理IO口不确定的电平状态,强制性的将电平拉上或拉下 注:当输入为确定的高电平或低电平时,上拉下拉电阻将不起作用 上拉和下拉都各有一个开关,当输入电平不确定时且上拉或下拉开关闭合时,不确定的电平就被强制性的转换为高电平(上拉开关闭合)或低电平(下拉开关闭合) 上拉电阻:将上拉开关闭合,输入的不确定电平被强制上拉为高电平 下拉电阻:将下拉开关闭合,输入的不确定电平被强制下拉为低电平 ![YOQUVW0S]8MH49B{)$CZ``B.png YOQUVW0S]8MH49B{)$CZ``B.png](data/attachment/forum/202207/06/141012ukk8vv686ivvmkd8.png)

小结:

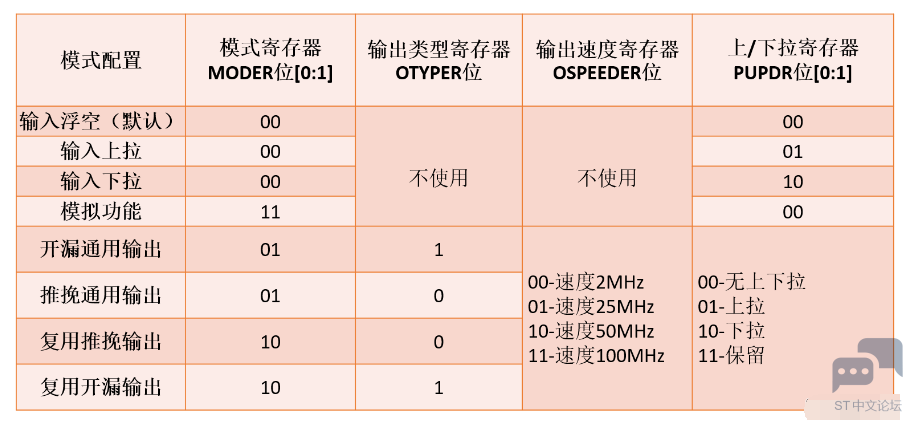

三、GPIO工作模式 为实现不同的工作要求,GPIO有8种工作模式。每个I/O口可以自由编程,但I/O寄存器必须按32位字被访问。

1.浮空输入 浮空输入:复位上电的时,引脚不确定电平的高低(既不接电源,也不接地

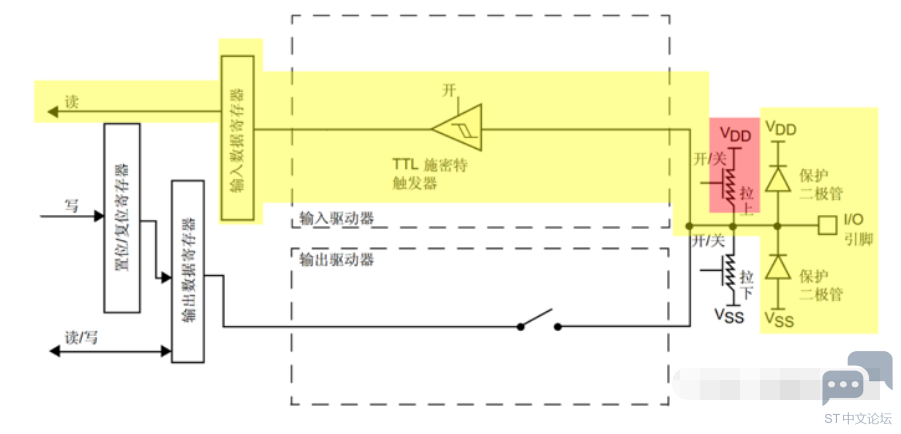

(1)外部通过IO口输入电平(上下拉电阻处于关闭状态) (2)传输到施密特触发器(此时施密特触发器为打开状态) (3)继续传输到输入数据寄存器IDR (4)CPU通过读输入数据寄存器IDR实现读取外部输入电平值 2.输入上拉模式 输入上拉模式:与输入浮空模式相比较,不同之处在于内部有一个上拉电阻连接到 VDD(输入上拉模式下,上拉电阻开关接通,阻值约 30-50K)

外部输入通过上拉电阻,施密特触发器存入输入数据寄存器 IDR,被 CPU 读取,当输入管脚悬空时不受外部噪声信号干扰。 无论输入管脚悬空或者被高电平驱动时,读取的都是1. 只有在输入端为0的时,读取到的值才是0。因此采取的是非0输入模式。即若读取非0,即为1,若读取为0,即为0。强制上拉,一般是为了输入强高电平 3.输入下拉模式 输入下拉模式: 与输入浮空模式相比较,不同之处在于内部有一个下拉电阻连接到 VSS(输入下拉模式下,下拉电阻开关接通,阻值约 30-50K) ![_M(P9B}M9E%HZM2C@Z]$AII.png _M(P9B}M9E%HZM2C@Z]$AII.png](data/attachment/forum/202207/06/141013lrbk23nvqbju3que.png)

外部输入通过下拉电阻,施密特触发器存入输入数据寄存器 IDR,被 CPU 读取,强制下拉,一般是为了输入强低电平 4.模拟输入模式

上拉和下拉部分均为关闭状态,施密特触发器为截止状态,通过模拟输入通道输入到 CPU,IO 口外部电压为模拟量(电压形式非电平形式), 作为模拟输入范围一般为 0~3.3V 将IO口作为模拟输入接口,输入的可能是变化的值,接收外部的模拟信号输入 5.开漏输出模式 开漏输出即三极管的集电极或者MOS管的漏极进行输出 开漏输出可以实现线与功能。开漏输出只能输出强低电平,高电平需要依靠外部上拉电子拉高,适合做电流型驱动,吸收电流能力较强 注: 在输出模式下TTL施密特触发器为开启状态,所以输出模式下仍存在输入

(1)CPU写入位设置/清除寄存器BSRR,映射到输出数据寄存器ODR (2)联通到输出控制电路(也就是ODR的电平) (3)ODR电平通过输出控制电路进入N-MOS管 开漏不使用 P-MOS(输出1) ,故输出不为 “0” 或 “1”,而是 “0” 或 “浮空” (1)写0传输到MOS管处,N-MOS 导通,输出为0 (2)写1传输到MOS管处,P-MOS 和 N-MOS 都不导通,输出浮空 (1)ODR输出0: N-MOS截止,IO端口电平不会由ODR输出决定,而由外部上拉/下拉决定 在输出状态下,输出的电平可以被读取,数据存入输入数据寄存器,由CPU读取,实现CPU读取输出电平 所以,当N-MOS截止时,如果读取到输出电平为1,不一定是我们输出的1,有可能是外部上拉产生的1 (2)ODR输出1: N-MOS开启,IO端口电平被N-MOS管拉倒VSS,使IO输出低电平。此时输出的低电平同样可以被CPU读取到 开漏输出为不确定状态,不具有驱动能力 6.推挽输出模式 推挽输出使用 P-MOS和N-MOS ,输出为0或1

推挽输出可以采取强高/强低输出,可以连接数字电路 7.推挽复用输出模式

与推挽输出模式唯一的区别在于输出控制电路之前电平的来源 推挽输出模式的输出电平是由CPU写入输出数据寄存器控制的,推挽复用输出模式的输出电平是由复用功能外设输出决定的 8.开漏复用输出模式

与开漏输出模式唯一的区别在于输出控制电路之前电平的来源 开漏输出模式的输出电平是由CPU写入输出数据寄存器控制的,开漏复用输出模式的输出电平是由复用功能外设输出决定的 小结: (1)推挽结构:两个参数相同的三极管或MOS管分别受两互补信号的控制,总是在一个三极管或MOS管导通的时候另一个截止。高低电平由输出电平决定 (2)开漏输出:只可以输出强低电平,高电平得靠外部电阻拉高。输出端相当于三极管的集电极。适合于做电流型的驱动,其吸收电流的能力相对强, 由于输出电平完全由上拉电阻连接的电源电平决定,很方便的调节电平转换 可以实现"线与"功能,"线与"指的是多个信号线直接连接在一起,只有当所有信号全部为高电平时,合在一起的总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平 (3)推挽输出:可以输出强高、低电平,都具有驱动能力,可以连接数字器件 四、GPIO寄存器组 STM32G4系列控制器参考手册 : 查看GPIO寄存器 ![S]}D5NI2GRL$A@~UO}0FC%S.png S]}D5NI2GRL$A@~UO}0FC%S.png](data/attachment/forum/202207/06/141015u27c47n4abr2cfbb.png)

每个GPIO包括10个寄存器来配置GPIO的具体功能(每个引脚功能都是完全可以独立配置,互不影响): GPIOx_MODER:GPIO 端口模式寄存器 GPIOx_OTYPER :GPIO 端口输出类型寄存器 GPIOx_OSPEEDR :GPIO 端口输出速度寄存器 GPIOx_PUPDR :GPIO 端口上拉/下拉寄存器 GPIOx_IDR :GPIO 端口输入数据 GPIOx_ODR :GPIO 端口输出数据寄存器 GPIOx_BSRR :GPIO 端口置位/复位寄存器 GPIOx_LCKR :GPIO 端口配置锁定寄存器 GPIOx_AFRL :GPIO 复用功能低位寄存器 GPIOx_AFRH :GPIO 复用功能高位寄存器 GPIOx_BRR:GPIO位复位寄存器 ![)N$%}HJMVIYZNOC~M]C~V.png )N$%}HJMVIYZNOC~M]C~V.png](data/attachment/forum/202207/06/141015q1cgzvhhgghs5uch.png)

|

NUCLEO-G474RE 扩展 LSM6DSO 传感器数据融合实操演示全解析

经验分享 | STM32G474 高精度定时器同步功能全解析 从内部互联到多芯片协同的实现方案

经验分享 | STM32G4双BANK启动应用演示

STM32G4 LPTIM+DMAMUX 实现并行输出应用示例

实战经验 | LAT1578 SAU对NSC分区的影响

经验分享 | STM32G474 HRTIM Triggered-half模式实现两相交错电源180°相位同步方案

STM32大神笔记,超详细单片机学习汇总资料

经验分享 | 为什么重启ADC的DMA传输要先停掉ADC?

实战经验 | 基于STM32G474的三相LLC+SR PWM产出方案

STM32固件库分享,超全系列整理

微信公众号

微信公众号

手机版

手机版