.png) STMCU小助手

发布时间:2022-7-10 12:51

STMCU小助手

发布时间:2022-7-10 12:51

|

引言 STM32U575/585 微控制器(MCU)基于具有 Arm® TrustZone®和 FPU 的高性能 Arm® 32 位 Cortex®‑M33CPU。这些 MCU 采用新型结构制造,得益于其高度灵活性和高级外设集,实现了一流的超低功耗性能。STM32U575/585 器件可为应用实现极高的能效。 带有“Q”后缀的 STM32U575/585 器件(例如 STM32U5xxxxQ)支持在运行和低功耗模式下使用内部 SMPS,从而能够设计出非 常高效的低功耗应用( ~/ B! @1 B" b6 q. t 通过集成 ART 加速器 8 KB 指令缓存,STM32U575/585 MCU 可在高达 160MHz 的频率下运行,实现 240 DMIPS 性能,同时保+ h1 a9 \- n T5 w( J* P. q 持极低的动态功耗。$ ~/ l% q! s9 |% ^; R STM32U575/585 器件嵌入了大量智能高性能外设,具有多种先进的超低功耗模拟功能。借助于 LPBAM(低功耗后台自主模 式),许多外设(包括通信、模拟、定时器和音频)均可正常工作并自主进入停机模式,并直接访问内存。 超低功耗设计和处理性能的组合使这些器件能够达到行业领先的 EEMBC® ULPBench™得分,最高达到 535 ULPMark™。 STM32U575/585 MCU 集合了多种创新,能够使不同模式下的功耗减到最小,同时保留大部分现有外设并很好地实现了引脚兼 容,能够很容易地从现有产品上进行移植。 得益于其内置内部稳压器和电压调节,无论外部供电电压是多少,在活动模式下都能保持尽可能小的消耗。这使得这些器件非常适合电池供电的产品,所需供电电压可低 至 1.71 V。; ?1 a# O- E. [+ b 此外,它们具有多电压域,允许产品以低压供电,同时模数和数模转换器可在高达 3.6V 的高电源电压和参考电压下工作。 STM32U575/585 器件可支持电池备份域以保持 RTC(实时时钟)运行,并能支持 32 个寄存器(每个寄存器为 32 位宽)的组,该寄存器组在失去电源时能够保持内容。该可选备份电池可在有主电源时充电。 这些器件支持多种主要的低功耗模式,其中每种都有多个子模式选项。这使得设计人员可以在低功耗性能、短启动时间、可用外设集与唤醒源最大数量之间实现最佳折中。. ?2 e y/ S. A) n6 v & y4 j* H) t$ m* b9 E% g- w 1.概述; C9 s! F8 M |9 b, ?$ `* B# \9 v 本应用说明适用于基于 Arm® Cortex®内核的 STM32U575/585 微控制器。 提示 " H+ R' D. z O Arm 是 Arm Limited(或其子公司)在美国和/或其他地区的注册商标。: y& |" i* ~/ [% ~3 q0 E# F1 P 1 x( w" e; W: U$ b: a 参考文档& c. T* J( Z9 j' S; |" \ [1] 参考手册:基于 Arm®的 STM32U575xx 和 STM32U585xx 高级 32 位 MCU(RM0456) [2] STM32U575xx(DS13737)和 STM32U585xx(DS13086)的数据表! g% p5 K3 y% U- w [3] 应用笔记用于硬件设置和低功耗的 STM32 微控制器 GPIO 配置(AN4899) [4] 应用笔记使用 LPBAM 进行的 STM32U575/585 功耗优化(AN5645)0 b0 L1 v; a: p1 [8 ? 2.高能效处理 由于使用了关联到其存储器接口的 Cortex‑M33 核,因而在运行模式下获得了很高的处理性能(以 DMIPS/MHz 表 示)。为确保实现最大工作频率下的高性能工作,STM32U575/585 器件嵌入了 ART 加速器指令缓存# }5 R- J! z- u" I2 L# u (ICACHE),通过其屏蔽 Flash 访问等待状态。无论系统时钟频率是多少,都可达到 1.5 DMIPS/MHz 的处理性 能。3 C( M- m, Z& o. d/ L; z STM32U575/585 器件支持动态电压调节,以便优化其在运行模式下的功耗。可根据系统的最高操作频率,调节为 逻辑(VCORE)供电的主稳压器提供的电压。更多详细信息,请参见参考文档[1]。! H" Y+ d' H4 w3 r6 ~ 主调压器在以下范围内运行: • Range 1(V 内核 = 1.2 V),其中 CPU 和外设运行频率高达 160 MHz3 `" t w! `' A) S • Range 2(V 内核 = 1.1 V),其中 CPU 和外设运行频率高达 110 MHz' E# W: Q* B4 l • Range 3(V 内核 = 1.0 V),其中 CPU 和外设运行频率高达 55 MHz • Range 4(V 内核 = 0.9 V),其中 CPU 和外设运行频率高达 25 MHz2 X6 C) H: v1 l5 m9 h 除非另有说明,否则本应用笔记中使用的所有功耗数据均基于从参考文档[2]中提取的 TA = 25 ° C 且 VDD = 3.0 V 时的典型规格。 提示 使用低功耗调压器时,根据软件配置,系统时钟可以是频率高达 24MHz(默认为 4MHz)的 MSIS,也可以是 HSI16。 2.1 内部调压器效率 STM32U575/585 器件嵌入了两个内部调压器,可在应用运行时根据应用要求进行选择:# V( C$ S6 O9 P# U" Z* G- U • SMPS 降压转换器 • 线性调压器(LDO) LDO 和 SMPS 稳压器有两种模式:" Q1 P9 v$ |4 g" G( U • 主调压器(需要性能时使用) • 低功耗调压器 两个调压器都可以提供四个不同电压(电压调节),同时还能在停机模式下工作。 ![)OK{V]WKEO{PM_L`L[1`YO4.png )OK{V]WKEO{PM_L`L[1`YO4.png](data/attachment/forum/202207/10/125435yhxmgs7xslm4xfsl.png)

' K6 V( `& q/ L4 c 下图显示了 STM32U575/585 微控制器在运行模式下用于 SMPS 和 LDO 配置的典型电流消耗(作为系统频率的函 数)。7 k% ^5 C& Q1 r . B7 q# {- D0 u. `

( g3 u7 u4 M" ~9 R: _& l- [ 1 h) v5 `0 M) R' _& Z 提示 8 y3 H# W3 Y3 R4 ^ 从具有单路缓存的内部 Flash 运行时,功耗达到最低。指令缓存往往可减少对存储器的访问次数,从而降低整体 电流消耗。使用 ICACHE 时,内部 SRAM 的电流消耗与 Flash 相似。: J1 j6 g9 u4 o 下图显示了该曲线在 CPU 频率下转化为功率效率(将其除以电流消耗、乘以电源电压得到功率图)。) I1 x! v0 A) q( _# |# o ' a9 z3 f1 [3 N3 s, E8 l2 f3 j1 \

. v$ q E. W/ C% d0 Y 2.2 ICACHE 效率 指令缓存(ICACHE)旨在缓存来自处理器的指令提取或指令存储器负载。ICACHE 只管理读事务,不管理写事 务。在大部分时间,ICACHE 通过从内部 ICACHE 提取指令来降低功耗,而不是从更大且功耗更大的主存储器中获; ~( P) t7 I9 L- h* r! X 取指令。7 q* J9 x+ ^. l ICACHE 的默认配置(复位时)是双路组相联缓存。对于需要极低功耗配置文件的应用,ICACHE 可以配置为单 路,即直接映射缓存。 : e1 J v" g. o& ~# }- X9 a* r- K ![1CO7SZ0PG]OD@~M`L~IG}AQ.png 1CO7SZ0PG]OD@~M`L~IG}AQ.png](data/attachment/forum/202207/10/125605cby8wahhvsbeagzl.png)

提示 预取往往会以额外的 Flash 存取为代价提升代码执行性能。9 h& y" K( }$ j# M

下图显示了 STM32U575/585 微控制器在运行模式下在不同 ICACHE 配置的斐波那契基准中的功率效率(作为系统 频率的函数),其中采用 SMPS 且 VDD = 1.8 V。 0 ?( o i- ^" e: K0 ~8 t; X & h: d2 o/ [4 w0 o( E# w5 O C ![~}GUC]70{ZGQQDUT23DV8ZT.png ~}GUC]70{ZGQQDUT23DV8ZT.png](data/attachment/forum/202207/10/125750wtsks459wbttvtx9.png)

1 I/ R q4 v4 X2 m3 R 2.3Flash 效率, ^9 p4 j6 z) t9 ^! i) I- P 下图显示了 Flash 延迟(要被编程到 Flash 访问控制寄存器中的等待状态数值),具体取决于 STM32U575/585 稳" S! m3 \: o7 ?/ z+ F' Y% d 压器电压调节范围和系统时钟频率。 . L) r$ M% W3 ?. d, U2 H& R ![B7YHV$D`8VQWWQMNP2Q7A]Y.png B7YHV$D`8VQWWQMNP2Q7A]Y.png](data/attachment/forum/202207/10/125818bjgljr0czczzfqbv.png)

Flash 支持低功耗读取模式(LPM)。等待状态(WS)的数量取决于 LPM: • LPM = 0:多达 4 个 WS(取决于电源电压和频率)% C% p9 S3 u! k$ Q0 t& U1 E • LPM=1(降低功耗并增加延迟):高达 15WS(具体取决于电源电压和频率)

% {! x$ ^( n4 l) |' y6 w 3.STM32U575/585 超低功耗特点" G$ q" _* e' q% O 3.1 低功耗模式 STM32U575/585 微控制器实现了多种不同的功耗模式。默认情况下,系统复位或上电复位后,MCU 进入运行模/ z, c' a+ m' a- V+ |; { 式。系统提供了多个低功耗模式,可在 CPU 不需要运行时(例如等待外部事件时)节省功耗。由用户选择具体的' {. w' {/ Z* Q0 h$ H0 F 模式,以在低功耗、短启动时间和可用唤醒源之间寻求最佳平衡。如需更详细信息,请参考[1]。 ( C% p1 n# E' p& \ 3.1.1 睡眠模式 CPU 时钟关闭,包括 Cortex-M33 内核(例如 NVIC、SysTick 等)在内的所有外设都可以运行,并在发生中断或' r- t! t. p$ }1 n8 T+ i 事件时唤醒 CPU。 3.1.2 停机模式6 [2 O$ J% E& m" T' \" D 停机模式基于 Cortex-M33 深度睡眠模式与外设时钟门控的组合。核心域中的所有时钟均停止。禁用 PLL、MSIS、 MSIK、HSI16 和 HSE 振荡器,如果外设请求,则可以在停机 0、停机 1、或停机 2 模式下启用 MSIS、MSIK、 HSI16。6 a* M- K0 f- a# G 停机 0 和停机 1 提供最大数量的活动外设和唤醒源,相比停机 2,其唤醒时间更短,但功耗较高。在停机 2 和停机3 d H' w; j# a; Q9 A 3 模式下,核心域的大部分处于低漏电模式。 在从停机模式退出时,系统时钟可以是 MSIS(最高 24 MHz)或 HSI16,具体取决于软件配置。0 {6 A! t2 G* x; h- P8 `! h 低功耗后台自主模式(LPBAM)0 `- R2 c0 N- J! O, V* G7 v 一些外设是自主的,可以在需要时通过请求其内核时钟(最高 24MHz 的 MSIK,或 HSI16)及其总线(APB 或$ [+ w8 _. T3 `$ Z AHB)而在停机 0、停机 1、或停机 2 模式下运行,以便与 DMA(GPDMA1 或 LPDMA1,取决于外设和功耗模+ X; ^- [! ^) O- @ 式)传输数据。 : e/ ~3 [+ X& x1 D3 {: h/ M& i0 q 3.1.3 待机模式* G# g5 [0 E* u" }4 q 待机模式实现在保留欠压复位功能时的最低功耗:关闭内部调压器,从而关闭核心域。PLL、MSI(MSIS 和5 U# r/ r) M$ J9 {3 P0 w. t* | MSIK)RC、HSI16 RC 和 HSE 晶振也会关闭。RTC 可保持激活状态。可选择保留 8、56 或 64 KB 的 SRAM2。6 q0 O0 c9 N2 U) ]% M; K; I 可以施加内部上拉或下拉来保持 I/O 电平。! S! c: F+ M* S 唤醒后的系统时钟为 MSIS,最高 4MHz。5 u; D% _6 ^; ?6 h 3.1.4 关断模式" E1 t5 r0 I! c$ d; v 关断模式下功耗达到最低。该模式基于深度睡眠模式,其中调压器被禁用。因此核心域断电。通过关闭内部稳压7 F9 [1 d Q( j8 x" z 器,以及禁用耗电监控,该模式可实现最低电流消耗。借助某一个(共五个)唤醒引脚或复位引脚,能够从该模式. u W* l$ O) n! N! h0 b 唤醒。由低速外部振荡器(LSE)定时的 RTC 在此模式下也是起作用的,具有唤醒功能。. z3 I9 N9 {+ x9 d8 ~ 文档[1]的“功耗模式”部分中的“低功耗模式总结”表总结了每种模式的可用特性,并提供了电流消耗的指示。% M( \4 ]' u' A+ c# a% h, c 3.2 功耗优化 3.2.1 ICACHE 处于运行模式% T" \7 A( B0 ?, v$ W ICACHE 通过从内部 ICACHE 获取指令来降低功耗。在大多数情况下,采用较低性能配置文件和严格的低功耗限制 的应用程序可能会从配置为直接映射(ICACHE_1-way)的 ICACHE 的较低功耗而受益。 这种单路高速缓存配置是通过在 ICACHE_CR 中编程 WAYSEL=0 实现的。 $ F3 y/ Z9 b4 g9 _ ) n1 G: |/ W" U# i 3.2.2 运行和睡眠模式下的 Flash STM32U575/585 Flash 包括主存储器块,该主存储器块由两个 1 MB 的存储区(bank)组成,每个 bank 包含 128) D& H( s' o8 u& f8 W- R; B8 ]. j. V 个 8 KB 的页面。当 MCU 处于运行和睡眠模式时,这一结构在专用模式下的功耗方面得到了优化。+ L9 B, q5 r, Z+ k) M' R 为了降低运行和睡眠模式下的功耗,可以根据所使用的存储区,通过设置 FLASH_ACR 中的 PDREQ1 或 PDREQ2 独立地将每个存储区置于掉电模式。/ U: G% G; M. R& F# c5 `! G/ k9 G Flash 支持低功耗读取模式,通过在 FLASH_ACR 中编程 LPM=1 来降低功耗。$ M9 b; K( D9 F$ G $ T V k, l) s0 c8 I6 W2 R/ W 提示 预取往往会以额外的 Flash 存取为代价提升代码执行性能。然而,对于大多数应用程序,预取开启时的电源效率) ]! H8 o v, b; Y 会更好。 f; `$ \/ E; `: l# u6 ~ 3.2.3 电源控制优化& G. m4 o9 ?: D6 b: f 在待机模式下,可以将 BOR 配置为不连续模式(超低功耗模式),通过将 PWR_CR 中的 ULPMEN 位设置为 1 来: \9 d. S" H7 J5 ] 进一步降低电流消耗。- _/ f( p( K6 m% L 为降低运行、睡眠或任何低功耗模式下的功耗,建议从 LDO 切换到 SMPS。6 w& v+ l& ~; r, I: X j 提示 • SMPS 电源引脚仅在具有 SMPS 降压转换器选项的特定封装上可用。4 Q8 o: a! o* y# e7 k- W7 m • 可以动态完成 SMPS 到 LDO 和 LDO 到 SMPS 的切换。# _7 \; v. D# K* W( C4 W7 E 3.2.4 低功耗模式下的 RCC 为了维持输出时钟精度,MSI 偏置默认为连续模式。当调压器处于 Range 4 中并且设备处于停机 1 或停机 2 模式 时,在进入低功耗模式之前在 RCC_ICSCR1 中设置 MSIBIAS 可降低 MSI 功耗。 在进入低功耗模式之前,建议选择 HSI16 或 MSIS(16 或 24MHz)作为唤醒源,以缩短唤醒时间,并减少唤醒期1 \- }4 r. K( \3 t7 T e 间损失的能量。若使用 24 MHz,则须为 SRAM 读访问配置一个等待 状态延迟,这会影响代码执行性能。然后须在3 O1 b8 V0 g$ F! T5 e 1 个 SRAM 等待状态下使用 24 MHz 和使用 16 MHz 作为系统时钟之间对该性能进行评估。 提示 停机模式期间或从停机模式唤醒时的 MSIS 频率与进入停机模式之前频率相同。如果使用 MSIS 在运行模式下馈 送 PLL,则由于 PLL 输入时钟频率限制使 MSIS 在 4 MHz 到 16 MHz 之间。此时建议关闭 PLL 并在进入停机模% a$ o1 R3 J; K/ l! _. T 式之前将 MSIS 配置为高频(如果使用 MSIS 作为唤醒时钟)。- l9 P& S- ~! m! z% g( n1 B 必须通过清零外设自身的使能位来禁用无法在停机 2 模式下使能的所有外设,或者通过配置 RCC 寄存器 使其处于 复位状态。4 `) C1 `* P' @7 x( Z. | 对于每个时钟源来说,在未使用时都可单独开启或者关闭,以降低功耗。' @, m; T {# N5 B / D& h1 Q8 M2 E 3.2.5 低功耗模式下的 I/O 状态 如需更详细信息,请参考[3]。 7 m: \" |# H* K$ F3 {% J; X' r 配置未使用的 GPIO GPIO 始终有一个输入通道,可以是数字或模拟通道。如果不需要读取 GPIO 数据,则优先配置为模拟输入。这节% E) ~3 M' k. U: Z( ? 省了输入施密特触发器的消耗。& b& L& |! N& Q 禁用 GPIO 寄存器时钟 如果某个 GPIO 组长时间不需要使用,请使用 HAL_RCC_GPIOx_CLK_DISABLE()函数禁用其时钟。 进入低功耗模式时配置 GPIO. Z3 f/ E: y# o 在睡眠、停机 0、停机 1 或停机 2 模式下,所有 I/O 引脚保持与运行模式中相同的状态。对于输出,根据外部组件. J7 {) k7 O( | 所需的电平驱动合适的电平。3 L, ?9 U/ F/ P2 ^" j& M7 g3 q# ^$ P 在停机 3、待机或关断模式下,I/O 默认处于浮动状态。根据外部组件所需的电平施加上拉或下拉。应认识到,在退 出关断模式时不会施加该上拉/下拉,直到固件配置 GPIO 为止。 a/ h1 O5 g0 w, h1 [ 提示 在一些应用中,为了进一步降低停机模式下的功耗,并为了获得更高的电阻值精度,建议使用外部上拉而不是内7 H W. r- g& j) c: d 部上拉。 m& Z2 J. T2 ^* r( j) s- |" U 3.2.6 内部 SRAM STM32U575/585 器件嵌入了五个 SRAM,每个都具有特定的功能:SRAM1、SRAM2、SRAM3 为主 SRAM。 SRAM4 在 SRAM 中用于停机 2 模式下的外设低功耗后台自主模式(LPBAM)。 保留所有 SRAM 和寄存器内容,但 SRAM 可全部或部分关闭,以便进一步降低功耗。这些 SRAM 由多个可以关闭 的块组成:) D# _4 _ C; ` • 运行模式 要降低运行模式下的功耗,应通过在 PWR_CR1 中编程 SRAMxPD 来关闭所有 SRAM。 " t I& ?. z1 G) V% X • 停机模式9 f* A! y( `! I1 G' @5 K 该模式可实现最低功耗,同时保持低功耗调压器供电的 SRAM 和寄存器的内容。停机 3 是具有完全保留的最3 V! z6 p3 S9 |( F% Z) Z 低功耗模式。为了进一步优化功耗,建议如下: – 通过在 PWR_CR2 中编程 SRAMxPDSy = 1 来关闭未使用的 SRAM:( {# `# U+ t9 K7 A. m2 ` ◦ SRAM1, SRAM3, SRAM4 ◦ DCACHE1、DMA2D、FDCAN、FMAC、PKA(如可用)和 USB 的 SRAM% X/ S; @, M7 }; B! x* d4 b – 根据应用数据大小,通过清除 PWR_CR2 中的 SRAMPDS1 和/或 SRAMPDS2 位来保留 SRAM2 第 1# l) f3 V- ]3 S' q1 `$ Y/ S 页和/或第 2 页。 • 待机模式 进入待机模式后,除备份域和待机电路中的寄存器和备份 SRAM(2 KB)外,其余 SRAM 和寄存器的内容都 将丢失。通过在 PWR_CR1 中设置由低功耗调压器供电的 RRSB1 和/或 RRSB2,SRAM2 第 1 页(8 KB)或- E9 q7 H8 }% M. R( i3 T 第 2 页(56 KB)或两页都可以在待机模式保持(在 RAM2 保持模式下待机)。! d A" N" }8 t' k 6 k/ K2 z* q( g 3.2.7 运行和停机模式下的外设时钟门控 STM32U575/585 器件支持关闭 AHB/APB 时钟的功能,以进一步降低功耗。( C* x2 G# J5 [+ P- P 未使用任何 AHB/APB 外设并且其时钟被禁用时,会出现以下情况:$ B1 E! W q/ A9 C; E" ~& E8 o v* P • 当在 RCC_CFGR2 中设置 AHB1DIS = 1 时,AHB1 外设的所有时钟都关闭( BKPSRAM、DCACHE1、0 _" n+ i8 S; A FLASH、ICACHE 和 SRAM1 除外)。 • 当在 RCC_CFGR2 中设置 AHB2DIS = 1 时,来自 RCC_AHB2ENR1 的 AHB2 外设的所有时钟都关闭 (SRAM2 和 SRAM3 除外)。 • 当在 RCC_CFGR3 中设置 AHB3DIS = 1 时,AHB3 外设的所有时钟都关闭(SRAM4 除外)。1 `5 F* }) F6 D • 当在 RCC_CFGR2 中设置 APB1DIS = APB2DIS = 1 且在 RCC_CFGR3 中设置 APB3DIS = 1 时,APB1/2/34 K& Q1 x- Y' J5 e7 ^% K 外设的所有时钟都关闭。 当启用外设时,其时钟可在器件处于休眠模式时通过清除 RCC_AHBxSMENR 和 RCC_APBxSMENR 中的外设 SMEN 位而自动关闭。外设的 EN 位和 SMEN 位均须设置为 1,以便在休眠模式下保持时钟开启。 外设的 SMEN 位还用于根据外设请求在停机 0 和停机 1 模式下允许外设提供时钟。当外设请求时钟时,该时钟将 分配给所有启用的外设。因此,如果在停机模式下未使用外设,则须在进入停机模式之前清除 SMEN 位。4 F/ v& X: l# P8 C% m1 z & O2 ]& z }1 \" c' R8 { Caution: 外设的 SMEN 位必须设置成允许产生能够从停机模式唤醒器件的中断。% D3 e5 |6 `+ q9 \0 l 3.3 使用 LPBAM 优化外设功耗 STM32U575/585 器件支持低功耗后台自主模式(LPBAM),使外设能够在停机 0、停机 1 和停机 2 模式(无任何 软件运行)下工作并保持自主。 由于外设自身的独立时钟(称为内核时钟)请求性能,此功能在停机模式下可用。该内核时钟在有外设请求时自动0 p. \( F8 N3 |9 X$ E" V0 D 打开,并在无外设请求时自动关闭。如需更详细信息,请参考[1]。 3.3.1 支持 LPBAM 的外设2 g. E, p- V! H; s- G- q( C 下表列出了支持 LPBAM 的所有 STM32U575/585 外设。, j& y4 G' p4 ~7 C" E: Z

) X6 Y T" P4 k$ z E9 c3 ] 3.3.2 主要用例3 y' z. v: Y: `) X( t+ y% I 以下是可以留在停机模式下完成的用例示例(有关更多详细信息,请参见文档[4]): • 由低功耗定时器(或任何其他触发器)触发的 ADC 或 DAC 转换 • 音频数字滤波器数据传输到 SRAM 中:检测到声音活动时从停机唤醒- \# L5 ~: H2 {/ z- Q8 U! | • I2C/SPI 从设备传输、UART/LPUART 接收:在外设传输结束时或在 DMA 缓冲区事件时唤醒$ N3 P; p6 G" H' Z4 | ^# }9 Y • 由 LPTIM 触发器触发的(例如传感器周期性读取)I2C/SPI 主设备传输,UART/LPUART 传输:在外设传输 结束时或在 DMA 缓冲区事件时唤醒# e0 Y7 M6 e* q • 外设之间的桥。例如:通信外设传输的 ADC 转换数据 • 从 SRAM 到另一个 SRAM 的数据传输 5 _% n; n# f q 4 低功耗模式选择方法 考虑一个简化的应用模型,其中应用每隔 Tperiod 唤醒一次,始终执行一些相同操作并将指令数视为常数(无等待循 环,无数据依赖)。然后可以进行以下近似计算:0 f0 f. | l, f$ [ • PROCESS 阶段持续时间(Tprocess)可由每个阶段要执行的时钟周期次数(NOC)来定义。将 FCLK 定义为0 L+ X a/ q! c CPU 系统时钟频率,PROCESS 阶段的持续时间等于 TPROCESS = NOC / FCLK。此阶段的平均电流消耗等于+ P, U8 Z s) u' s0 C. m. S Iprocess。8 s& o8 L @# Q2 x* l/ K; w • INACTIVE 阶段的持续时间为 TPERIOD - TPROCESS,其平均电流消耗为 IINACTIVE。 ) v* R$ [) \7 x5 m0 O ![B$`JS_YQ89`[]3P_[KFLO9L.png B$`JS_YQ89`[]3P_[KFLO9L.png](data/attachment/forum/202207/10/130412lrm1zwzyjrgy8zdq.png)

- Y$ {: [1 A: g3 P q0 f 4.1 PROCESS 阶段 C5 R) f. A& O g0 x: O 根据处理要求(DMIPS),可以使用下列不同运行模式中的某一种:9 a s9 q+ i8 _8 M4 a • 具有 Range 1 电压的运行模式,在 160 MHz 运行时最大可达 240 DMIPS: B$ o1 {# s4 k; g • 具有 Range 2 电压的运行模式,在 110 MHz 运行时最大可达 165 DMIPS$ R) U* v6 i& Y2 j9 J! F8 A7 k* L • 具有 Range 3 电压的运行模式,在 55 MHz 运行时最大可达 82.5 DMIPS0 ]# e7 G; i* K, ?) W% ` • 具有 Range 4 电压的运行模式,在 25 MHz 运行时最大可达 37.5 DMIPS 选择频率时另一个需要考虑的参数是支持相关外设约束(如有)的能力。& {! v6 G7 Y! F" S 4 p8 P/ p. A' q$ |# M0 U 4.2 INACTIVE 阶段% `4 v9 Z# l) p3 S. n0 b, w U; u STM32U575/585 期间提供了可用于 INACTIVE 阶段的不同低功耗模式: • 睡眠2 Y1 Z& {( k+ w! V! `5 ~; ?2 K% @ • 停机 0(主调压器开启) • 停机 1(具有低功耗稳压器) • 停机 2(具有低功耗稳压器) • 停机 3(具有低功耗稳压器) • 待机(具有 RTC 和 SRAM2 保留选项) • 关断(使用 RTC 作为选项) 根据唤醒源和睡眠周期持续时间,可选择下述某一种模式: • 睡眠:如果反应性是关键参数(此时唤醒时间仅为 8 个系统时钟周期)5 L; z5 P2 J: J) b$ o" d2 g • 停机 0:当唤醒时间至关重要时(如果程序位于 Flash 中,则<2.5μs) • 停机 1:如果有多个外设需保持唤醒且系统有多种唤醒源(此时应用必须能够容许约 13 μs 的从 Flash 唤醒的7 u; _+ B+ r+ \; B4 ` 时间)! m; U* _& J1 L5 k8 N8 L; C3 ` • 停机 2:如果有少数外设需保持唤醒且能产生唤醒事件,如 DMA 传输完成、LPUART/SPI/I2C 传输事件、通( J8 D. |+ E4 {' g$ E; J2 x$ v9 W* u 过 SDF 语音检测、ADC 模拟看门狗(此时应用须能够容许约 20 µs 的从 Flash 唤醒的时间) • 停机 3:如果除 RTC 之外无其他外设需要在保留所有 SRAM 的情况下保持唤醒,在 FSTEN = 0 时从 Flash( ?- O7 m- H& E, r$ u5 U# d 唤醒的时间为 66.5 µs • 待机:如果除 RTC 之外无其他外设需要保持唤醒,并且需要保留不超过 64 KB 的 SRAM2(此时应用须容许 在 MSIS = 4 MHz 且 FSTEN = 0 时从 Flash 唤醒的时间约为 64.5 μs) • 关断:如果只有 RTC 和备份寄存需要保持唤醒(此时应用须容许在 MSIS = 4 MHz 时约 610 μs 的唤醒时 间)* O; L% t) S. a3 x5 b 提示 唤醒时间取决于代码位置(Flash)、系统时钟源和频率。详细情况请参考[2]。上述从停机唤醒的图形对应于 249 O* k4 i! O, w/ F2 }2 W MHz 或 4 MHz 时的 MSIS 且代码在 Flash 中。为了缩短唤醒时间,建议在 PWR_CR2 中设置 FLASHFWU = 1 且 SRAM4FWU = 1。 4.3 睡眠模式选择 以下数值结果基于从文档[2]中提取的 25°C 时的典型规格值。 针对 RTC 处于 INACTIVE 阶段的不同选择的低功耗模式(睡眠、停机 1 、停机 2、停机 3、具有 RTC 和 SRAM2 保留功能的待机、待机和关断),下图给出了作为主电源(VDD)函数的理论功耗。

$ K* {/ ^6 T7 m/ P! g ![}J]LH38V)PE0D][DUL[X`0F.png }J]LH38V)PE0D][DUL[X`0F.png](data/attachment/forum/202207/10/130558v1nwmwa50daak3np.png)

9 w5 s) u5 P# _, s# x0 Q 前面的图表明,对于需要保留一些数据的应用,待机模式可实现最佳能耗,而停机 3 模式是保留所有 SRAM 的最+ D) @% g# P, [ t8 w$ n- L2 d 低功耗模式。如图 7 所示,使用 SMPS 将能耗降至一半。" c. e: l- q) x7 F |& c 丢弃了关机模式(虚线),因为该模式无法为此类应用提供足够的数据保持能力。+ m5 T- ?* I, r) X7 _+ ]$ g 低功耗模式选择不只是由总体功耗决定的,还与连接到该应用的其他唤醒考虑有关。 图 6 而且图 7 表明,相比于 待机,以少量额外功耗为代价,停机 2 和停机 3 模式针对唤醒的设置更加强大、简单和快速(无需外设重新初始 化) - G$ I# w/ n$ `$ Y% N 4.4 低功耗模式选择 对于实际应用,根据唤醒周期,可使用下面的准则: • 如果唤醒周期长于几十 ms,则使用待机模式实现,可具有更好的功耗性能。( T/ r( Q+ ~7 _6 {: P: _ • 如果唤醒周期较短,则使用停机 2 或停机 3 模式实施效果则更好。8 ~# C" B8 A1 j D$ h8 ? • 如果温度较高,则最好使用待机模式。7 l8 C2 m r# g) I# F; y 低功耗模式选择不仅依赖于功耗,还与唤醒时间要求(系统反应性)和数据保持要求有关。 如果处理可适应低于 24 MHz 的频率,则最优点如下: • 待机或停机 3 模式 在待机模式下,最佳点是唤醒转换时间长于 66μs、保留区低于 64KB SRAM + 2KB BKPSRAM。在停机 3 模 式下,可以保留所有 SRAM。 : D" M7 \* W% u5 A: X • 停机 2 模式+ ~( w$ E" T7 p5 R/ Y( I7 h 最佳点是唤醒转换时间长于 20μs 并且保留区大于 66KB (64KB SRAM2 + 2KB BKPSRAM)保留。8 N6 [6 v" X0 p 如果唤醒周期长于几秒且无需保留内存,则关机模式下会有最好的功耗性能。这种情况下唤醒时间典型值为 610( K& F2 k0 w+ ?5 M- R4 G µs。 ) h% m' r+ W; h* ^ 4.5 转换的影响: x+ j3 ?/ N4 e3 H) \* a 为了完成这项研究,必须考虑在转换阶段(唤醒和停用)消耗的能量。 根据文档[2],在 VDD=3.0V 时,使用 SMPS,离开低功耗模式时所消耗的能量大致为: • 1.1 nAs,对于从停机 1 到运行模式的转换(MSI = 24 MHz) • 0.57 nAs,对于从停机 2 到运行模式的转换(MSI = 24 MHz)9 B% [1 O7 n# V, g1 L) Z D3 h: O • 4.54 nAs,对于从停机 3 到运行模式的转换(MSI = 24 MHz) • 21.22 nAs,对于从待机到运行模式的转换(MSI = 4 MHz) • 457.29 nAs,对于从关断到运行模式的转换(MSI = 4 MHz)+ Y) O' i6 Z! P. F6 O$ D " r' Q% v2 U$ H! L+ V4 U6 G 5 ULPMark-CP 用例优化 5.1 ULPMark-CP 描述 ULPMark-内核配置文件(CP)基准侧重于 MCU 内核,特别是睡眠中的能源成本,以及与激活模式之间的转换。 该基准使用一组可在 8 位、16 位和 32 位微控制器之间移植的通用工作负载。内核配置文件以 1 秒的占空比运行,$ l/ \9 `# f- Q1 H/ Q$ M0 v 将这些工作负载与延长的不活动时间相结合,从而启用微控制器低功耗模式。 在测试的激活部分,基准测试执行以下操作:0 q" M5 ~9 P1 C- V. ?) p8 r • 生成 20 个 GPIO 脉冲。 • 执行 8 位线性插值。" K3 W0 U4 B+ d7 c! y3 z8 y, Y) w4 z • 执行 16 位积分(过滤器)。& h) E' T. U* X& \; L3 G • 计算 7 段 LCD 二进制转换(保存状态)。 • 在字符串中搜索子字符串。 • 执行小型冒泡排序。! _; \/ d) Y9 L5 W • 根据输入和先前状态置换字符串的位。2 n6 @3 H9 r: b 下图显示了 ULPMark-CP 基准在长时间睡眠中运行,随后短暂唤醒以执行最少的处理,模拟睡眠边缘节点来节省能 源(更多详细信息,请参见[5])。6 \8 Z c+ A1 [* w& w& _; I ![}ZG]@XOKLT8PQ)`1~)_D)VV.png }ZG]@XOKLT8PQ)`1~)_D)VV.png](data/attachment/forum/202207/10/130706ehx0i4pbagmge7mx.png)

8 {! o7 s, N: k; e* y9 b) x 5.2 应用约束条件 ULPMark-CP 规定了下列约束条件: • 该应用每秒唤醒一次,基于精确 RTC 在一组数据上执行某些操作。9 p5 J& s+ u s! W9 f, r* v# d+ ` • 从一个处理周期到下一个处理周期时,数据需要保持。这要求在 INACTIVE 阶段中能够保持数据。 • 利用编译器最强优化选项进行编译时,应用所需的处理周期数约为每秒 10000 周期。0 u' {- G3 P3 b5 }' s. n. t, w# e 对于系统反应性不作特别约束,以便服务外部事件或 RTC 周期中断。: v; T/ A: A2 a 5.3 PROCESS 阶段优化 基准测试的激活部分仅运行总运行时间的约 3%,因此用户可以使用内部 MSIS,使用对应于 16 MHz 电压调节范围 4 的功率最佳点。在 16 MHz 标称频率下使用 MSIS 时,其功耗低于使用 PLL 的任何其他解决方案。 为了进一步优化激活阶段的功耗,可以应用以下步骤: 1. 在运行模式下关闭 SRAM1、SRAM2、SRAM3、SRAM4。+ b; j d- e2 Y W! n5 f+ G4 m6 \ 2. 将系统时钟配置为 16 MHZ 的 MSIS 电压调节范围 4。 3. 将数据置于 BKPSRAM。 4. 禁用未使用的 AHB/APB 时钟。) m5 q) ^2 ]/ X% |3 o 5. 将所有 GPIO 引脚置于模拟模式。* c2 P' T x* E2 a$ \ 6. 关闭 Flash 存储区 2。! ^/ u+ W) L! l. I2 z 7. 用 Flash 低功耗模式。 8. 配置编译器优化(高速,无大小限制)。 下图显示了处于激活阶段的 ULPMark-CP。从唤醒到进入低‑功耗模式大约需要 156µs,在 16 MHz 系统时钟 MSIS 的运行模式下消耗 550 µA 电流。9 X+ o! N' x0 s* g; W+ l" z ![U]_B[SVGF~}ED~S5BW6A)CP.png U]_B[SVGF~}ED~S5BW6A)CP.png](data/attachment/forum/202207/10/130816g25ipuzixu5lf353.png)

5.4 INACTIVE 阶段优化% E: t1 O" }3 Q& k2 E7 Y ULPBench-CP 基准要求从一次运行到下一次运行时能够在低功耗模式下保持数据变量无变化。因此,不可使用关! v, u) r! f) F" q1 T' R' {, j) Q 机模式,因为该模式无法为该应用提供足够的数据保持能力。0 `9 r4 K: h- {$ n& X 停机 3 模式可在保留 8 KB SRAM2 或 2 KB BKPSRAM 以及最短唤醒时间的条件下使用。然而,最节能的解决方案- m, C; b; S! C' K" G 是使用待机模式并且具有 RTC 和 8 KB SRAM2 或 2 KB BKPSRAM 数据保持。 为了进一步优化 INACTIVE 阶段的功耗,可以应用以下步骤: 1. 启用 SMPS 调压器。: y; B+ M+ n5 X) T+ _6 I! ` 2. 启用 ULPMEN 位。 3. 在停机 3 模式下关闭未使用的 SRAM。, L7 A9 [8 P; c: m 4. 禁用 AHB/APB 外设的所有时钟(RTC 的 AHB3/APB3 除外)。 下图显示了待机模式下处于 INACTIVE 阶段的 ULPMark-CP,其中平均电流消耗为 1.34µA。 + j# g- t6 @! [7 l7 G% |7 M/ P

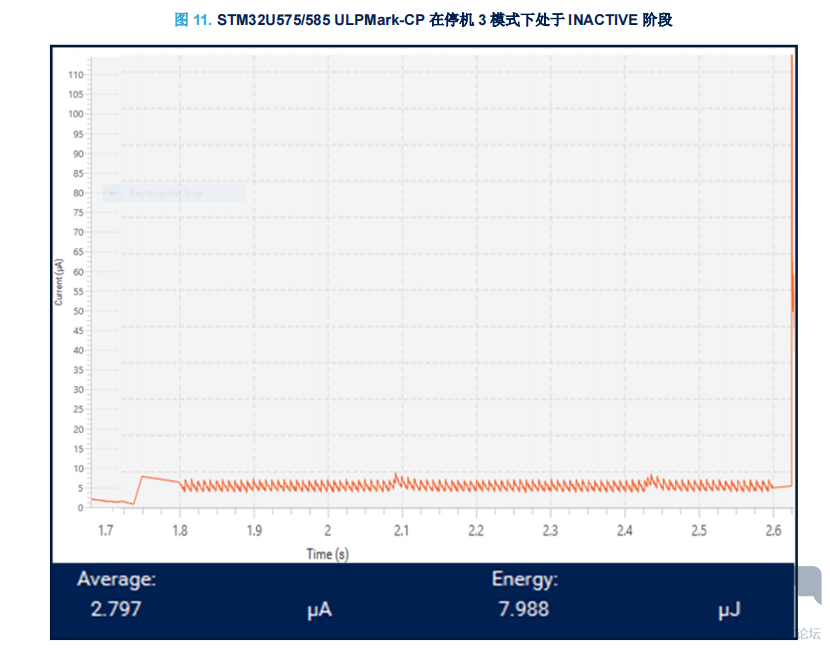

下图显示了停机 3 模式下处于 INACTIVE 阶段的 ULPMark-CP,其中平均电流消耗为 2.97µA。 1 R& N! s$ Y# t) j

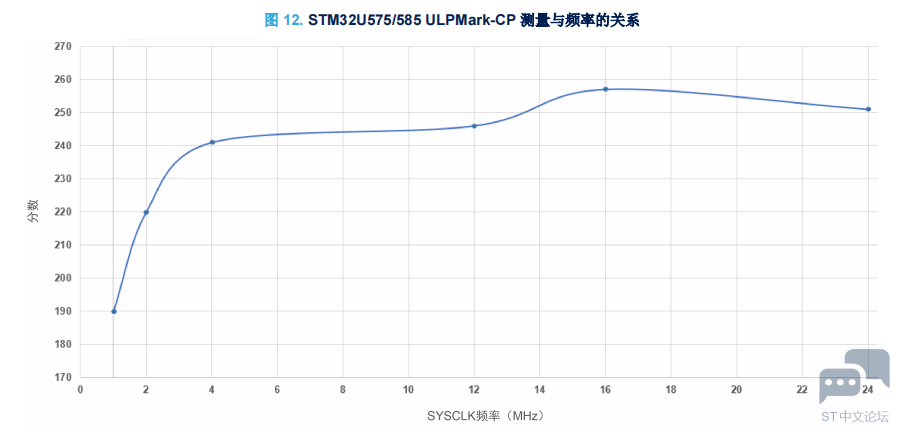

! T) I8 z$ s* Z8 ?' Q% |% | 在 ULPBench 基准的情况下,唤醒周期为 1 秒,处理载荷约为每秒 10 K 循环时,最佳选择是在 INACTIVE 阶段使 用待机模式,在 PROCESS 阶段关联地使用 16 MHz(来自 MSIS)下电压调节 Range 4 模式。; L* h* p' i7 h7 |7 S3 L 5.5 STM32U575/585 测量结果 下图显示了在 PROCESS 阶段使用不同系统时钟频率进行的 ULPMark-CP 得分测量,其中非活动阶段使用具有; i9 g7 |; i2 K, ]# B BKPSRAM 保留和 RTC 功能的待机模式。8 ^# ~- ~0 p3 L2 J ) D8 Z! b3 c/ {2 Q9 p

结果提供了不同的时钟配置:对于低于 24MHz 的频率,使用 MSI(因为从待机模式唤醒时会自动启动)。 如在理论研究中已经看到的,使用电压调节范围 4 在 16 MHz 时,使用 MSIS 实现最佳结果。3 H' B" H, U; D! N% q2 L" M 0 c8 f* u7 d( W. w9 q* e7 G+ k 5.6 电压范围内的性能演变8 @" i) c- D, H! a4 c8 H2 z EEMBC 定义了 3.0V 的基础测试默认值,但该电压并不代表电池供电的低功耗应用。使用 LDO 调压器时,与保持 在 3.0V 相比,移至较低电压时的功率增益明显。相反,当使用 SMPS 调压器增加 VDD 时,功耗降低。这就是为什" _5 m% K2 P: b5 q: u& ~0 Y 么 EEMBC 引入了用户定义电压的比较,让制造商选择理想的工作条件。 下图显示了不同电压下的 ULPMark-CP 得分测量。 ) O: F# N: o6 y% c + B+ ?6 }. B7 }1 O& C* `+ K 以上曲线对应于 16MHz MSIS 模式下的电压调节范围 4。其中清楚地显示了电压降低的优势。 6 结论 本应用笔记介绍了 STM32U575/585 微控制器的超低功耗特点。它们显示了此微控制器系列在嵌入式系统中降低电 流消耗方面所具有的优势。无论何种应用,这些器件均可在优化性能和功耗方面提供多种选择。0 ~: ?! }9 S/ M8 `: L 基于实验和定量结果,本文档提供了相关指南,帮助根据终端用户应用的特点和约束条件,快速选择最佳运行和低" b( E# q4 E$ v2 R 功耗模式。 ( y L9 @0 p2 _& B. ~( n $ k6 e; I8 y6 m2 j9 U& V) i% _ ) O0 ~$ u, h; O: a |

STM32U5低功耗测试

STM32怎么选型

内存配置的艺术:STM32为嵌入式系统高端UI优化RAM和闪存的三大策略

STM32U5 系列使用 LPBAM 进行功耗优化

【STM32U545】实现CAN数据收发

【我的STM32U5 项目秀】+04-MPU6050在STM32U5上的移植

实战经验 | 基于 STM32U5 创建 USBx_CustomHID 通信

STM32U5 x E-BIKE,记录你的骑行多巴胺

基于STM32U5系列TIMER+DMA+DAC应用经验分享

实战经验 | 基于 STM32U5 片内温度传感器正确测算温度

微信公众号

微信公众号

手机版

手机版