.png) STMCU小助手

发布时间:2022-7-31 23:14

STMCU小助手

发布时间:2022-7-31 23:14

|

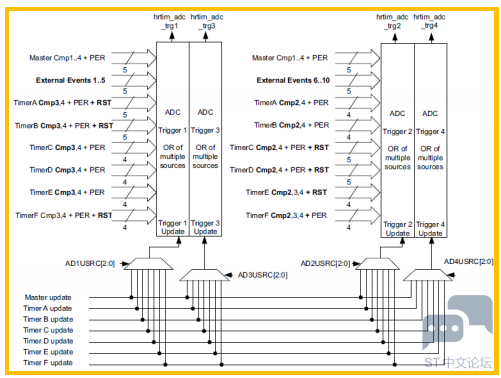

1. 前言 当前的数字电源设计中,ADC 与定时器是最重要的两个外设,算法基于 ADC 的采样结果来计算更新 PWM 输出,以实现环路控制。一般情况下使用定时器的复位/周期事件或是某个比较事件来触发 ADC 转换,然后在 ADC 转换完成中断中执行环路算法,让 ADC 的转换频率、算法执行频率与 PWM 频率保持一致。但是某些情况下 ADC 的转换频率或是环路计算频率跟不上 PWM 的频率,需要对 ADC 的触发进行分频,实现每 N 个 PWM 周期触发一次 ADC 转换。本文基于STM32G474 介绍在高精度定时器与高级控制定时器中如何实现 ADC 的触发分频。 2. 高精度定时器中 ADC 分频的实现 在 G474 的高精度定时器中有多达 10 路的 ADC 触发信道,每个触发通道有多达 32 种触发源可以选择,PWM 发波可以与 ADC 触发非常灵活的关联。如下图为 hrtim_adc_trg1~hrtim_adc_trg4 与其对应可选触发源的框图。

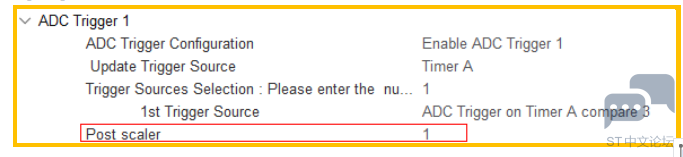

高精度定时器中通过“ADC post-scaler”来实现 ADC 触发源的分频,配置 ADCxPSC[4:0]即可。如下图所示为在定时器工作在 up-counting 计数模式下,设置某个比较事件触发 ADC 转换,在 ADCxPSC[4:0]配置不同的值时实现 ADC 触发分频输出的示意图。

![PW[F_XZGFHO90H(]N3J]A.png PW[F_XZGFHO90H(]N3J]A.png](data/attachment/forum/202207/31/231047yaefr88hr3h1xrem.png)

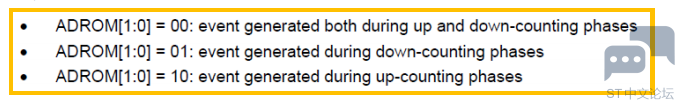

当定时器工作在 up-down counting 计数模式下时,对于设定的比较值或是 Roll-Over 都存在 两个点,所以首先还需通过设置 ADROM 来确定触发点,如下:

如下图所示为在定时器工作在 up-down counting 计数模式下,设置某个比较事件触发 ADC 转换,在 ADCxPSC[4:0]与 ADROM[1:0]配置不同的值时实现 ADC 触发分频输出的示意图。 ![%5G8DG1O3]G~)`3O8H6ZN6V.png %5G8DG1O3]G~)`3O8H6ZN6V.png](data/attachment/forum/202207/31/231235evpde25xhk5xzexv.png)

完整版请查看:附件 |

LAT1065_STM32G4中ADC触发分频的实现方式_v1.0.pdf

下载693.86 KB, 下载次数: 32

经验分享 | STM32G4双BANK启动应用演示

STM32G4 LPTIM+DMAMUX 实现并行输出应用示例

实战经验 | LAT1578 SAU对NSC分区的影响

经验分享 | STM32G474 HRTIM Triggered-half模式实现两相交错电源180°相位同步方案

STM32大神笔记,超详细单片机学习汇总资料

经验分享 | 为什么重启ADC的DMA传输要先停掉ADC?

实战经验 | 基于STM32G474的三相LLC+SR PWM产出方案

STM32固件库分享,超全系列整理

经验分享 | STM32G4 双BANK Flash模式页擦除话题

经验分享 | STM32G4片内FLASH擦写实验笔记

微信公众号

微信公众号

手机版

手机版