.png) STMCU小助手

发布时间:2023-2-13 21:01

STMCU小助手

发布时间:2023-2-13 21:01

|

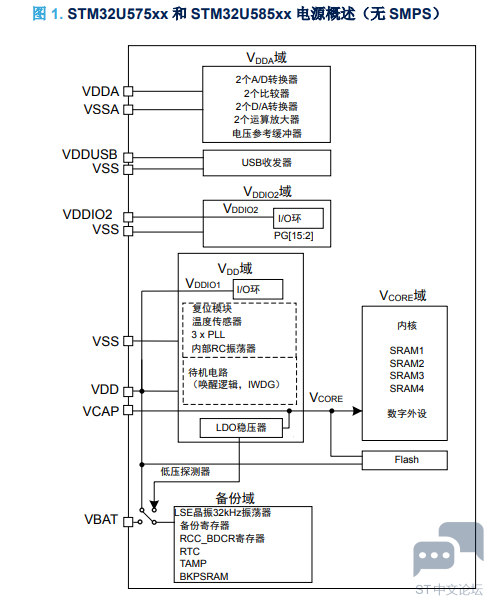

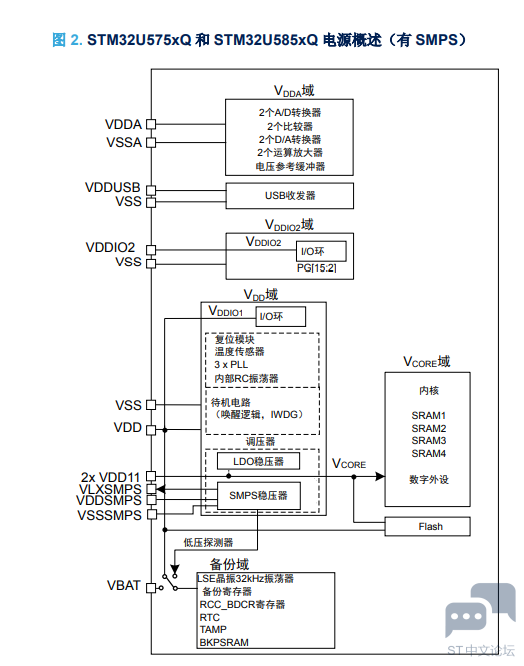

引言 本应用笔记为系统开发者概述了开发板特性的硬件实现。开发板特性为供电电源、时钟管理、复位控制、自举模式设置和调试管理。本文档详细介绍了如何使用 STM32U575xx 和 STM32U585xx 微控制器(也称为 STM32U575/585)。其中介绍了使用这些 MCU开发应用程序所需的最少硬件资源。 本文还包括了详细的参考设计原理图,说明了其主元件、接口和模式。 1概述 提示本文档适用于基于 Arm®的 STM32U575/585 微控制器。 2 电源管理 2.1 电源 STM32U575/585 器件要求 1.71 至 3.6 V 的工作电压电源(VDD)。 下面列出的独立电源可用于特定外设: • VDD = 1.71 V 至 3.6 V VDD 是为 I/O、内部稳压器和系统模拟信号(如复位、电源管理和内部时钟)供电的外部电源。VDD 通过VDD 引脚从外部提供。 • VDDA = 1.58 V (COMPs) / 1.6 V (DACs/OPAMPs) / 1.62 V (ADCs) / 1.8 V (VREFBUF) 至 3.6 VVDDA 是为 A/D 转换器、D/A 转换器、电压参考缓冲器、运算放大器和比较器供电的外部模拟电源。VDDA 电压电平独立于 VDD 电压。不使用这些外设时,VDDA 引脚必须优先连接至 VDD 电压电源。 提示 如果 VDDA 引脚保持为高阻抗或连接至 VSS,则可施加到 I/O(具有"_a" I/O 结构)上的最大输入电压将降低(参见器件数据手册以了解更多详细信息)。 • VDDSMPS = 1.71 V 至 3.6 VVDDSMPS 是为 SMPS 降压转换器供电的外部电源。它通过 VDDSMPS 引脚从外部提供,且必须连接到与VDD 引脚相同的电源。 • VLXSMPSVLXSMPS 引脚是开关 SMPS 降压转换器输出。 • VDD11VDD11 是通过内部 SMPS 降压转换器 VLXSMPS 引脚提供的数字内核电源。仅出现在具有内部 SMPS 的封装上的两个 VDD11 引脚连接至总量为 4.7 µF(典型值)的外部电容。此外,每个 VDD11 引脚需要一个 100 nF陶瓷电容。 • VCAPVCAP 是来自内部 LDO 稳压器的数字内核电源。VCAP 引脚(一个或两个)仅出现在只具有 LDO(无SMPS)的封装上,需要连接至总量为 4.7 μF(典型值)的外部电容。此外,每个 VCAP 引脚需要一个 100nF 陶瓷电容。 提示 – 如果有两个 VCAP 引脚(UFBGA169 封装),则每个引脚必须连接至 2.2 µF 电容(总量约为 4.4 µF)(最大 4.7 µF)。每个 VCAP 还需要一个 100 nF 陶瓷电容。 – SMPS 电源引脚(VLXSMPS、VDD11、VDDSMPS、VSSSMPS)仅在具有 SMPS 的封装上可用。在此类封装中,STM32U575/585 器件并联嵌入了两个稳压器(一个 LDO 和一个 SMPS),以便为数字外设提供VCORE 电源。 VDD11 引脚上需要总 4.7 μF 的外部电容和 2.2 µH 线圈。此外,每个 VDD11 引脚需要一个100 nF 陶瓷电容。 – Flash 由 VCORE 和 VDD 供电。 • VDDUSB = 3.0 V 至 3.6 VVDDUSB 为外部独立电源,为 USB 收发器供电。VDDUSB 电压电平独立于 VDD 电压。 不使用 USB 时,VDDUSB 引脚必须优先连接至 VDD 电压电源。 提示 如果 VDDUSB 引脚保持为高阻抗或连接至 VSS,则可施加到 I/O(具有"_u" I/O 结构)上的最大输入电压将降低(参见器件数据手册以了解更多详细信息)。 • VDDIO2 = 1.08 V 至 3.6 V VDDIO2 是为 14 个 I/O (port G[15:2])供电的外部电源。VDDIO2 电压级别与 VDD 电压无关,不使用 PG[15:2]时,最好连接到 VDD。 提示 在小封装上,VDDA、VDDIO2 或 VDDUSB 独立电源可能不作为专用引脚出现,且内部连接至 VDD 引脚。如果产品上不支持某功能,则该功能也不会出现。 • VBAT = 1.65 V 至 3.6 V(保证功能降至 VBOR_VBAT 最小值,参见产品数据手册) 当 VDD 掉电时(通过电源开关),VBAT 为 RTC、TAMP、外部时钟 32 kHz 振荡器、备份寄存器和可选备份SRAM 提供电源。 • VREF- 和 VREF+ VREF+ 为 ADC 和 DAC 的输入参考电压。使能时,它还是内部电压参考缓冲器(VREFBUF)的输出。当ADC 和 DAC 不使能时,VREF+引脚可接地。 内部电压参考缓冲器支持四个输出电压,可利用 VREFBUF_CSR 寄存器中的 VRS[2:0]字段进行配置: – VREF+大约为 1.5 V。这要求 VDDA ≥ 1.8 V。 – VREF+大约为 1.8 V。这要求 VDDA ≥ 2.1 V。 – VREF+大约为 2.048 V。这要求 VDDA ≥ 2.4 V。 – VREF+大约为 2.5 V。这要求 VDDA ≥ 2.8 V。 VREF- 和 VREF+ 引脚并非在所有封装上可用。当不可用时,它们分别与 VSSA 和 VDDA 引脚绑定。当 VREF+引脚与 VDDA 在一个封装中互相绑定时,内部 VREFBUF 不可用且必须禁用。VREF- 必须始终等于 VSSA。 下图显示了 STM32U575/585 器件电源概述,具体取决于 SMPS 存在性。

在无 SMPS 的器件中,I/O 和系统模拟外设(如 PLL 和复位模块)由 DD 电源供电。为数字外设和存储器供电的VCORE 电源由 LDO 生成。如果选定的封装具有 SMPS 降压转换器选项,但 SMPS 不被应用程序使用(而是使用嵌入式 LDO),则建议设置 SMPS 电源引脚,如下所示:• 将 VDDSMPS 和 VLXSMPS 连接至 VSS • 将 VDD11 引脚通过两个(2.2 µF + 100 nF)电容连接至 VSS(如在正常模式下) 独立模拟外设电源 为了提高 ADC 和 DAC 转换精度、扩展供电的灵活性,模拟外设配有独立电源,可以单独滤波并屏蔽 PCB 上的噪声。 模拟外设的电压电源输入在单独的 VDDA 引脚上可用。VSSA 引脚提供了独立的电源接地连接。 VDDA 电源电压可与 VDD 不同。复位后,由 VDDA 供电的模拟外设是逻辑隔离且电隔离的,因而不可用。当 VDDA电源存在时,使用这些外设前,必须通过设置 PWR_SVMCR 寄存器中的 ASV 位,解除此隔离。 VDDA 电源可由模拟电压监测(AVM)监控,并与两个阈值(AVM1 为 1.6 V,而 AVM2 为 1.8 V)进行比较。有关更多详细信息,请参见器件数据手册和参考手册的“外设电压监测(PVM)”部分。 当使用单供电时,VDDA 引脚可外部连接至同一 VDD 电源,为得到无噪声的 VDD 参考电压,需通过外部滤波电路。 ADC 和 DAC 参考电压 为确保低电压输入和输出上的更好精度,用户可将 VREF+连接至一个独立的、低于 VDDA 的参考电压源。 对于模拟输入 (ADC)或输出 (DAC)信号, VREF+为最高电压,以满量程值表示。VREF+可由外部参考或VREFBUF(可以输出可配置电压:1.5、1.8、2.048 或 2.5 V)来提供。VREFBUF 还可通过 VREF+引脚为外部元件提供电压。 有关更多信息,请参见器件数据手册和参考手册的“电压参考缓冲器(VREFBUF)”部分。 独立 I/O 电源轨 来自端口 G(PG[15:2])的一些 I/O 由单独的电源轨供电。此轨的电源范围为 1.08 V 至 3.6 V,可通过 VDDIO2 引脚外部提供。VDDIO2 电压电平完全独立于 VDD 或 VDDA。 VDDIO2 引脚仅可用于一些封装(参见数据手册中的引脚排列详细信息,以了解 I/O 列表)。 复位后,由 VDDIO2 供电的 I/O 是逻辑隔离且电隔离的,因而不可用。当 VDDIO2 电源存在时,从 PG[15:2]使用任一I/O 前,必须通过设置 PWR_SVMR 寄存器中的 IO2SV 位,解除此隔离。 VDDIO2 电源由 VDDIO2 电压监测(IO2VM)监控且与内部参考电压(3/4 VREFINT,约为 0.9 V)进行比较。有关更多详细信息,请参见器件数据手册和参考手册的“外设电压监测(PVM)”部分。 独立的 USB 收发器电源 USB 收发器通过一个单独的电源 VDDUSB 供电。VDDUSB 范围从 3.0 V 到 3.6V,完全独立于 VDD 或 VDDA。 复位后,由 VDDUSB 供电的 USB 功能是逻辑隔离且电隔离的,因而不可用。当 VDDUSB 电源存在时,使用 USBOTG 外设前,须通过设置 PWR_SVMR 寄存器中的 USV 位,解除此隔离。 VDDUSB 电源由 USB 电压监测(UVM)监控且与内部参考电压(VREFINT,约为 1.2 V)进行比较。有关更多详细信息,请参见器件数据手册和产品参考手册的“外设电压监测(PVM)”部分。 电池备份域 为了在 VDD 掉电时,还能保留备份寄存器的内容,且为 RTC 供电,可将 VBAT 引脚连接到电池或者其他备用电源上。 VBAT 引脚为 RTC、TAMP、LSE 振荡器和 PC13 到 PC15 I/O 供电,允许 RTC 在主电源关闭时也可工作。 当在 PWR_BDCR1 寄存器中设置 BREN 位时,可通过 VBAT 引脚为备份 SRAM 供电。 VBAT 电源的开关由复位模块中内置的掉电复位电路进行控制。 Caution: • 在 tRSTTEMPO(VDD 启动时)或 PDR(下电复位)检测期间,VBAT 和 VDD 之间的电源开关仍连接到 VBAT引脚。 • 在启动阶段,如果 VDD 的建立时间小于 tRSTTEMPO(有关 tRSTTEMPO 的值,参见数据手册)且 VDD > VBAT+ 0.6 V,会有电流经由 VDD 引脚和电源开关(VBAT)之间连接的内部二极管注入 VBAT 引脚。 如果连接到VBAT 引脚的电源/电池无法承受此注入电流,则强烈建议在该电源与 VBAT 引脚之间连接一个低压降二极管。 如果没有使用任何外部电池,建议将该 VBAT 引脚连接到带有 100 nF 外部去耦电容的 VDD 上。 通过 VDD 对备份域供电时(模拟开关连接到 VDD 引脚),以下引脚可用: • PC13、PC14 和 PC15,可用作 GPIO 引脚 • PC13、PC14 和 PC15——三个引脚可由 RTC 或 LSE 进行配置(参见参考手册的 RTC 部分) • 下列引脚,由 TAMP 配置为篡改引脚: – PE3(TAMP_IN6/TAMP_OUT3) – PE4(TAMP_IN7/TAMP_OUT8) – PE5(TAMP_IN8/TAMP_OUT7) – PE6(TAMP_IN3/TAMP_OUT6) – PC13(TAMP_IN1/TAMP_OUT2) – PA0(TAMP_IN2/TAMP_OUT1) – PA1(TAMP_IN5/TAMP_OUT4) – PC5(TAMP_IN4/TAMP_OUT5) 完整版请查看:附件 |

STM32U575585 MCU 硬件开发入门.pdf

下载707.29 KB, 下载次数: 9

经验分享 | STM32U5 ADC+TIM+DMA 2D传输应用演示

【经验分享】LAT1496 基于 USBD库CDC Standalone例程中的一个Bug解析

STM32U5A9JDK试用---MIPI-DSI屏幕驱动

STM32U5 ADC 自校准失败终极解决:VDDA 隔离解除 + 电压调整器就绪实操指南

《STM32U3线上课程》学习笔记+STM32U3 超低功耗 MCU,超低功耗及数据安全

立即在GitHub上抢先体验面向STM32U5的最新STM32Cube HAL更新

STM32开发五大误区,新手别傻傻信了

实战经验 | STM32U5周期性异常复位问题分析

经验分享 | 一个 STM32U5 SBSFU SecureFault 问题定位与分析

经验分享 | STM32U5系列TIMER+DMA+DAC应用演示

微信公众号

微信公众号

手机版

手机版