.png) STMCU小助手

发布时间:2023-2-15 21:03

STMCU小助手

发布时间:2023-2-15 21:03

|

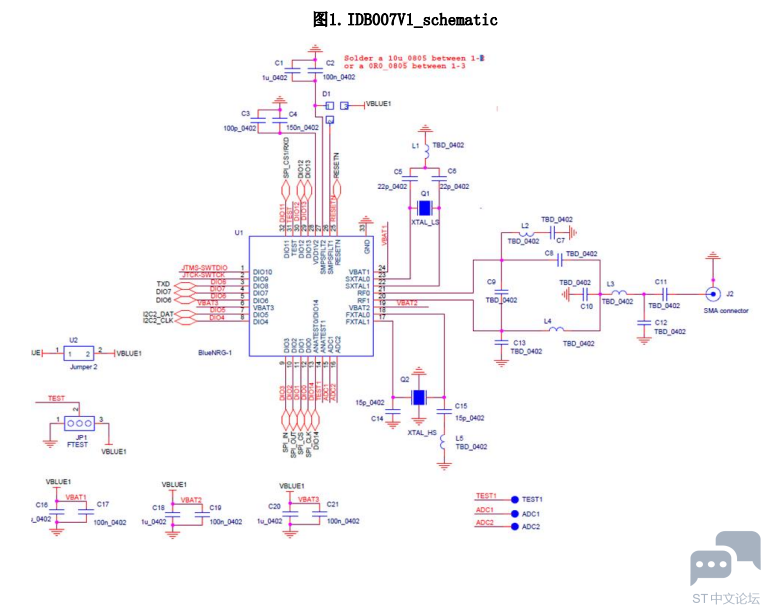

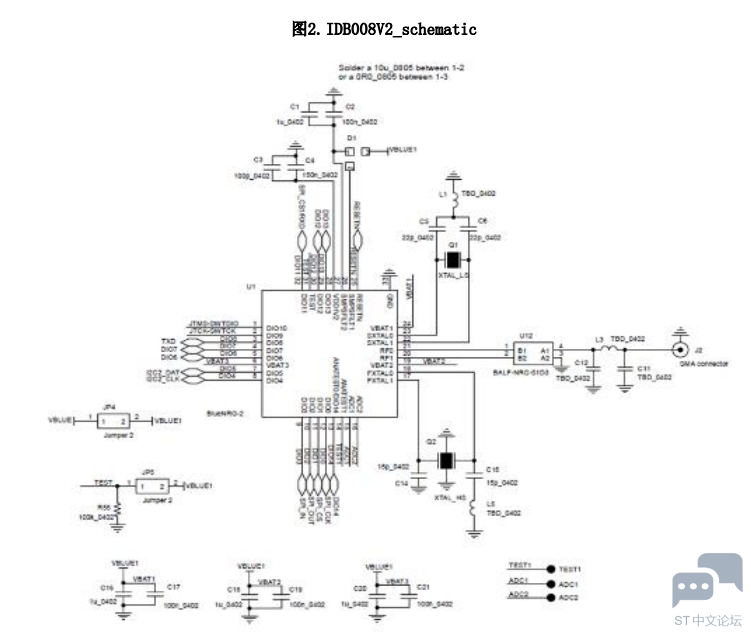

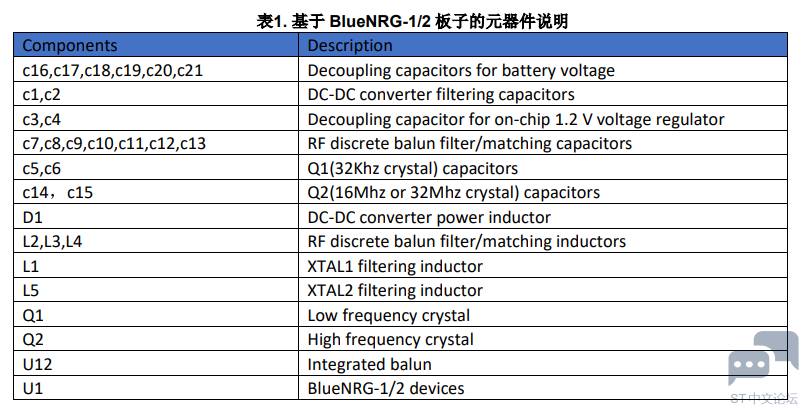

1. 前言 为了让客户在原理图设计阶段少走弯路,我这里结合客户评估和设计阶段常遇到的问题,整理了一下 BlueNRG-1/-2 相关设计及注意事项以备客户解惑用。 2. BlueNRG-1/-2 的原理图参数说明及设计注意事项 2.1. BlueNRG-1/-2 原理图及参数如下:

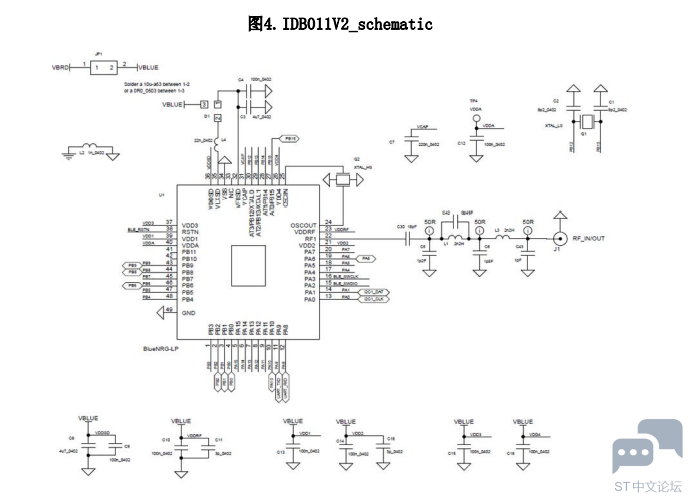

2.2. 原理图设计注意事项: 1. C4 的取值只能是 150nf 或者 220nf,否则会影响系统的稳定。 2. 设计成 SMPS ON 的是时候,D1 中的 pin1 和 pin2 之间焊接一颗电感,该电感的具体要求如下:标称值为 10 uH 或 4.7 uH ,但 DCR 务必小于 1ohm 且额定电流必须大于 100 mA。 3. RXD/TXD 必须接到 DIO11 和 DIO08 pin,否则后续将无法使用 RF Flash utility 工具和 BlueNRG GUI 工具。 4. 这里的 L1=2nH,L5=3.9nH 建议保留,这有助于抑制最后通道的杂散并减少晶体和RF 信号间的相互影响。 5. 建议预留 ANATEST0 pin 和 ANATEST1 pin 的测试点,以便后续测试高速晶体的启振时间。 6. DIO7 建议通过 100kohm 电阻接地并预留测试点:为强制执行 updater 代码(参见预先编程的引导加载程序),建议将 IO7 引脚拉高并硬件复位设备。 3. BlueNRG-LP/LPS 的原理图参数说明及设计注意事项 3.1. BlueNRG-LP 原理图及参数如下: ![S8ZZNGY3ODT@[`5QKVMU]{B.png S8ZZNGY3ODT@[`5QKVMU]{B.png](data/attachment/forum/202302/15/210752mxt97wqsgvg9xx7s.png)

完整版请查看:附件  BlueNRG-X原理图参数说明.pdf

(583.26 KB, 下载次数: 0)

BlueNRG-X原理图参数说明.pdf

(583.26 KB, 下载次数: 0)

|

分享STM32资料-采用 STM32U031R8 MCU 的 STM32 Nucleo-64 开发板,官方资料,数据手册等资料

HRTIM 指南

使用 STM32 的 DWT 单元监控内存

DAC,COMP,HRTIM Fault 功能的使用

一个软件引起的 LSE 驱动不良的问题

STM32 GUI LTDC 最大像素时钟评估方法

STM32 Cordic 运算速度评估

全新OpenSTLinux 6.1版本发布

ST-LINK Utility介绍、下载、安装和使用教程

【2025·STM32峰会】GUI解决方案实训分享1-对LVGL咖啡机例程的牛刀小试以及问题排查

微信公众号

微信公众号

手机版

手机版