.png) STMCU小助手

发布时间:2023-2-16 21:00

STMCU小助手

发布时间:2023-2-16 21:00

|

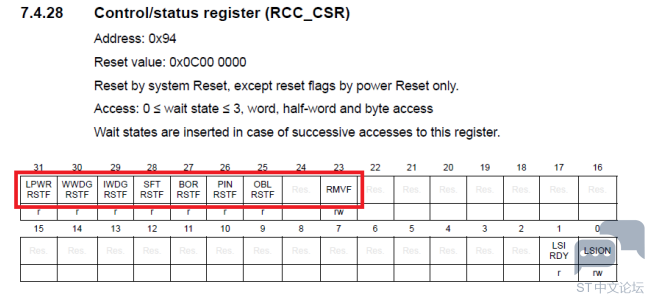

1. 引言 本文探讨一个奇怪的 MCU NRST 管脚异常复位现象。 2. 复位问题及排查 这个问题是客户对开发的平台做 EMS 浪涌测试的时候发生的, 平台上使用了一个STM32G474 RCT6 MCU 。在某个等级的 EMS 测试中, 客户发现 MCU 有时候会异常复位而影响平台的稳定工作。 2.1. MCU 异常复位问题的通常解决思路 我们知道, 导致 MCU 异常复位的原因有很多, 比如外部复位电路被干扰, MCU 电源的异常跌落, 看门狗不能正常喂狗导致的复位等等。 STM32 MCU 的复位标志位寄存器可以帮助我们发现导致异常复位的线索。 复位标志位的相关信息可以在 STM32 MCU 的 Reference Manual 中找到。在 RCC 章节的 RCC_CSR 寄存器中,我们可以看到:

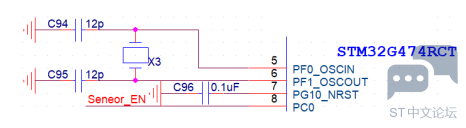

图中红色围住的部分就是复位标志相关的寄存器。 LPWRRSTF:低功耗模式复位标志位, 被置 1 表示发生了非法的 STOP, SLEEP 或SHUTDOWN 等低功耗模式进入。 WWDGRSTF: 窗口看门狗复位标志。 IWDGRSTF: 独立看门狗复位标志。 SFTRWTF: 软件复位标志位。 BORRSTF: 欠压复位标志位。 PINRSTF: 从 NRST 引脚输入产生的复位的标志位。 OBLRSTF: 加载选项字节产生的复位的标志位。 以上的标志位被置 1 表示发生了相关的复位。 这些被置 1 的标志位可以通过向 RMVF 位写 1 清除。 在一次正常的 MCU 上电过程中, 电压的上升和 PDR 电路的工作必然会导致BORRSTF 和 PINRSTF 被置位 1, 因此在做 EMS 实验前, 需要先通过向 RMVF 写 1将所有复位标志位清除, 然后观察在 EMS 测试导致的复位后, 哪些复位标志位被置位了。 例如,当观察到 BORRSTF 被置 1 表示发生了欠压复位, 需要重点检查 MCU 供电电路包括滤波/退耦电容的设计和布局等等。 PINRSTF 位被置 1 表示 MCU 的 NRST 管脚接收到了能够触发复位的异常低电平,需要检查 NRST 的外围电路是如何被干扰的, 或设法增加滤波电路滤除干扰。 WWDGRSTF 或 IWDGRSTF 被置 1 表示喂狗不正常导致了复位,一般是由程序在EMS 测试中运行不正常进入死循环导致,MCU 被 EMS 干扰影响的途径相对难以判断,可能是地或某个/些 GPIO 管脚被 EMS 干扰侵入而影响了 MCU 的正常运行。 通过观察异常复位发生后的复位标志位,可以使我们避免解决问题时在不相关的电路上浪费时间, 比如如果只有 BORRSTF 被置位, 我们需要重点关注供电电路, 而不需要在复位管脚相关电路做无用的调整。 2.2. 在客户开发平台上的排查 根据上面 2.1 节描述的思路,我们在客户的平台上排查发生异常复位的原因, 通过检查 STM32G4 的复位标志位,发现复位发生后 PINRSTF 被置 1 了。 这似乎是个简单的 NRST 复位管脚被干扰的问题。 但是观察客户的设计, NRST 管脚并没有外接比较长走线的外部电路, 只是在管脚放置了一颗 0.1UF 的电容。按常理这样的电路一般不会将干扰引入 NRST 管脚。

为了避免是 0.1UF 电容将地噪声引入管脚, 拆除这颗电容后再做浪涌实验, 结果PINRSTF 还是被置位。STM32G4 有一个新功能, NRST 管脚可以被复用为一个 GPIO PG10, 当这个管脚被定义为 PG10 后, 加在这个管脚的低电平干扰将不会再导致 MCU 复位。但是奇怪的事情发生了,STM32G474 第 7 脚由 NRST 改定义成 PG10 后(Option byte 中修改),浪涌实验中依然发生了 PINRSTF 被置位的现象。 这时候看来不能只局限于 NRST 管脚的探查了,干扰是不是从其它 GPIO 窜入 MCU 并进一步通过耦合影响了复位电路的工作呢? 在 LQFP 的封装中,由于 MCU 内部并行的较长的 bonding 线的存在, 相邻的 GPIO之间 最可能产生耦合干扰, 所以我们从第 7 脚相邻的第 6 和 8 脚开始排查。分别将它们的外部信号断开。 通过排查, 第 8 脚信号断开没有解决问题。 但是当将第 6 脚相连的晶振和电容断开,并改用内部 HSI 时钟源后, 异常复位问题消失了, PINRSTF 不再被置位。看来干扰是从第 7 脚进入的。观察客户的 PCB 设计, 发现晶振的 CLOAD 电容接地并不是直接接地平面, 而是经过一根细长的地走线后才由一个过孔连接到地平面,很明显这根细长的地走线在浪涌测试中作为天线接收了干扰并经电容传递到了 MCU 内部。 完整版请查看:附件  LAT1244_奇怪的NRST 管脚异常复位问题_v1.0.pdf

(255.03 KB, 下载次数: 18)

LAT1244_奇怪的NRST 管脚异常复位问题_v1.0.pdf

(255.03 KB, 下载次数: 18)

|

分享STM32资料-采用 STM32U031R8 MCU 的 STM32 Nucleo-64 开发板,官方资料,数据手册等资料

HRTIM 指南

使用 STM32 的 DWT 单元监控内存

DAC,COMP,HRTIM Fault 功能的使用

一个软件引起的 LSE 驱动不良的问题

STM32 GUI LTDC 最大像素时钟评估方法

STM32 Cordic 运算速度评估

全新OpenSTLinux 6.1版本发布

ST-LINK Utility介绍、下载、安装和使用教程

【2025·STM32峰会】GUI解决方案实训分享1-对LVGL咖啡机例程的牛刀小试以及问题排查

微信公众号

微信公众号

手机版

手机版