.png) STMCU小助手

发布时间:2023-4-21 17:59

STMCU小助手

发布时间:2023-4-21 17:59

|

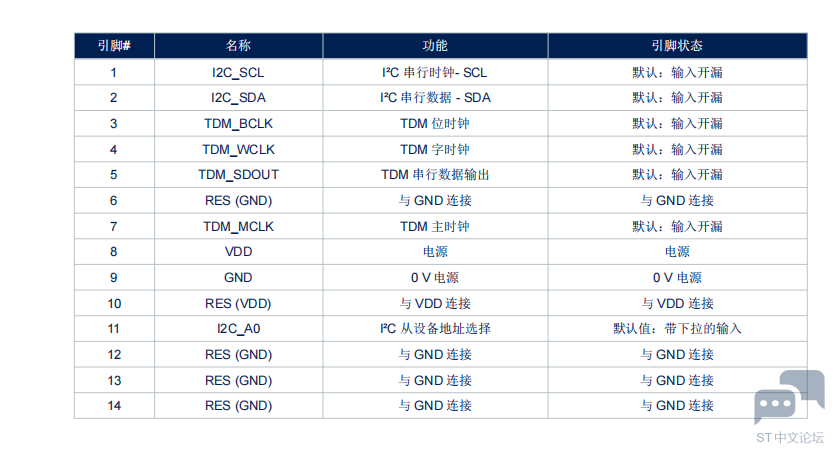

引言 本文档旨在提供 ST LIS25BA 运动传感器相关的使用信息和应用提示。 LIS25BA 是一种高性能 3 轴 MEMS 加速度计,具有低噪声、高且平坦的带宽和时分复用(TDM)接口。 该器件具有±3.85 g 的满量程加速度范围,并能以 2400 Hz 的信号带宽测量加速度。 由于具有高带宽,LIS25BA 特别适用于可穿戴设备或智能耳机,并可以显著提高音频质量,尤其是在使用 ST MEMS 麦克风实现降噪功能的系统中。器件关键应用为骨骼振动检测、波束成形增强和语音检测增强。 LIS25BA 采用纤薄的小型塑料平面网格阵列封装(LGA),可确保在更大的温度范围(-40 °C 至+85 °C)内正常工作。 1引脚说明 ![$FJ9_AFFP1BK%]YH(T}YGNY.png $FJ9_AFFP1BK%]YH(T}YGNY.png](data/attachment/forum/202304/21/180022fl6eb9no6i5o8en4.png)

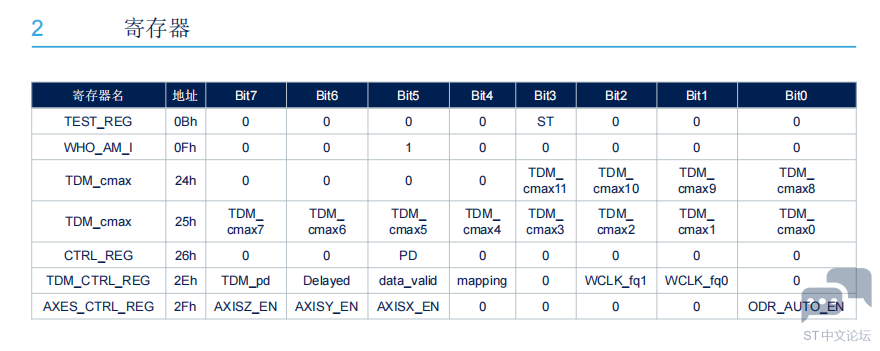

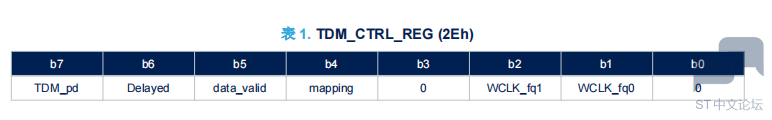

3 工作模式 LIS25BA 具有两种工作模式: • 禁用模式; • 正常模式。 供电后,LIS25BA 执行一段 5.5 ms 的启动程序来加载修整参数。启动完成后,器件会自动配置为禁用模式。 LIS25BA 提供两种接口: • I²C 数字接口,用于配置器件; • TDM 接口,用于检索加速度数据。 当传感器处于禁用模式时,器件几乎所有内部模块都会关闭。I²C 数字接口保持激活,以便能够与器件进行通信。 在正常模式下,可通过将 CTRL_REG 寄存器的 PD 位置 0 来配置 LIS25BA:在正常模式下,感应链处于激活状态。 为了采集加速度输出数据,必须使能 TDM 接口。建议在使能接口前设置所有 TDM 接口时钟(MCLK、BCLK 和WCLK)。可通过将 TDM_CTRL_REG 寄存器的 TDM_pd 位置 0 来使能 TDM 接口。 3.1 TDM 接口配置 TDM 接口可通过 TDM_CTRL_REG 寄存器进行配置。

TDM_pd Delayed data_valid mapping 0 WCLK_fq1 WCLK_fq0 0 • TDM_pd:TDM 使能。如果 TDM_pd 位置 0,则 TDM 接口使能,否则禁用。 • Delayed:TDM 延迟配置。如果 Delayed 位置 0,则 TDM 使用“不延迟”配置,否则使用“延迟”配置。选择“不延迟”配置时,在 WCLK 上升沿后的第一个上升/下降沿进行 SLOT0 数据采样(基于 data_valid 位的值,如下文所述);选择“延迟”配置时,在 WCLK 上升沿后的第二个上升/下降沿进行 SLOT0 数据采样。 • data_valid:TDM 数据有效配置。如果 data_valid 位置 0,在位时钟(BCLK)的上升沿进行数据采样,否则在下降沿进行采样。 • mapping:TDM 映射配置。如果 mapping 位置 0,分别在 SLOT0、SLOT1 和 SLOT2 中映射加速度计 X-Y-Z数据,否则在 SLOT4、SLOT5 和 SLOT6 中映射。在未激活插槽的转换过程中,TDM_SDOUT 引脚配置为高阻抗。 • WCLK_fq:TDM 时钟频率,如下一节所述。 LIS25BA 为 TDM 接口提供了四种可能的配置:下表总结了与支持的每种 TDM 配置相关的 Delayed 和 data_valid配置。 ![XBKOA]7WMI[UW[TXHOL87.png XBKOA]7WMI[UW[TXHOL87.png](data/attachment/forum/202304/21/180022j260ob7lm5o6wx6o.png)

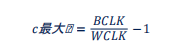

3.2 TDM 时钟频率 WCLK 信号的功能是识别帧的开始,特别是始于 WCLK 信号上升沿的帧。支持的 WCLK 宽度为: • 16-slot 宽度(1024 个 BCLK 周期,50%占空比); • 1-slot 宽度(16 个 BCLK 周期); • 1 个 BCLK 周期。 在 TDM 模式下,LIS25BA 可通过 TDM_SDOUT 引脚以下列采样频率输出加速度计数据: • WCLK = 8 kHz; • WCLK = 16 kHz; • WCLK = 24 kHz。 可以用两种不同的方式选择 TDM 时钟频率: • 使用 TDM_CTRL_REG 寄存器的 WCLK_fq[1:0]位。这种情况下,必须将 AXES_CTRL_REG 寄存器的ODR_AUTO_EN 位置 0。WCLK_fq 位的可用配置如下: – 00b:采样频率等于 8 kHz; – 01b:采样频率等于 16 kHz; – 10b:采样频率等于 24 kHz。 • 使用将 MCLK 和 WCLK 作为输入接收的 ODR_auto 功能块的输出(如 LIS25BA 数据手册中所述),按MCLK 与 WCLK 之比计算当前采样频率。可通过将 AXES_CTRL_REG 寄存器的 ODR_AUTO_EN 位置 1 使能 ODR_auto 功能块。根据 WCLK_fq[1:0]位的值,可能的 ODR_auto 功能块输出如下: – 00:采样频率等于 8 kHz (MCLK/WCLK = 1536); – 01:采样频率等于 16 kHz (MCLK/WCLK = 768); – 10:采样频率等于 24 kHz (MCLK/WCLK = 512)。 注意:如果 MCLK 与 WCLK 之比不是 1536、768 和 512,则自动将采样频率强制为 8 kHz。 串行时钟 BCLK 的唯一目的是将数据移出 TDM_SDOUT 串行端口。为此,TDM 接口使用一个内部计数器,该计数器在检测到 WCLK 的上升沿时置为 1,在达到 WCLK 周期中的最大 BCLK 数量时重置为 0。 WCLK 周期中包含的最大 BCLK 数量(即 cmax)可表示为 BCLK 和 WCLK 频率的函数,并且可使用以下等式进行计算: ܿ

为了支持范围[1024 MHz, 12.288 MHz]内的串行时钟 BCLK 变量,从而计算内部 TDM 计数器的正确最大值,有两种可能的解决方案可供选择: • cmax 值是 TDM 接口的输入,设备可以自动计算。此功能默认使能,可通过将 AXES_CTRL_REG 寄存器的ODR_AUTO_EN 位置 0 进行禁用。 • 可通过寄存器 TDM_cmax 设定 TDM cmax。 3.3 轴禁用 在 TDM 模式下,为了减少工作期间的功耗,主机处理器可以通过解除 AXES_CTRL_REG 寄存器中 AXISX_EN、AXISY_EN 或 AXISZ_EN 位的置位选择性地关断每个 LIS25BA 加速度计轴。当轴被关断时,相应的 TDM 插槽将处于高阻抗状态。 数据手册提供了每种模式(单轴、双轴或三轴模式)的典型和最大电流消耗。 3.4 配置切换 必须从 I²C 接口明确地激活 TDM 接口。必须丢弃使能 TDM 接口后的前 3 个采样:这是因为接口同步外部 WCLK。 此外,可以动态地重新配置 TDM 协议,但在这种情况下,TDM 配置变化后的前 3 个采样也将无效。 完整版请查看:附件  AN5169 LIS25BA:带TDM 接口的低噪声、高带宽3 轴数字输出加速度计.pdf

(582.93 KB, 下载次数: 3)

AN5169 LIS25BA:带TDM 接口的低噪声、高带宽3 轴数字输出加速度计.pdf

(582.93 KB, 下载次数: 3)

|

文末有福利 | 意法半导体业内首款Matter NFC芯片, 简化智能家居NFC部署

【STEVAL-25R200SA 测评】低功耗检卡测试

【STEVAL-25R200SA评测】在不同工作负载下的功耗表现,如DPO动态功率输出的性能

【STEVAL-25R200SA评测】天线开发注意事项

【STEVAL-25R200SA评测】低功耗捡卡(LPCD)检测性能

【STEVAL-25R200SA 测评】功耗测试

【STEVAL-25R200SA 测评】资源介绍

【STEVAL-25R200SA评测】低功耗捡卡(LPCD)检测性能

【STEVAL-25R200SA评测】兔哥的ST25-03-低功耗捡卡(LPCD)检测性能

【STEVAL-25R200SA评测】兔哥的ST25-02-不同模式的读写距离

微信公众号

微信公众号

手机版

手机版