|

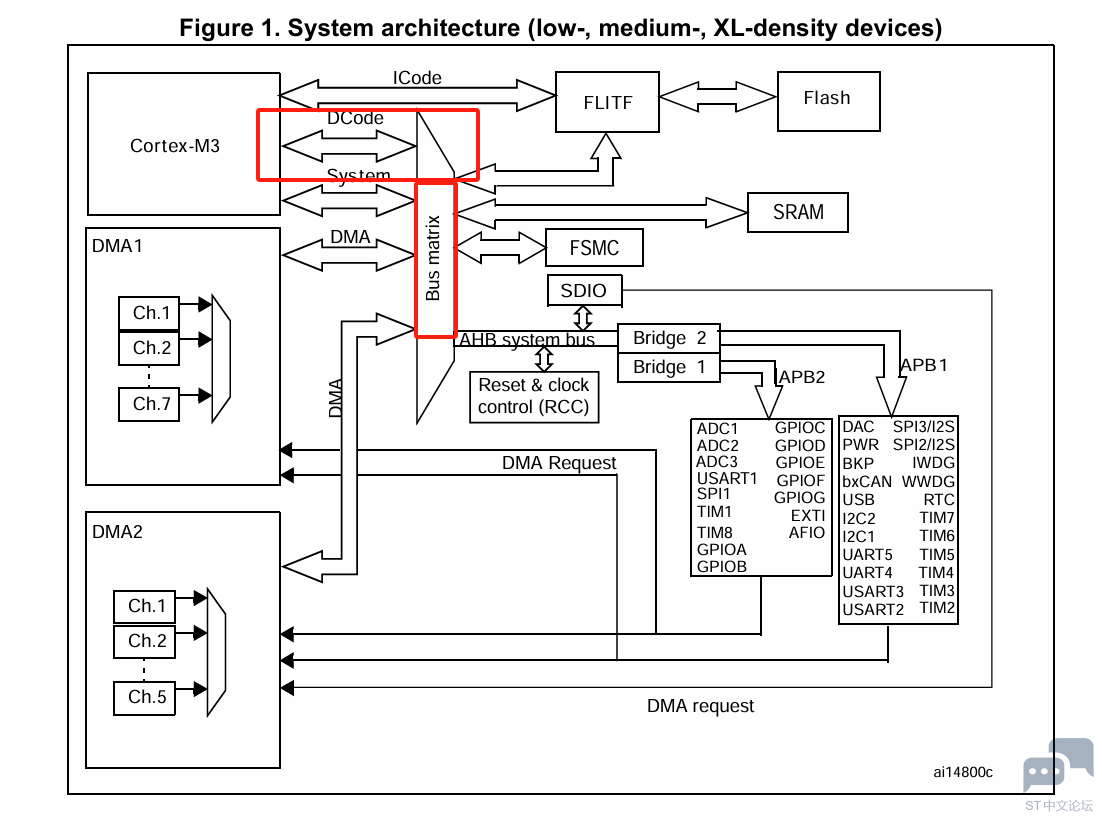

stm32参考手册里的系统架构图中把Dcode连接到bus matirx,但是其对Dcode bus的描述却是连接m3的Dcode到flash的数据接口。 cortex-m3的TRM里面也明确说了Dcode是对代码空间0x00000000 - 0x1FFFFFFF的访问。

并且stm32的参考手册后面的文字描述也与前面的文字描述不符,对bus matirx的描述里面确实说了dcode是bus matirx的4个master的其中一个,和前面图相符,但又和参考手册对dcode的描述不符。 以上好像描述不符的地方,我猜测这种矛盾可能的原因是,因为sram也可以重定向到0x00000000,当这种重定向发生时,确实也是用dcode对代码空间0x00000000 - 0x1FFFFFFF的访问,但访问的是sram,也就把dcode连接到了总线矩阵,但只能访问flash和sram,好像还有它自己boot那一块,但得重映射的时候才有效。 就算这样解释图中也有两处矛盾,一是对Dcode本身的描述,说的是接发FLASH数据接口,而是DMA的描述中对总线矩阵功能的解释,说Dcode访问外设??这是可以的吗?外设怎么样也不能到0x00000000 - 0x1FFFFFFF之间吧? 请各位大佬给小弟解下惑 |

在 STM32CubeIDE 中正确设置 STM32F103C8T6 的 Flash 容量

咨询下,新项目打算用STM32F103的USB与工控机或PAD进行通讯,问题如下

STM32F103 串口下载ST Flash Loader Demo

请问一下STM32F103C8T6的Hardwar NSS Output ENABLE后cs持续拉低是为什么

foc2.0函数SVPWM_3ShuntCalcDutyCycles看不明白

F103的IIC支持高速400K频率吗?

STM32F103RCT6断电以后,ADC会漏电

无源晶振开关电路设计

要在STM32F103C8T6上实现TIM+DMA+ADC采集电压,cubemx配置为什么,代码怎么写

PCF8563(RTC)读取时间有误

微信公众号

微信公众号

手机版

手机版

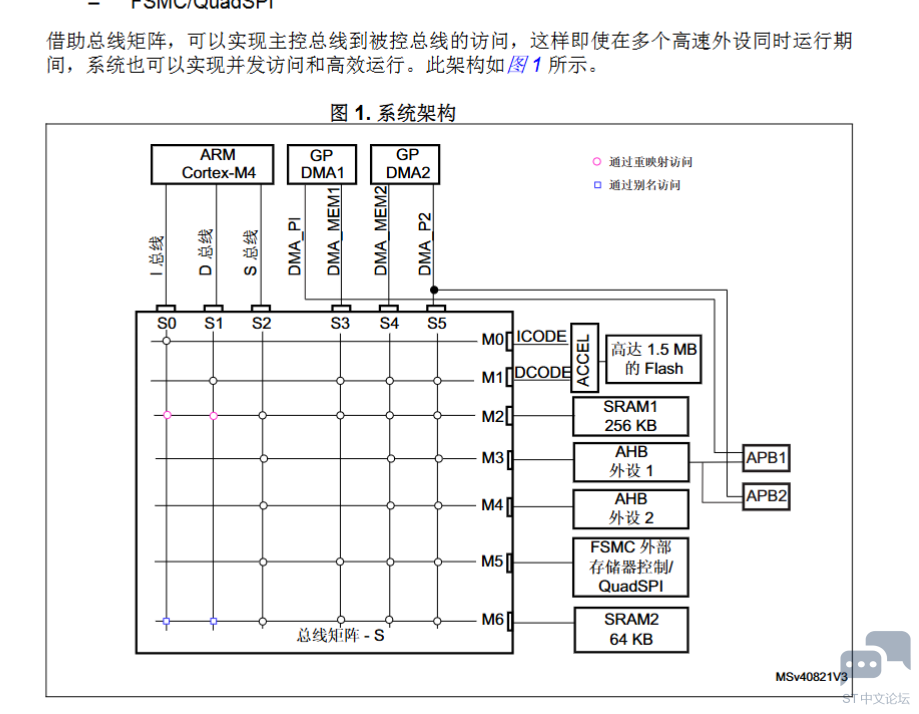

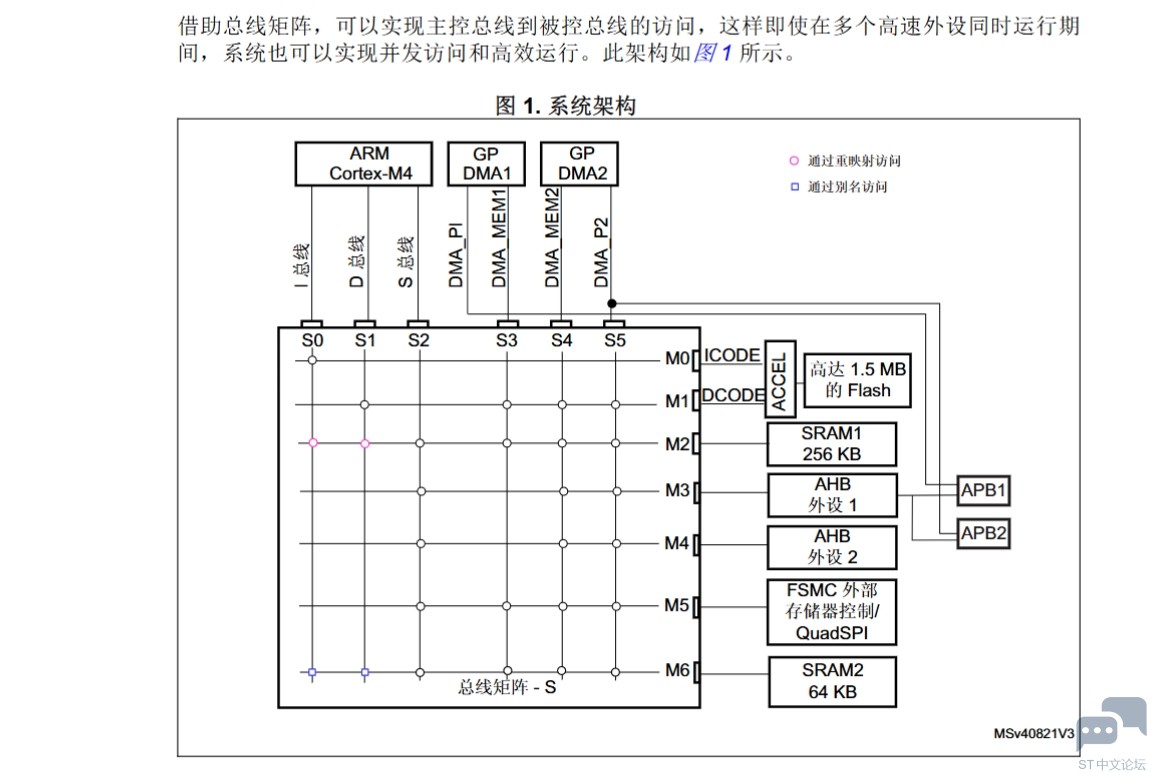

更新,大结局。 TRM确实是对的icode和dcode是执行code使用的。

st更新了bus架构图,回答了我的疑惑,确实是如我猜测的那样,通过重映射来实现icode,dcode对sram的访问