|

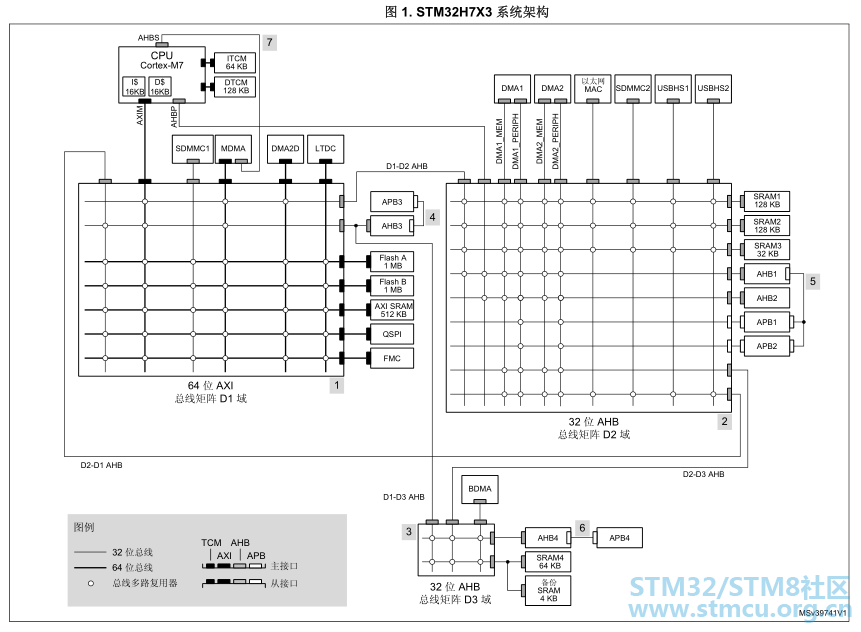

1 文档约定9 Y, @! T* t0 e# a$ B 8 ~5 o) o- W9 w0 \- B 2 存储器和总线架构 c" A" z; |2 o$ x2 [" f) M* a& r ^' M 2.1 系统架构 ( [0 _$ T5 g" }' X: d6 G! W 通过一个 AXI 总线矩阵、两个 AHB 总线矩阵和总线桥,可以将总线主设备与总线从设备实 现互连,如 表 1 和 图 1 所示。

0 X2 D B" x- s" O8 g

- ~4 W. C+ E9 E" U7 P 2.1.1 总线矩阵 D1 域中的 AXI 总线矩阵+ p$ ~& w s7 Q; h4 e; N. Q* s- V D1 域中的多 AXI 总线矩阵为从多个主设备到多个从设备的并发访问提供保证和仲裁。这样可实现高速外设的高效同步运行。7 a) ~ C: R n 仲裁采用带 QoS 功能的轮循调度算法。. |& I1 t' Q F! M0 { DTCM 和 ITCM(数据和指令紧密耦合 RAM)通过专用 TCM 总线直接连接到 Cortex-M7 内核。MDMA 控制器可通过 AHBS(特定的 CPU 从设备 AHB)访问 DTCM 和 ITCM。ITCM由 Cortex-M7 以 CPU 时钟速度(零等待周期)访问。 有关 AXI 互连的更多信息,请参见 第 5 节: AXI 互连 。* z, Z5 k6 E3 E& @6 K D2 域和 D3 域中的 AHB 总线矩阵 D2 域和 D3 域中的 AHB 总线矩阵为从多个主设备到多个从设备的并发访问提供保证和仲% Z& e4 j+ J3 e# C, a+ ^ 裁。这样可实现高速外设的高效同步运行。2 S2 ~5 [$ P( { 仲裁采用循环调度算法。 8 \/ t5 f: K- G. K7 {; y 2.1.2 总线- 总线桥& d$ e, _9 n' L8 p3 T) `4 I- D( g 系统中具有大量的总线-总线桥,用于在不同总线类型的外设之间实现通信。 B. V) I$ [1 i n* @6 K4 J1 h D1 和 D3 域中的 AHB/APB 总线桥可将 APB3 和 APB4 上的外设分别连接到 AHB3 和AHB4。D2 域中的 AHB/APB 总线桥可将 APB1 和 APB2 上的外设连接到 AHB1。这些AHB/APB 总线桥提供完全同步接口,允许 APB 外设依靠与其所连接的 AHB 无关的时钟来运行。: q1 h. ?- k& H. }% `1 S% A7 g AHB/APB 总线桥还可将 APB1 和 APB2 外设分别连接到 DMA1 和 DMA2 外设总线,而无需通过 AHB1。 AHB/APB 总线桥可将 8 位/16 位 APB 数据转换为 32 位 AHB 数据,具体通过将 8 位/16 位APB 数据复制到 32 位字的三个高位字节/高位半字来实现。* }- Q9 f- T$ K4 y9 C AXI 总线矩阵在其从总线接口上集成 AHB/AXI 总线桥功能。 图 1 中标记为 32 位的主设备接口上的 AXI/AHB 总线桥在矩阵外部。 Cortex-M7 CPU 从其 AHBS 从设备 AHB 提供 AHB/TCM 总线(ITCM 和 DTCM 总线)转换,以允许 MDMA 控制器访问 ITCM 和 DTCM。 2.1.3 域间总线 D2-D1 AHB 该 32 位总线将 D2 域连接到 D1 域中的 AXI 总线矩阵。它使得 D2 域中的总线主设备能够访 问 D1 域中的资源(总线从设备),以及通过 D1-D3 AHB 间接访问 D3 域中的资源(总线从 设备)。 D1-D2 AHB% |: v, Y- C6 E: O% Z: d 该 32 位总线将 D1 域连接到 D2 域 AHB 总线矩阵。它使得 D1 域中的总线主设备能够访问+ f u0 l# w( u8 J7 X$ p- m, X D2 域中的资源(总线从设备)。 存储器和总线架构 RM0433' {# l# x4 r; z7 u3 l: ] 98/3019 文档 ID 029587 Rev 1 [English Rev 3] D1-D3 AHB7 L4 {4 m2 l" A) m4 i7 Z 该 32 位总线将 D1 域连接到 D3 域 AHB 总线矩阵。它使得 D1 域中的总线主设备能够访问, }, |2 q3 r) a0 n, Q# X D3 域中的资源(总线从设备)。 D2-D3 AHB5 t) L) p9 Y& `) Z- o) G 该 32 位总线将 D2 域连接到 D3 域 AHB 总线矩阵。它使得 D2 域中的总线主设备能够访问 D3 域中的资源(总线从设备)。1 \( \' o5 D+ N0 ]6 R2 } , c' M) @) Z; n% r( E, p0 _/ J 2.1.4 CPU 总线' }$ f+ D/ x" q& W( O0 v Cortex ® -M7 AXIM 总线/ T3 C% v h7 s; H Cortex ® -M7 CPU 使用 64 位 AXIM 总线访问所有存储器和外设(ITCM、DTCM、AHB2 外设除外),同时由于寻址不兼容性,AHB1、APB1 和 APB2 外设也排除在外。6 a% g9 o% N, S6 E, |' W 该 AXIM 总线将 CPU 连接到 D1 域中的 AXI 总线矩阵。% O7 o, x0 [; }; J$ W0 t Cortex ® -M7 ITCM 总线 Cortex ® -M7 CPU 使用 64 位 ITCM 总线从 ITCM 中获取指令和访问数据。 Cortex ® -M7 DTCM 总线, l1 { c: D. @/ d+ H; B# R' s8 s Cortex ® -M7 CPU 使用 64 位 DTCM 总线访问 DTCM 中的数据,而且也可以从其中获取指令。 Cortex ® -M7 AHBS 总线+ C* Q: T/ X) a$ r5 }% t Cortex ® -M7 CPU 使用 32 位 AHBS 从总线以允许 MDMA 控制器访问 ITCM 和 DTCM。 Cortex ® -M7 AHBP 总线 Cortex ® -M7 CPU 使用 32 位 AHBP 总线通过 D2 域中的 AHB 总线矩阵访问 AHB1、AHB2、. |: L7 q' `3 r APB1 和 APB2 外设。 * {" {8 e) Y. f8 I& E- f & ? r+ s7 t: b2 e* n 0 r3 m: h) X% b, p6 l ......................... 阅读更多内容,请下载文档 ; }% g" J& ?+ w: p2 \5 o; }% L O; k8 C; A' G. G" F& L4 { |

| 谢谢破总分享知识 |

| 谢谢楼主的分享 |

实战经验 | 关于STM32H7使用LL库生成ADC代码工作异常问题说明

实战经验 | 关于STM32H745的MC SDK电机控制工程问题的解决办法

【H745I GUI】1.GreenHouse 灯光控制

【Wio Lite AI视觉开发套件】+移植TensorFlow Lite

STM32H745I-DISCO脉冲宽度调制(PWM)

STM32H745I-DISCO串口通信,输入输出

拷打cubemx【002】——自定义还需基于芯片的工程

STM32硬件结构学习

STM32中BOOT的作用

STM32H7的TCM,SRAM等五块内存基础知识

微信公众号

微信公众号

手机版

手机版