|

1、针对不同的目标应用,STM32MP1完全走了一个不同的道路。通常在ARM-A7系列以至ARM-A5x系列的芯片都是以Linux内核的开发为主,ARM-Mx内核为辅助。但是ST在M系列的积累,在STM32MP1就展示出了更大的灵活性。从显示驱动的支持看,HDMI,MIPI,LCD直接驱动都包含,那么无论是Linux内核Ax或者Mx系列,这些外设都是可以直接访问的,在外设的选择上,经济型的匹配上都赋予了更大的灵活性。但前提是整个硬件构建都是可以用户定制的。 2、前面已经简单描述了多核启动的基本逻辑,那么在硬件上是如何配合实现的,需要在以下综合考虑。具体,是否还有其他的加载顺序,那么,基于M4内核与Ax内核分离的情况下,其实是可以有更多选择的,但是,作为ST官方设计了这样的架构,那么沿用标准流程是最便捷可靠的方式。 至少需要按照以下顺序实现,电源设计,封装选择,时钟管理,初始化和启动模式,以及调试管理。 2.1 -- 电源设计:1 ?! U1 _3 K8 R! ~5 S% M! _$ J U

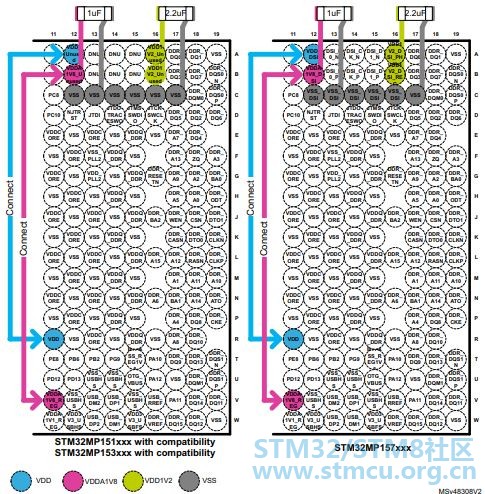

上图展示了各个内核供电轨,内核1.18~1.25V,主IO供电1.71~3.6V,USB驱动3.1~3.6V,还有视频接口,RTC驱动,以及Vbat电池供电1.20~3.6V,参考电压Vref等不同的范围,需要对照手册逐个核对这些供电引脚需要,合理选择PMIC电源管理芯片,以满足要求。 针对不同的供电和引脚,需要有不同的解耦电容,从100nF到2.2uF不等。9 p$ I4 n m2 I$ S! E; G5 z0 M 启动时,起始电压可以低至1.71V。 2.2 --封装设计。. J7 P# L& P, k 封装尺寸从10x10到18x18的LFBGA封装,提供GPIO从98到176个,在不同的封装,尽量保持了兼容性,如下图6 {3 n# m! E/ o5 o' @) t1 W

在STM的CubeMX中具有这样的引脚配置工具,实现直观的设计和配置。 , r& S0 ?/ G& P3 X3 l9 K: J8 H 2.3 时钟 相比电源设计更多样的是时钟,至少包括HSI,CSI内部高低速时钟,HSE外部高速时钟,PLL for USB/DSI等。外部的辅助时钟,32kHZ,32.768kHz等这些常见的低功耗时钟。 以HSE OSE时钟为例,可以由外部提供时钟信号也可以直接从晶振获得(8~50MHz)5 f' _& w) O' R6 Z& y Y. _6 b

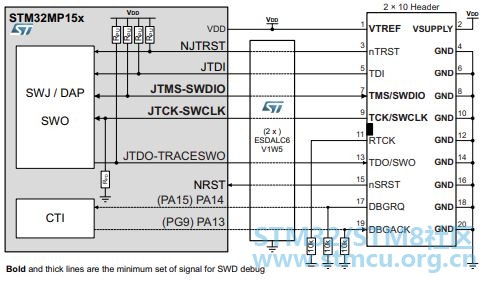

2.4 上贴已经介绍过启动设置的boot引脚,对于生产模式,这个引脚可以固定引接或者用0值电阻短接,根据设置选择启动位置,常见的设置不是从SD卡启动,如本次测试的开发板,而是从外存如NORFlash或者NANDFlash启动。对于启动影像一般足够容纳一个精简的系统kernal,外部设备其实可以在加载内核的适合从外部设备再次加载。这个不同于台式计算机多数从大容量外存加载的过程。 这个开发板只选择了Boot0和Boot2的选择开关,Boot1已经直接置零了。软起动也是需要访问这个引脚获得数据,写入 SYSCFG_BOOTR寄存器中,软起动后,不再访问引脚,电流为零,即使带电拨动选择开关也不改变 SYSCFG_BOOTR寄存器的数值了。/ d8 L* y. a( Z 2.5 调试接口 通常JTAG或者SWD调试接口需要引出,上拉下拉电阻内置,通过指定寄存器置位来确定。典型的设置如下图

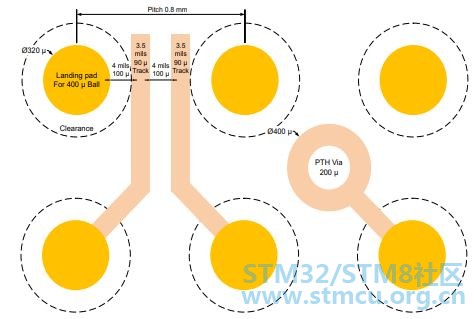

其中对于SWD只支持M4内核。/ P, e' W/ n! T, O3 Q: }$ `' O5 l 3. 硬件设计导则 3.1 PCB设计至少4层板,设置独立的电源平面和接地平面。通孔设计要根据导则选择,如下图- I3 q3 c4 m& B7 U

3.2 输入输出接口IO设置需要进行调试,并正确对OSPEEDR置位,SYS CFG寄存器的IO补偿需要置位。 3.3 未使用的IO引脚要设置为无用并正确连接,不能浮空。; i& U# m/ A% L4 g 3.4 外设引接需要正确匹配传输线,和电平转换,如下图中对于DSI显示的差分传输线设计,# ?, i3 x# i5 m# f* ?5 S

# \/ c/ w! s' |1 V! ~2 Q 3.5 实际上,本开发板在传输线平衡上也做良好的设计,注意下图中弯折的传输线,是为了保证等效长度均衡的方法,在很多开发板上,都采用了最近连接线的设计,对于高速板的设计,具有更高的要求。3 X$ J8 v. U @

/ o9 N& V8 v5 _- g |

基于STM32MP1和STM32MP2在嵌入式Linux平台上部署有效的安全保护机制

利用STM32MP1和STM32MP2为嵌入式Linux提供有效的安全措施:供当今决策者参考的3条宝贵经验

STM32MP1 WiFi连接

【STM32MP157】从ST官方例程中分析RPMsg-TTY/SDB核间通信的使用方法

【STM32MPU 安全启动】 TF-A BL2 TrustedBoot原理学习

《STM32MPU安全启动》学**结

《STM32MPU安全启动》学习笔记之optee 如何加载CORTEX-M核和使能校验

《STM32MPU安全启动》学习笔记之TF-A BL2校验optee和uboot的流程以及如何使能

《STM32MPU 安全启动》课程学习心得+开启一扇通往嵌入式系统安全领域深处的大门。

《STM32MPU安全启动》 课程学习心得

微信公众号

微信公众号

手机版

手机版