.png) STMCU小助手

发布时间:2021-8-6 10:47

STMCU小助手

发布时间:2021-8-6 10:47

|

概览 现代电子系统中,由于“软”错误引起的系统故障比永久性硬件失效引起的系统故障要更多。“软”错误是指可以恢复的故障或者失效。这一类错误容易发生在寄存器,RAM等上面,由于受到电磁干扰或者封装材料中的α粒子,宇宙射线等的影响而造成位值翻转。针对这个问题,可以在硬件上加奇偶校验,ECC电路来进行检测。 0 }/ m$ a; k2 G# i; P$ D STM32H7系列MCU的Flash,SRAM和CACHE都支持ECC的功能。在本文中,主要介绍SRAM ECC这部分功能以及应用中的注意事项。, g2 A1 j8 n$ v/ e- H$ S. S ' C) z9 D( M* ^ - s& o- O7 o: L% a , c6 @5 \( {0 S- M9 Z5 j RAMECC外设 在STM32H7系列MCU中,有一个叫RAMECC的外设,它是一个RAM ECC Monitor。RAMECC提供了一个接口给应用程序来检测当前RAM的ECC状态,以及当发生ECC错误后执行相应的恢复或者报错程序。# m% J' F4 w h' J7 { 5 `7 A3 U( _. n, i/ |% W& t9 A 6 c' P' h1 d' \ STM32H7的RAM ECC支持纠正单比特的错误和检测双比特的错误。对于AXI SRAM和TCM RAM,每64位数据附加8位ECC码;其他的32位总线的SRAM,每32位数据附加7位ECC码。 在对SRAM进行写操作的时候,硬件自动计算并保存ECC的值,在对SRAM进行读操作或者非对齐的写操作(读-改-写)的时候会自动进行校验,并且出错的地址和数据可以通过寄存器读出。 6 N! v; s: Z* t( l4 L2 y4 y4 Z STM32H7的RAM ECC功能的实现可以分成两个部分:RAM ECC Controller和RAM ECC Monitor单元,如下图所示。

! r" ^& d% y# }2 ` 关于ECC Controller3 e8 j3 e2 a" B- h) `' \' s D% L STM32H7的SRAM分成AXI SRAM,SRAM1,SRAM2,SRAM3,SRAM4,数据TCM RAM,指令TCM RAM和备份SRAM等几块。每个RAM块分别对应一个ECC Controller。 0 y' v! S; V4 S, L9 E/ ~# t: }, c& ~ f ECC Controller始终处于使能状态。它负责ECC代码的计算存储,比较和错误检测,可以完成单比特错误纠正和双比特错误检测的功能。/ r; x: n, K7 T8 z - O! w4 F, v) t- ?9 C3 l- v 关于ECC Monitor STM32H7一共有三个ECC Monitor,各负责一个域。ECC Monitor接收来自ECC Controller的诊断事件,并根据寄存器的配置产生对应的中断信号。4 }2 {3 }7 S4 Q% U( d' n5 U' W 2 D3 O% B7 E- m4 B' u ECC Controller与ECC Monitor之间的映射关系见下图。例如D1的RAMECC Monitor单元,一共有5个通道,每个通道对应一个SRAM块的ECC controller。每个通道都有自己的一组寄存器,图中的Address offset就是寄存器组的偏移地址。如果要打开AXI SRAM的ECC Monitor单元,使得当检测到AXI SRAM的ECC错误时产生对应的中断,就需要操作AXI SRAM对应的寄存器组。

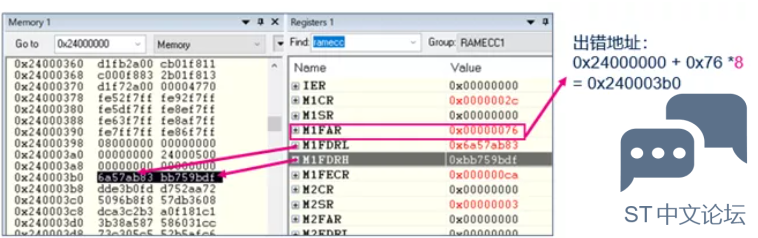

/ M- x+ L/ O( v6 Z6 r1 l FAR和FDR寄存器 RAMECC支持单比特ECC错误中断,双比特ECC错误中断和非对齐写操作(Byte Write)引起的ECC中断。在RAMECC的IER和CR寄存器中可以分别配置和使能这些中断。在SR寄存器中可以查看这些中断的状态。这几个寄存器的操作都一目了然,这里想说明的是另外两个寄存器:出错地址寄存器FAR和出错数据寄存器FDR。0 w- B+ ]) S: W, F$ b9 w6 s E - G4 j% W# R' E4 e5 Q 使能了CR寄存器里的ECCELEN位后,当ECC错误(单比特/双比特错误)发生后,出错的地址和数据就会被锁定到FAR和FDR寄存器里。 FAR寄存器里保存的是相对地址。实际出错地址的计算公式如下:* v0 ~- e9 V$ K4 q 实际的出错地址= SRAM的起始地址 + FAR寄存器的值 * N(N=4或者8)。 t4 E- i6 p* ]7 {1 f' ~; } }" ]7 o( v FDR寄存器有两个,对于64位总线的SRAM数据,FDRL寄存器保存低4字节的数据,FDRH保存高4字节的数据。对于32位总线的SRAM数据,数据保存在FDRL寄存器中,FDRH的值为0。0 n0 [9 S7 W4 r: z) p # P% s" t- w. C * ^2 A1 h3 \. M% m 我们可以看下面两个例子:* u- l; r n3 U5 ]* m- B 例子1:使能AXI-SRAM对应的Monitor功能(如何使能请参考STM32H7CUBE库中的RAMECC_ErrorCount例程)。上电后AXI-SRAM先不初始化,然后直接进行读操作就会触发ECC错误。这时候我们在调试状态下查看FAR和FDR的值,见下图。$ X! ?- e0 ?; c4 n2 z$ T7 U

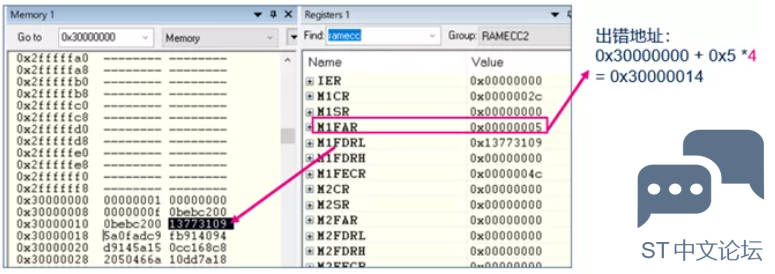

0 c. H( E6 N2 I7 f1 f 这里因为AXI-SRAM是64位总线接口,所以计算实际出错地址时,N的值是8。 . _2 W, f0 t f$ Y5 r, ^+ w, ? V' i& ]2 s, q X! _! H 例子2:使能SRAM1(0X30000000)对应的Monitor功能。上电后不进行初始,然后直接进行读操作就会触发ECC错误。这时候我们在调试状态下查看FAR和FDR的值,如下图。7 }4 N9 \ _5 d

4 j/ b& h3 c' i% A3 ^ 7 A3 a7 |- \; f; U7 `- T* i 因为SRAM1是32位总线接口,所以这时N的值是4。 # C! V) u, S3 n7 u+ c% C , y6 b, N E4 \. ?0 L; N- l( D6 w / D( L" D- j0 ^" w5 N6 N, K 在应用中如何正确使用RAM ECC/ R$ M' L( b1 |) f; ? 在使用支持ECC的RAM时,一定要注意的是要对RAM进行初始化,否则就可能会报ECC错误。就像我们在上一节的实验中做的那样,通过不初始化的做法,我们可以模拟出ECC错误。在AN5342中给出了建议的初始化步骤。2 ?* _7 L$ \6 p6 g; [2 M 对于单比特的ECC错误可以在读出的过程中自动纠正,但仅仅只是读出的数据是正确的,为了防止错误累积,导致从单比特的错误变成双比特的错误,可以在检测到单比特错误后,将正确的值写回到SRAM中去。这里有两种方式,一种如果原本SRAM中保存的值在Flash有备份,那么直接将Flash中的值再次写到SRAM中去;或者利用前面提到的FAR和FDR寄存器将正确的值写回SRAM中。2 n. k. C5 Q) s, D, t- ~8 d 5 C& l/ }. Z- q1 ~ 通过周期性的ECC检测来主动发现SRAM的故障也是提高系统可靠性的方法。ECC检测可以通过读SRAM的值来进行。检测不需要一次性完成,可以在系统空闲时,分段的对SRAM进行检测。请参考AN5342了解更多的细节。& O6 |" f g5 ~2 N |

【Wio Lite AI视觉开发套件】+移植TensorFlow Lite

STM32H745I-DISCO脉冲宽度调制(PWM)

STM32H745I-DISCO串口通信,输入输出

拷打cubemx【002】——自定义还需基于芯片的工程

STM32硬件结构学习

STM32中BOOT的作用

STM32H7的TCM,SRAM等五块内存基础知识

STM32H7的TCM,SRAM等五块内存基础知识

简单了解一下STM32H7的BDMA

有奖预约 | STM32H7R7基于RT-Thread RTOS的智能终端GUI解决方案

微信公众号

微信公众号

手机版

手机版

您好,但是参考了各方资料,STM32H7系列的RAM区ECC功能无法关闭,这就导致无法查看RAM区原始数据,特别是对单bit错误的纠正功能没有手段去验证,这块能赐教下吗