.png) STMCU小助手

发布时间:2021-8-6 10:47

STMCU小助手

发布时间:2021-8-6 10:47

|

概览 现代电子系统中,由于“软”错误引起的系统故障比永久性硬件失效引起的系统故障要更多。“软”错误是指可以恢复的故障或者失效。这一类错误容易发生在寄存器,RAM等上面,由于受到电磁干扰或者封装材料中的α粒子,宇宙射线等的影响而造成位值翻转。针对这个问题,可以在硬件上加奇偶校验,ECC电路来进行检测。 STM32H7系列MCU的Flash,SRAM和CACHE都支持ECC的功能。在本文中,主要介绍SRAM ECC这部分功能以及应用中的注意事项。 RAMECC外设 在STM32H7系列MCU中,有一个叫RAMECC的外设,它是一个RAM ECC Monitor。RAMECC提供了一个接口给应用程序来检测当前RAM的ECC状态,以及当发生ECC错误后执行相应的恢复或者报错程序。 STM32H7的RAM ECC支持纠正单比特的错误和检测双比特的错误。对于AXI SRAM和TCM RAM,每64位数据附加8位ECC码;其他的32位总线的SRAM,每32位数据附加7位ECC码。 在对SRAM进行写操作的时候,硬件自动计算并保存ECC的值,在对SRAM进行读操作或者非对齐的写操作(读-改-写)的时候会自动进行校验,并且出错的地址和数据可以通过寄存器读出。 STM32H7的RAM ECC功能的实现可以分成两个部分:RAM ECC Controller和RAM ECC Monitor单元,如下图所示。

关于ECC Controller STM32H7的SRAM分成AXI SRAM,SRAM1,SRAM2,SRAM3,SRAM4,数据TCM RAM,指令TCM RAM和备份SRAM等几块。每个RAM块分别对应一个ECC Controller。 ECC Controller始终处于使能状态。它负责ECC代码的计算存储,比较和错误检测,可以完成单比特错误纠正和双比特错误检测的功能。 关于ECC Monitor STM32H7一共有三个ECC Monitor,各负责一个域。ECC Monitor接收来自ECC Controller的诊断事件,并根据寄存器的配置产生对应的中断信号。 ECC Controller与ECC Monitor之间的映射关系见下图。例如D1的RAMECC Monitor单元,一共有5个通道,每个通道对应一个SRAM块的ECC controller。每个通道都有自己的一组寄存器,图中的Address offset就是寄存器组的偏移地址。如果要打开AXI SRAM的ECC Monitor单元,使得当检测到AXI SRAM的ECC错误时产生对应的中断,就需要操作AXI SRAM对应的寄存器组。

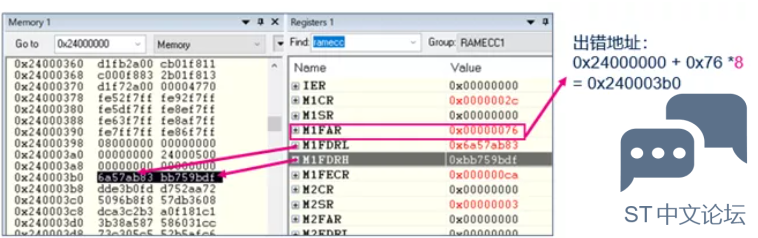

FAR和FDR寄存器 RAMECC支持单比特ECC错误中断,双比特ECC错误中断和非对齐写操作(Byte Write)引起的ECC中断。在RAMECC的IER和CR寄存器中可以分别配置和使能这些中断。在SR寄存器中可以查看这些中断的状态。这几个寄存器的操作都一目了然,这里想说明的是另外两个寄存器:出错地址寄存器FAR和出错数据寄存器FDR。 使能了CR寄存器里的ECCELEN位后,当ECC错误(单比特/双比特错误)发生后,出错的地址和数据就会被锁定到FAR和FDR寄存器里。 FAR寄存器里保存的是相对地址。实际出错地址的计算公式如下: 实际的出错地址= SRAM的起始地址 + FAR寄存器的值 * N(N=4或者8)。 FDR寄存器有两个,对于64位总线的SRAM数据,FDRL寄存器保存低4字节的数据,FDRH保存高4字节的数据。对于32位总线的SRAM数据,数据保存在FDRL寄存器中,FDRH的值为0。 我们可以看下面两个例子: 例子1:使能AXI-SRAM对应的Monitor功能(如何使能请参考STM32H7CUBE库中的RAMECC_ErrorCount例程)。上电后AXI-SRAM先不初始化,然后直接进行读操作就会触发ECC错误。这时候我们在调试状态下查看FAR和FDR的值,见下图。

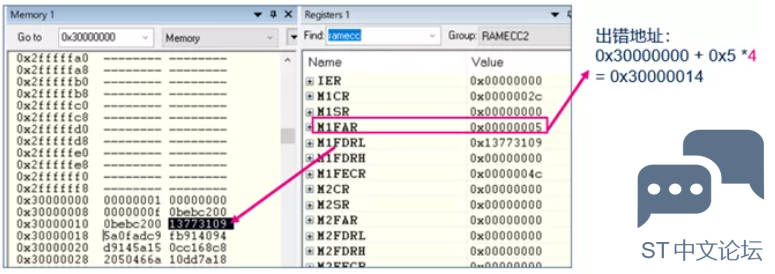

这里因为AXI-SRAM是64位总线接口,所以计算实际出错地址时,N的值是8。 例子2:使能SRAM1(0X30000000)对应的Monitor功能。上电后不进行初始,然后直接进行读操作就会触发ECC错误。这时候我们在调试状态下查看FAR和FDR的值,如下图。

因为SRAM1是32位总线接口,所以这时N的值是4。 在应用中如何正确使用RAM ECC 在使用支持ECC的RAM时,一定要注意的是要对RAM进行初始化,否则就可能会报ECC错误。就像我们在上一节的实验中做的那样,通过不初始化的做法,我们可以模拟出ECC错误。在AN5342中给出了建议的初始化步骤。 对于单比特的ECC错误可以在读出的过程中自动纠正,但仅仅只是读出的数据是正确的,为了防止错误累积,导致从单比特的错误变成双比特的错误,可以在检测到单比特错误后,将正确的值写回到SRAM中去。这里有两种方式,一种如果原本SRAM中保存的值在Flash有备份,那么直接将Flash中的值再次写到SRAM中去;或者利用前面提到的FAR和FDR寄存器将正确的值写回SRAM中。 通过周期性的ECC检测来主动发现SRAM的故障也是提高系统可靠性的方法。ECC检测可以通过读SRAM的值来进行。检测不需要一次性完成,可以在系统空闲时,分段的对SRAM进行检测。请参考AN5342了解更多的细节。 |

STM32H750 外扩 QSPI FLASH 跑 2 小时就死机?LAT1151 官方根治方案

STM32H723 多通道序列 ADC 启动不了?寄存器操作必须等 ADRDY 就绪

经验分享 | STM32H7 LPTIM+DMAMUX+BDMA应用演示

经验分享 | STM32H7系列ADC DMA传输异常案例分享

经验分享 | STM32H7 MDMA 与通用DMA的联动传输示例

STM32H750 基于 Keil 制作 QSPI 外部 Flash 下载算法 全流程实操指南

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

微信公众号

微信公众号

手机版

手机版

您好,但是参考了各方资料,STM32H7系列的RAM区ECC功能无法关闭,这就导致无法查看RAM区原始数据,特别是对单bit错误的纠正功能没有手段去验证,这块能赐教下吗