5.1 初学者重要提示

( A* P( I, ~% W& c/ x b! | 学习本章节后,务必学习STM32参考手册中MAC章节的基础知识讲解,非常重要。

1 B# r4 l, f, w! { x 实际项目中,关于MAC的配置问题,需要大家学习我们论坛网友发的这个帖子。3 q: o! e; I$ p0 G0 Q: R2 Y

: c) h. {5 |$ q. W. g

5.2 什么是MAC

) L, W5 s' `* D- Q- j, t7 Q媒体访问控制(MAC,Media Access Control),又称作介质访问控制,简称MAC,是局域网中数据链路层的下层部分,提供地址及媒体访问的控制方式,使得不同设备或网络上的节点可以在多点的网络上通信,而不会互相冲突,上述的特性在局域网中格外重要。早期网络发展时以MAC判别各个网络接口的位置,但后来互联网发展后,才有IP的制定与使用。若只是两台设备之间全双工的通信,因为两台设备可以同时发送及接收数据,不会冲突,因此不需要用到MAC协议。

# a9 h5 g! N. z6 E- q V! \% _- a0 d9 x z6 l

媒体访问控制MAC子层负责解决与媒体接入有关的问题,在物理层的基础上进行无差错的通信。" ?, Y8 Y! d3 _3 M

0 Z/ }% m! V! JMAC子层是网络与设备的接口,它从网络层接收数据帧,然后通过媒体访问规则和物理层将数据帧发送到物理链路上。它也从物理层接收数据帧,再送到网络层。总的来说,MAC有三大功能:

4 y/ M" t: c$ u# J2 @: g; p! |& \; n3 p3 S$ R

决定节点何时发送数据包。

# ~0 ?' A! x# `3 ^ 将数据帧发送到物理层,然后发送到物理链路。0 ]$ d# H) N1 I- [4 K ~8 U) Y

从物理层接收数据帧,然后送给网络层处理。

. t2 o+ o/ I2 R6 D1 E其中最重要的是第一点:决定节点何时发送数据包。对于每一种媒体访问控制技术,用来控制节点发送时机的规则叫做媒体访问规则。局域网上的节点不能想要发送数据就发送,节点只能在轮到它的时候才发送。

6 I% m- L. b4 O5 k

; x/ i- z2 a/ C4 J: o: p5 [5.3 MAC地址

. @" `* @2 D$ F6 {/ t {/ G" mMAC地址,又称为物理地址、硬件地址,用来定义网络设备的位置。在OSI模型中,第三层网络层负责 IP地址,第二层数据链路层则负责 MAC地址。因此一个主机会有一个MAC地址,而每个网络位置会有一个专属于它的IP地址。

8 m# ] _) M$ ]* e( \

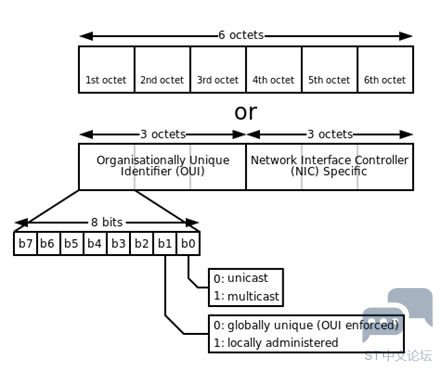

' T" o, N: O% Y3 `: J+ z" V9 _MAC地址长度是48bit(6字节),由16进制的数字组成,分为前24位和后24位:) J4 F9 c9 t" |& ?, I, c

. @. Q0 a$ |$ F9 I 前24位叫做组织唯一标志符(Organizationally Unique Identifier,即OUI),是由IEEE的注册管理机构给不同厂家分配的代码,区分了不同的厂家。

, c+ X7 n( g5 X% X7 I, _ 后24位是由厂家自己分配的,称为扩展标识符。同一个厂家生产的网卡中MAC地址后24位是不同的。

$ ?' C4 Y9 S+ _: l) E( H9 vMAC地址的完整数据格式如下(来自wiki百科):; o, H% d" b3 R( W& V1 S7 `( d

' F# v: ]# p* k# i3 l7 {4 W# J# G0 T# t+ m7 b

% _2 m4 C& g3 d: G: c8 V/ V第一个字节的后两位比较重要:

7 M3 \1 O1 v) Z; G/ L% k9 B } n* o2 l4 i% I3 Z5 e* y

b0 = 0:表示MAC单播地址。

7 h8 N) a: R8 h# C* n' ~/ X1 H" F3 H' T

b0 = 1 : 表示MAC组播地址。

4 c- a& C J- Z7 Z' O4 [6 K

) f- D; C% @) @0 }7 I1 gb1 = 0:表示OUI分配的全球唯一MAC地址。

' l7 O; z Q& X- t( Z+ r( {: A- {( ^

, {+ b" N8 Z" y: e- T4 _" Yb1 = 1:表示用于本地管理的MAC地址。

! E# K+ I- n) y$ E- @' F- ?/ x) A& H u- {

为了更好地理解,举几个例子:2 h* m+ e1 k* v9 k

6 h" y7 P5 N$ N0 @9 A1 k

00:xx:xx:xx:xx:xx是MAC单播地址。$ f j: `( W* v7 I8 b

01:xx:xx:xx:xx:xx是MAC组播地址。

) }# g- Q; S/ V. x 01:00:5e:xx:xx:xx是IPv4组播地址。; T, l0 ]. l6 r9 T( N4 Y3 l: r; v

ff:ff:ff:ff:ff:ff则作为广播地址。8 L9 |1 s# l+ K Z9 Z" M9 k5 V

00:50:c2:xx:xx:xx 是意法半导体的MAC地址。

' o7 ]5 I8 s' ]+ A& u( H: P' s( f6 n5.4 STM32自带MAC基础知识

$ \& V7 k, @% Z# @1 v关于STM32自带的MAC部分,STM32参考手册中写的晦涩难懂,特别是中文翻译版本,逻辑混乱,如果可以的话,建议大家看英文版。7 x* {( p+ g7 l \

3 v4 G. J" G. J! Y$ H( b/ b

STM32参考手册中对MAC的讲解主要分为三部分:

, t x7 J L' c- b1 s0 {

* d( a1 e A7 D. {& n! P& D, d MAC的接口MII和RMII。

5 f. C( v2 g3 v# G/ J# G) L参考手册中对这一部分讲解的比较详细,也比较容易理解,建议初学者务必读一读。我们这里就不将其复制粘贴过来了。

7 v0 F: }) z* M5 |9 N% U( ~* t, e) d5 x! ?! h9 }2 x

MAC802.3帧格式,帧发送,帧接收等方面的讲解。

3 G2 a4 q6 E+ U( A! h, v3 A& L这一个部分知识点理解起来比较困难,配合下一章节的底层驱动就好理解了。

P8 I9 ^; t. R2 _

2 g3 X7 u& D1 n! |# T/ S) [- ~ MAC的DMA收发方式控制。

$ {8 c+ p8 h2 x k手册中给出了DMA方式的发送和接收的初始化顺序,在下一章节讲解底层驱动的时候结合驱动代码会理解的更好,建议初学者也读一遍。

) w( x+ T) l9 u( Z( i# q8 E* I7 w

5 i/ ]) j8 d5 M5.5 以太网PHY基础知识

( B2 }0 s' V0 \仅有STM32自带的MAC还不能做网络通信,还需要外接以太网PHY芯片才可以,如同RS485通信一样,仅有一个串口是不行的,还需要外接RS485的PHY芯片。# z! h1 `( o# [

; M( _, y0 L1 P+ M( s" I9 APHY(Port Physical Layer),可称之为端口物理层,是一个对OSI模型物理层的简称。现在常用于STM32的有DP83848,LAN8270,DM9161/9162等。这些PHY芯片都大同小异,基本寄存器都是一样的,只有扩展寄存和厂商专门设置的寄存器不同。如果用户将其中一个PHY驱动成功了,驱动另一个也是非常方便的,下面是DP83848和DM9161/9162的基本寄存器和扩展寄存器:

5 B) G1 W$ Z O2 R r) L- y$ n: x1 N6 m, T6 J9 r; D6 ~& ]' Z

- /* DP83848C and DM9161 PHY Registers is the same */2 x" y/ \, l [$ E2 j9 B6 X& U, G# H

- #define PHY_REG_BMCR 0x00 /* Basic Mode Control Register */

" l$ d3 V3 l9 l8 } - #define PHY_REG_BMSR 0x01 /* Basic Mode Status Register */$ ^& j2 x1 S8 p* N0 l7 m2 `

- #define PHY_REG_IDR1 0x02 /* PHY Identifier 1 */5 d* q" ~/ }4 F* x

- #define PHY_REG_IDR2 0x03 /* PHY Identifier 2 */1 C" J. e. B. Z1 n

- #define PHY_REG_ANAR 0x04 /* Auto-Negotiation Advertisement */% x% c8 D. N; E6 k+ \/ Q

- #define PHY_REG_ANLPAR 0x05 /* Auto-Neg. Link Partner Abitily */

6 [' O# ~/ P/ ?9 P5 m3 i1 K - #define PHY_REG_ANER 0x06 /* Auto-Neg. Expansion Register */

3 a- |; C% c/ E: }5 t - #define PHY_REG_ANNPTR 0x07 /* Auto-Neg. Next Page TX .DM9161 NO */8 T) E5 d9 `4 j& {0 R( v

) G! ? [+ p% C/ X& q S! i0 X4 y8 |- /* Register BMCR bit defination */

7 v% n0 ]9 l4 D - #define PHY_FULLD_100M 0x2100 /* Full Duplex 100Mbit */

, }7 f1 v8 @1 B" |' M - #define PHY_HALFD_100M 0x2000 /* Half Duplex 100Mbit */

3 z$ S7 b4 Z2 b( K# w - #define PHY_FULLD_10M 0x0100 /* Full Duplex 10Mbit *// j% Y6 b0 h5 B2 s) W

- #define PHY_HALFD_10M 0x0000 /* Half Duplex 10MBit */3 y- A. G6 ~5 {- [

- #define PHY_AUTO_NEG 0x1000 /* Select Auto Negotiation */- K# L% T6 a; v J/ P7 M

7 P; o$ L* ]9 L i u- E% }% v. Y- /* PHY Extended Registers only for DP83848C */( ^0 y3 w2 @' ?

- #define PHY_REG_STS 0x10 /* Status Register */

( Y# r- ^( k f! D - #define PHY_REG_MICR 0x11 /* MII Interrupt Control Register */

/ G' G, B( k% m( D" q - #define PHY_REG_MISR 0x12 /* MII Interrupt Status Register */

2 g1 R" i8 R: R1 U! \1 S2 o) x - #define PHY_REG_FCSCR 0x14 /* False Carrier Sense Counter */- f" X* c! F6 c, m/ s

- #define PHY_REG_RECR 0x15 /* Receive Error Counter */

7 c6 U/ D+ k/ y4 [. O9 k# \. p' s - #define PHY_REG_PCSR 0x16 /* PCS Sublayer Config. and Status */

5 q) q8 f4 y* }- x8 A5 H - #define PHY_REG_RBR 0x17 /* RMII and Bypass Register */8 v9 k3 v) Q3 [3 \: q9 a& ]# k

- #define PHY_REG_LEDCR 0x18 /* LED Direct Control Register */$ a) d2 z: x3 y( J

- #define PHY_REG_PHYCR 0x19 /* PHY Control Register */1 u1 e8 F- }% g1 g

- #define PHY_REG_10BTSCR 0x1A /* 10Base-T Status/Control Register */

: U# R. u- D3 i+ a - #define PHY_REG_CDCTRL1 0x1B /* CD Test Control and BIST Extens. *// N* Y6 {2 I+ {: g' {/ H

- #define PHY_REG_EDCR 0x1D /* Energy Detect Control Register */

{7 I7 y/ p/ g3 T1 U - , y g# T1 ]1 \2 F1 ]4 }- t* d( d" U

- /* PHY Extended Registers only for DM9161 */6 [7 T3 i5 `# j" e1 k9 r

- #define PHY_REG_DSCR 0x10 /* Specified Congfiguration Register */

9 O( O# m. }1 N2 ]3 \' z - #define PHY_REG_DSCSR 0x11 /* Specified Congfiguration and Status Register */* M8 d$ e& [( B/ x# a* b: u

- #define PHY_REG_10BTCSR 0x12 /* 10Base-T Status/Control Register */* ?, b: s4 r- [: a

- #define PHY_REG_PWDOR 0x13 /* Power Down Control Register */ ?6 t# x: i ^6 z

- #define PHY_REG_CONGFIG 0x14 /* Specified Congfig Register */: D# U8 c' A5 Q" H2 S, [$ b6 z

- #define PHY_REG_INTERRUPT 0x15 /* Specified interrupt Register */

q6 G! x' O6 i) p! @8 ]; k - #define PHY_REG_SRECR 0x16 /* Specified Receive Error Counter */

$ _! ~" y9 t8 m# b" p - #define PHY_REG_DISCR 0x17 /* Specified Disconnect Counter Register */! n" u; Z9 e5 v7 X

- #define PHY_REG_RLSR 0x18 /* Hardware reset latch state Register */) W4 G: c! T% J' O X h8 T

- #define PHY_REG_PSCR 0x1D /* Power Saving control register */

. y9 X9 j3 d8 F5 Z2 a对于初学者来说,了解这些知识点就够了,具体如何配置这些寄存器会在下个章节讲解。1 c6 v+ c+ V3 g- H4 c9 G @

) ^4 N0 _% Q5 t; i2 ^5.6 总结/ c$ {+ ^& ~" \3 |

本章节就为大家讲解这么多,主要是为下章节的讲解做个铺垫。学习完毕本章节后,务必将STM32参考手册中MAC章节读一遍。2 S' Z1 e) ^! B

2 U$ a3 z& X0 ]- I5 e4 P8 k

! y$ u9 k) {# U% V7 L; `0 k5 A. q3 m c9 ^- C9 L0 n# D8 w, r' v

|

.png) STMCU小助手

发布时间:2021-12-27 17:00

STMCU小助手

发布时间:2021-12-27 17:00

微信公众号

微信公众号

手机版

手机版