01. 概述

CM4 内核支持 256 个中断,其中包含了 16 个内核中断和 240 个外部中断,并且具有256 级的可编程中断设置。但 STM32F4 并没有使用 CM4 内核的全部东西,而是只用了它的一部分。

STM32F40xx/STM32F41xx 总共有 92 个中断,STM32F42xx/STM32F43xx 则总共有 96 个中断,STM32F40xx/STM32F41xx 的 92 个中断里面,包括 10 个内核中断和 82 个可屏蔽中断,具有16级可编程的中断优先级,而我们常用的就是这82个可屏蔽中断。

02. 结构体声明

core_cm4.h文件中

- /** \brief Structure type to access the Nested Vectored Interrupt Controller (NVIC).

- */

- typedef struct

- {

- __IO uint32_t ISER[8]; /*!< Offset: 0x000 (R/W) Interrupt Set Enable Register */

- uint32_t RESERVED0[24];

- __IO uint32_t ICER[8]; /*!< Offset: 0x080 (R/W) Interrupt Clear Enable Register */

- uint32_t RSERVED1[24];

- __IO uint32_t ISPR[8]; /*!< Offset: 0x100 (R/W) Interrupt Set Pending Register */

- uint32_t RESERVED2[24];

- __IO uint32_t ICPR[8]; /*!< Offset: 0x180 (R/W) Interrupt Clear Pending Register */

- uint32_t RESERVED3[24];

- __IO uint32_t IABR[8]; /*!< Offset: 0x200 (R/W) Interrupt Active bit Register */

- uint32_t RESERVED4[56];

- __IO uint8_t IP[240]; /*!< Offset: 0x300 (R/W) Interrupt Priority Register (8Bit wide) */

- uint32_t RESERVED5[644];

- __O uint32_t STIR; /*!< Offset: 0xE00 ( /W) Software Trigger Interrupt Register */

- } NVIC_Type;

STM32F4 的中断在这些寄存器的控制下有序的执行的。只有了解这些中断寄存器,才能方便的使用 STM32F4 的中断。

ISER[8]:ISER 全称是:Interrupt Set-Enable Registers,这是一个中断使能寄存器组。上面说了 CM4 内核支持 256 个中断,这里用 8 个 32 位寄存器来控制,每个位控制一个中断。但是STM32F4 的可屏蔽中断最多只有 82 个,所以对我们来说,有用的就是三个(ISER[0~2]),总共可以表示 96 个中断。而 STM32F4 只用了其中的前 82 个。ISER[0]的 bit0~31 分别对应中断0~31;ISER[1]的 bit0~32 对应中断 32~63;ISER[2]的 bit0~17 对应中断 64~81;这样总共 82 个中断就分别对应上了。你要使能某个中断,必须设置相应的 ISER 位为 1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO 口映射等设置才算是一个完整的中断设置)。具体每一位对应哪个中断,请参考 stm32f4xx.h 里面的第 188 行处。

ICER[8]:全称是:Interrupt Clear-Enable Registers,是一个中断除能寄存器组。该寄存器组与 ISER 的作用恰好相反,是用来清除某个中断的使能的。其对应位的功能,也和 ICER 一样。这里要专门设置一个 ICER 来清除中断位,而不是向 ISER 写 0 来清除,是因为 NVIC 的这些寄存器都是写 1 有效的,写 0 是无效的。

ISPR[8]:全称是:Interrupt Set-Pending Registers,是一个中断挂起控制寄存器组。每个位对应的中断和 ISER 是一样的。通过置 1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写 0 是无效的。

ICPR[8]:全称是:Interrupt Clear-Pending Registers,是一个中断解挂控制寄存器组。其作用与 ISPR 相反,对应位也和 ISER 是一样的。通过设置 1,可以将挂起的中断接挂。写 0 无效。

IABR[8]:全称是:Interrupt Active Bit Registers,是一个中断激活标志位寄存器组。对应位所代表的中断和 ISER 一样,如果为 1,则表示该位所对应的中断正在被执行。这是一个只读寄存器,通过它可以知道当前在执行的中断是哪一个。在中断执行完了由硬件自动清零。

IP[240]:全称是:Interrupt Priority Registers,是一个中断优先级控制的寄存器组。这个寄存器组相当重要!STM32F4 的中断分组与这个寄存器组密切相关。IP 寄存器组由 240 个 8bit的寄存器组成,每个可屏蔽中断占用 8bit,这样总共可以表示 240 个可屏蔽中断。而 STM32F4只用到了其中的 82 个。IP[81]~IP[0]分别对应中断 81~0。而每个可屏蔽中断占用的 8bit 并没有全部使用,而是只用了高 4 位。这 4 位,又分为抢占优先级和响应优先级。抢占优先级在前,响应优先级在后。而这两个优先级各占几个位又要根据 SCB->AIRCR 中的中断分组设置来决定。

03. 中断分组

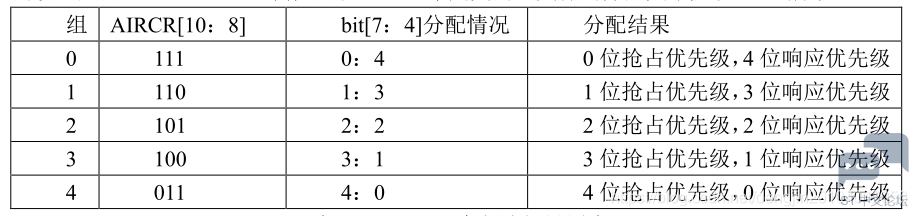

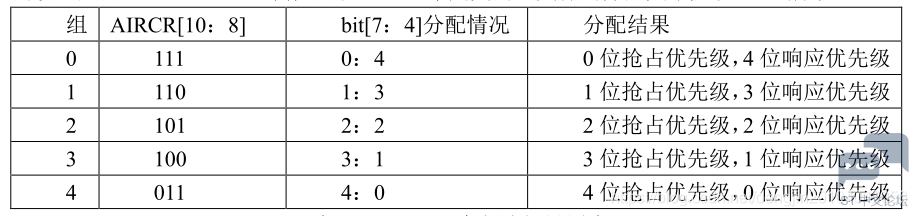

STM32F4 将中断分为 5 个组,组 0~4。该分组的设置是由 SCB->AIRCR 寄存器的 bit10~8 来定义的。

我们就可以清楚的看到组 0~4 对应的配置关系,例如组设置为 3,那么此时所有的 82 个中断,每个中断的中断优先寄存器的高四位中的最高 3 位是抢占优先级,低 1 位是响应优先级。每个中断,你可以设置抢占优先级为 0~7,响应优先级为 1 或 0。抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。

这里需要注意两点:第一,如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行;第二,高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的。而抢占优先级相同的中断,高优先级的响应优先级不可以打断低响应优先级的中断。

结合实例说明一下:假定设置中断优先级组为 2,然后设置中断 3(RTC_WKUP 中断)的抢占优先级为 2,响应优先级为 1。中断 6(外部中断 0)的抢占优先级为 3,响应优先级为 0。中断 7(外部中断 1)的抢占优先级为 2,响应优先级为 0。那么这 3 个中断的优先级顺序为:中断 7>中断 3>中断 6。

上面例子中的中断 3 和中断 7 都可以打断中断 6 的中断。而中断 7 和中断 3 却不可以相互打断!

04. 相关类型

misc.h文件

NVIC_InitTypeDef类型

- /**

- * @brief NVIC Init Structure definition

- */

- typedef struct

- {

- uint8_t NVIC_IRQChannel; /*!< Specifies the IRQ channel to be enabled or disabled.

- This parameter can be an enumerator of @ref IRQn_Type

- enumeration (For the complete STM32 Devices IRQ Channels

- list, please refer to stm32f4xx.h file) */

- uint8_t NVIC_IRQChannelPreemptionPriority; /*!< Specifies the pre-emption priority for the IRQ channel

- specified in NVIC_IRQChannel. This parameter can be a value

- between 0 and 15 as described in the table @ref MISC_NVIC_Priority_Table

- A lower priority value indicates a higher priority */

- uint8_t NVIC_IRQChannelSubPriority; /*!< Specifies the subpriority level for the IRQ channel specified

- in NVIC_IRQChannel. This parameter can be a value

- between 0 and 15 as described in the table @ref MISC_NVIC_Priority_Table

- A lower priority value indicates a higher priority */

- FunctionalState NVIC_IRQChannelCmd; /*!< Specifies whether the IRQ channel defined in NVIC_IRQChannel

- will be enabled or disabled.

- This parameter can be set either to ENABLE or DISABLE */

- } NVIC_InitTypeDef;

MISC_Vector_Table_Base- /** @defgroup MISC_Vector_Table_Base

- * @{

- */

- #define NVIC_VectTab_RAM ((uint32_t)0x20000000)

- #define NVIC_VectTab_FLASH ((uint32_t)0x08000000)

- #define IS_NVIC_VECTTAB(VECTTAB) (((VECTTAB) == NVIC_VectTab_RAM) || \

- ((VECTTAB) == NVIC_VectTab_FLASH))

MISC_System_Low_Power

- /** @defgroup MISC_System_Low_Power

- * @{

- */

- #define NVIC_LP_SEVONPEND ((uint8_t)0x10)

- #define NVIC_LP_SLEEPDEEP ((uint8_t)0x04)

- #define NVIC_LP_SLEEPONEXIT ((uint8_t)0x02)

- #define IS_NVIC_LP(LP) (((LP) == NVIC_LP_SEVONPEND) || \

- ((LP) == NVIC_LP_SLEEPDEEP) || \

- ((LP) == NVIC_LP_SLEEPONEXIT))

MISC_Preemption_Priority_Group

- /** @defgroup MISC_Preemption_Priority_Group

- * @{

- */

- #define NVIC_PriorityGroup_0 ((uint32_t)0x700) /*!< 0 bits for pre-emption priority

- 4 bits for subpriority */

- #define NVIC_PriorityGroup_1 ((uint32_t)0x600) /*!< 1 bits for pre-emption priority

- 3 bits for subpriority */

- #define NVIC_PriorityGroup_2 ((uint32_t)0x500) /*!< 2 bits for pre-emption priority

- 2 bits for subpriority */

- #define NVIC_PriorityGroup_3 ((uint32_t)0x400) /*!< 3 bits for pre-emption priority

- 1 bits for subpriority */

- #define NVIC_PriorityGroup_4 ((uint32_t)0x300) /*!< 4 bits for pre-emption priority

- 0 bits for subpriority */

- #define IS_NVIC_PRIORITY_GROUP(GROUP) (((GROUP) == NVIC_PriorityGroup_0) || \

- ((GROUP) == NVIC_PriorityGroup_1) || \

- ((GROUP) == NVIC_PriorityGroup_2) || \

- ((GROUP) == NVIC_PriorityGroup_3) || \

- ((GROUP) == NVIC_PriorityGroup_4))

- #define IS_NVIC_PREEMPTION_PRIORITY(PRIORITY) ((PRIORITY) < 0x10)

- #define IS_NVIC_SUB_PRIORITY(PRIORITY) ((PRIORITY) < 0x10)

- #define IS_NVIC_OFFSET(OFFSET) ((OFFSET) < 0x000FFFFF)

MISC_SysTick_clock_sourc

- /** @defgroup MISC_SysTick_clock_source

- * @{

- */

- #define SysTick_CLKSource_HCLK_Div8 ((uint32_t)0xFFFFFFFB)

- #define SysTick_CLKSource_HCLK ((uint32_t)0x00000004)

- #define IS_SYSTICK_CLK_SOURCE(SOURCE) (((SOURCE) == SysTick_CLKSource_HCLK) || \

- ((SOURCE) == SysTick_CLKSource_HCLK_Div8))

中断名字(stm32f4xx.h)

- /**

- * @brief STM32F4XX Interrupt Number Definition, according to the selected device

- * in @ref Library_configuration_section

- */

- typedef enum IRQn

- {

- /****** Cortex-M4 Processor Exceptions Numbers ****************************************************************/

- NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */

- MemoryManagement_IRQn = -12, /*!< 4 Cortex-M4 Memory Management Interrupt */

- BusFault_IRQn = -11, /*!< 5 Cortex-M4 Bus Fault Interrupt */

- UsageFault_IRQn = -10, /*!< 6 Cortex-M4 Usage Fault Interrupt */

- SVCall_IRQn = -5, /*!< 11 Cortex-M4 SV Call Interrupt */

- DebugMonitor_IRQn = -4, /*!< 12 Cortex-M4 Debug Monitor Interrupt */

- PendSV_IRQn = -2, /*!< 14 Cortex-M4 Pend SV Interrupt */

- SysTick_IRQn = -1, /*!< 15 Cortex-M4 System Tick Interrupt */

- /****** STM32 specific Interrupt Numbers **********************************************************************/

- WWDG_IRQn = 0, /*!< Window WatchDog Interrupt */

- PVD_IRQn = 1, /*!< PVD through EXTI Line detection Interrupt */

- TAMP_STAMP_IRQn = 2, /*!< Tamper and TimeStamp interrupts through the EXTI line */

- RTC_WKUP_IRQn = 3, /*!< RTC Wakeup interrupt through the EXTI line */

- FLASH_IRQn = 4, /*!< FLASH global Interrupt */

- RCC_IRQn = 5, /*!< RCC global Interrupt */

- EXTI0_IRQn = 6, /*!< EXTI Line0 Interrupt */

- EXTI1_IRQn = 7, /*!< EXTI Line1 Interrupt */

- EXTI2_IRQn = 8, /*!< EXTI Line2 Interrupt */

- EXTI3_IRQn = 9, /*!< EXTI Line3 Interrupt */

- EXTI4_IRQn = 10, /*!< EXTI Line4 Interrupt */

- DMA1_Stream0_IRQn = 11, /*!< DMA1 Stream 0 global Interrupt */

- DMA1_Stream1_IRQn = 12, /*!< DMA1 Stream 1 global Interrupt */

- DMA1_Stream2_IRQn = 13, /*!< DMA1 Stream 2 global Interrupt */

- DMA1_Stream3_IRQn = 14, /*!< DMA1 Stream 3 global Interrupt */

- DMA1_Stream4_IRQn = 15, /*!< DMA1 Stream 4 global Interrupt */

- DMA1_Stream5_IRQn = 16, /*!< DMA1 Stream 5 global Interrupt */

- DMA1_Stream6_IRQn = 17, /*!< DMA1 Stream 6 global Interrupt */

- ADC_IRQn = 18, /*!< ADC1, ADC2 and ADC3 global Interrupts */

- #if defined(STM32F40_41xxx)

- CAN1_TX_IRQn = 19, /*!< CAN1 TX Interrupt */

- CAN1_RX0_IRQn = 20, /*!< CAN1 RX0 Interrupt */

- CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

- CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

- EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

- TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break interrupt and TIM9 global interrupt */

- TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global interrupt */

- TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

- TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

- TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

- TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

- TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

- I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

- I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

- I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

- I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

- SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

- SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

- USART1_IRQn = 37, /*!< USART1 global Interrupt */

- USART2_IRQn = 38, /*!< USART2 global Interrupt */

- USART3_IRQn = 39, /*!< USART3 global Interrupt */

- EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

- RTC_Alarm_IRQn = 41, /*!< RTC Alarm (A and B) through EXTI Line Interrupt */

- OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS Wakeup through EXTI line interrupt */

- TIM8_BRK_TIM12_IRQn = 43, /*!< TIM8 Break Interrupt and TIM12 global interrupt */

- TIM8_UP_TIM13_IRQn = 44, /*!< TIM8 Update Interrupt and TIM13 global interrupt */

- TIM8_TRG_COM_TIM14_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */

- TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */

- DMA1_Stream7_IRQn = 47, /*!< DMA1 Stream7 Interrupt */

- FSMC_IRQn = 48, /*!< FSMC global Interrupt */

- SDIO_IRQn = 49, /*!< SDIO global Interrupt */

- TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

- SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

- UART4_IRQn = 52, /*!< UART4 global Interrupt */

- UART5_IRQn = 53, /*!< UART5 global Interrupt */

- TIM6_DAC_IRQn = 54, /*!< TIM6 global and DAC1&2 underrun error interrupts */

- TIM7_IRQn = 55, /*!< TIM7 global interrupt */

- DMA2_Stream0_IRQn = 56, /*!< DMA2 Stream 0 global Interrupt */

- DMA2_Stream1_IRQn = 57, /*!< DMA2 Stream 1 global Interrupt */

- DMA2_Stream2_IRQn = 58, /*!< DMA2 Stream 2 global Interrupt */

- DMA2_Stream3_IRQn = 59, /*!< DMA2 Stream 3 global Interrupt */

- DMA2_Stream4_IRQn = 60, /*!< DMA2 Stream 4 global Interrupt */

- ETH_IRQn = 61, /*!< Ethernet global Interrupt */

- ETH_WKUP_IRQn = 62, /*!< Ethernet Wakeup through EXTI line Interrupt */

- CAN2_TX_IRQn = 63, /*!< CAN2 TX Interrupt */

- CAN2_RX0_IRQn = 64, /*!< CAN2 RX0 Interrupt */

- CAN2_RX1_IRQn = 65, /*!< CAN2 RX1 Interrupt */

- CAN2_SCE_IRQn = 66, /*!< CAN2 SCE Interrupt */

- OTG_FS_IRQn = 67, /*!< USB OTG FS global Interrupt */

- DMA2_Stream5_IRQn = 68, /*!< DMA2 Stream 5 global interrupt */

- DMA2_Stream6_IRQn = 69, /*!< DMA2 Stream 6 global interrupt */

- DMA2_Stream7_IRQn = 70, /*!< DMA2 Stream 7 global interrupt */

- USART6_IRQn = 71, /*!< USART6 global interrupt */

- I2C3_EV_IRQn = 72, /*!< I2C3 event interrupt */

- I2C3_ER_IRQn = 73, /*!< I2C3 error interrupt */

- OTG_HS_EP1_OUT_IRQn = 74, /*!< USB OTG HS End Point 1 Out global interrupt */

- OTG_HS_EP1_IN_IRQn = 75, /*!< USB OTG HS End Point 1 In global interrupt */

- OTG_HS_WKUP_IRQn = 76, /*!< USB OTG HS Wakeup through EXTI interrupt */

- OTG_HS_IRQn = 77, /*!< USB OTG HS global interrupt */

- DCMI_IRQn = 78, /*!< DCMI global interrupt */

- CRYP_IRQn = 79, /*!< CRYP crypto global interrupt */

- HASH_RNG_IRQn = 80, /*!< Hash and Rng global interrupt */

- FPU_IRQn = 81 /*!< FPU global interrupt */

- #endif /* STM32F40_41xxx */

05. 相关函数

- /* Exported macro ------------------------------------------------------------*/

- /* Exported functions --------------------------------------------------------*/

- void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup);

- void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct);

- void NVIC_SetVectorTable(uint32_t NVIC_VectTab, uint32_t Offset);

- void NVIC_SystemLPConfig(uint8_t LowPowerMode, FunctionalState NewState);

- void SysTick_CLKSourceConfig(uint32_t SysTick_CLKSource);

|

.png) STMCU小助手

发布时间:2022-4-1 15:20

STMCU小助手

发布时间:2022-4-1 15:20

微信公众号

微信公众号

手机版

手机版