.png) STMCU小助手

发布时间:2022-4-18 09:37

STMCU小助手

发布时间:2022-4-18 09:37

|

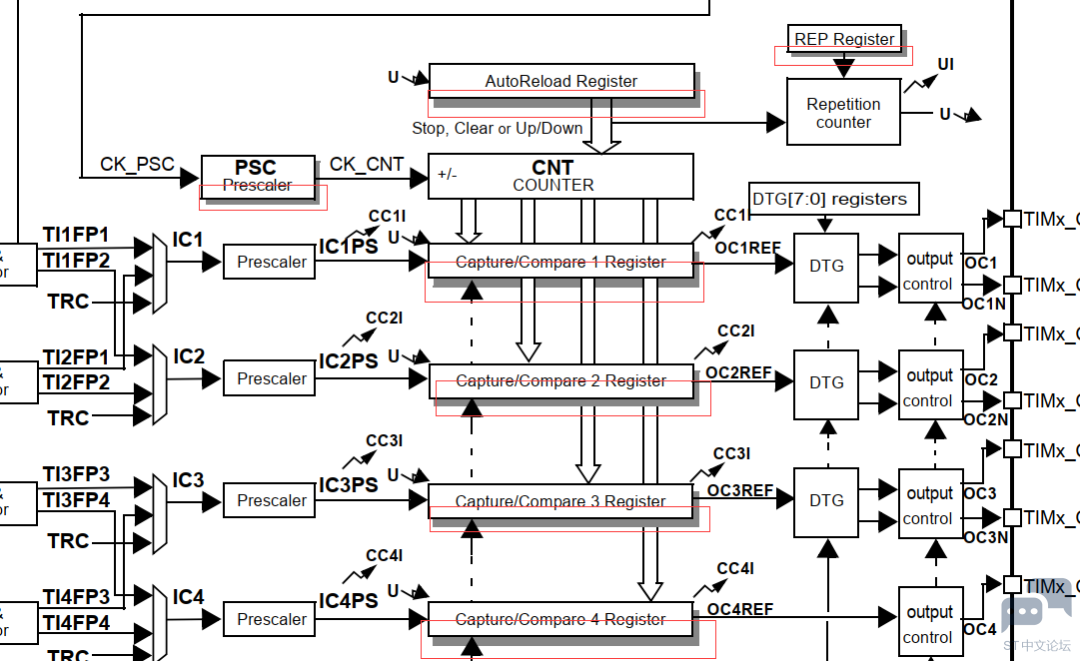

01、概述 在定时器框图中,有个小细节,有些寄存器下有个阴影

有这些阴影的表示这些寄存器存在影子寄存器。 在图例中也有对影子寄存器的说明:

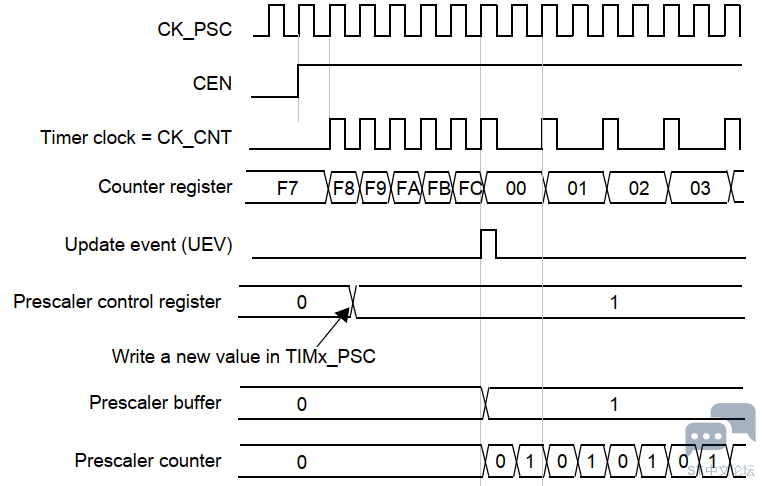

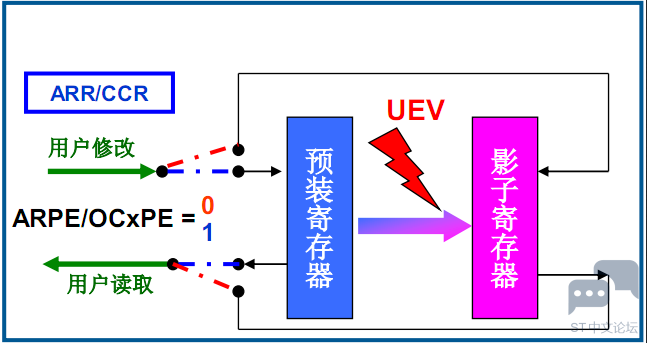

根据控制位,在发生U事件后,预装载寄存器内容转移到有效寄存器。这也就是对影子寄存器的说明。 有阴影的寄存器(AutoReloadRegister),表示在物理上这个寄存器对应2个寄存器,一个是程序员可以写入或读出的寄存器,称为preloadregister(预装载寄存器),另一个是程序员看不见的、但在操作中真正起作用的寄存器,称为shadowregister(影子寄存器)。 这里有3个寄存器名称 AutoReloadRegister。 preloadregister。 shadowregister。 在这里我的理解是,AutoReloadRegister自动重装载寄存器是一个概念寄存器,可以在寄存器表中找到每一位的定义,它是由preloadregister预装载寄存器和shadowregister影子寄存器组成。我们用户能接触到,能修改或读取的都是预装载寄存器,ST只是把它们开放出来(影子寄存器并没有开放给用户),其实就是ARR寄存器。 设计preloadregister和shadowregister的好处是: 所有真正需要起作用的寄存器(shadowregister)可以在同一个时间(发生更新事件时)被更新为所对应的preloadregister的内容,这样可以保证多个通道的操作能够准确地同步。如果没有shadowregister,或者preloadregister和shadowregister是直通的,即软件更新preloadregister时,同时更新了shadowregister,因为软件不可能在一个相同的时刻同时更新多个寄存器,结果造成多个通道的时序不能同步,如果再加上其它因素(例如中断),多个通道的时序关系有可能是不可预知的。 看到有阴影寄存器共三种: 1、PSC(Prescaler) 2、ARR(AutoReloadRegister) 3、CCR(Capture/Comparex Register) 4、REPRegister 02、PSC(Prescaler) 在预分频器的描述中: It is based on a 16-bit counter controlled through a 16-bit register(in the TIMx_PSC register).It can be changed on the fly as thiscontrol register is buffered. The new prescaler ratio is taken intoaccount at the next update event. 节选自STM32F207 Reference manual手册 由于该控制寄存器具有缓冲功能,因此可对预分频器进行实时更改。而新的预分频比将在下一更新事件发生时被采用。 预分频器分频由1 变为2 时的计数器时序图

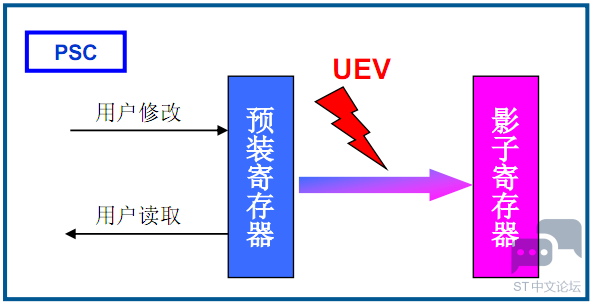

在这里看到预分频器寄存器存在影子寄存器,但是没有控制位控制它,它的预装载寄存器和影子寄存器是相连的。 工作模式如下图:

注意: 在ST的手册中,影子寄存器被描述成缓冲,在对预分频器的影子寄存器描述成寄存器具有缓冲功能。其中

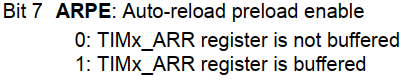

在这里又被描述成TIMx_ARR寄存器不进行缓冲。 03、ARR(AutoReloadRegister) 控制位: 在时基单位中有说明如下 The content of the preload register are transferred into theshadowregister permanently or at each update event (UEV), depending on theauto-reloadpreload enable bit (ARPE) in TIMx_CR1 register. 节选自STM32F207 Reference manual手册 预装载寄存器的内容既可以直接传送到影子寄存器,也可以在每次发生更新事件(UEV)时传送到影子寄存器,这取决于TIMx_CR1 寄存器中的自动重载预装载使能位(ARPE)。 也就是TIMx_CR1的ARPE位决定了预装寄存器数据传入影子寄存器的时间先后顺序。 计数器时序图,ARPE=0 时更新事件(TIMx_ARR 未预装载)。

从上面两图看出,向上计数,还没有到达0x36,就把自动重载寄存器修改为0x36,就会在计数到0x36时产生动作。 计数器时序图,ARPE=1 时更新事件(TIMx_ARR 预装载)。

从上面两图看出,向上计数,还没有到达0x36,就把自动重载预装载寄存器修改为0x36,就不会在计数到0x36时产生动作,会在这个时将自动重载预装载寄存器值赋给自动重载影子寄存器。 从预装载寄存器ARR传送到影子寄存器,有两种方式,一种是立刻更新,一种是等触发事件之后更新;这两种方式主要取决于寄存器TIMx->CR1中的“ARPE”位; ARPE=0,当ARR值被修改时,同时马上更新影子寄存器的值; ARPE=1,当ARR值被修改时,必须在下一次事件UEV发生后才能更新影子寄存器的值; 怎么样马上立刻更改影子寄存器的值,而不是下一个事件;方法如下 1、将ARPE=0。

2、在ARPE=1。

我们更改完预装载寄存器后,立刻设置UEV事件,即更改EGR寄存的UG位,如下

工作模式如下图:

04、CCR(Capture/Comparex Register) 还有计数器模式中有文字说明: The UEV event can be disabled by software by setting the UDIS bit inthe TIMx_CR1 register. This is to avoid updating the shadow registerswhile writing new values in the preload registers。 节选自STM32F207 Reference manual手册 通过软件将TIMx_CR1寄存器中的UDIS位置1可禁止更新事件UEV事件。这可避免向预装载寄存器写入新值时更新影子寄存器。 也就是TIMx_CR1寄存器中UDIS位间接决定了预装寄存器数据是否传入影子寄存器。 |

实战经验 | Keil工程使用NEAI库的异常问题

经验分享 | FDCAN数据段波特率增加后发送失败的问题分析

STM32几种流行开发环境的优缺点

好用软件推荐-TouchGFX Designer

OpenSTLinux 6.1发布:M33-TD加持+安全升级,STM32MPU开发效率翻倍!

【经验分享】STM32CubeIDE汉化

手把手教你VSCode搭建STM32开发环境

RTOS在STM32中的应用

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

微信公众号

微信公众号

手机版

手机版